Sigma-Delta ADC Matlab Model 包含实例和说明,多种MATLAB代码...

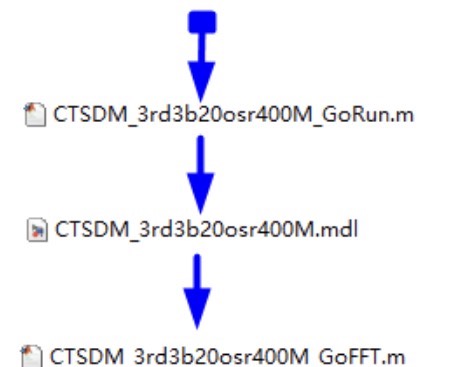

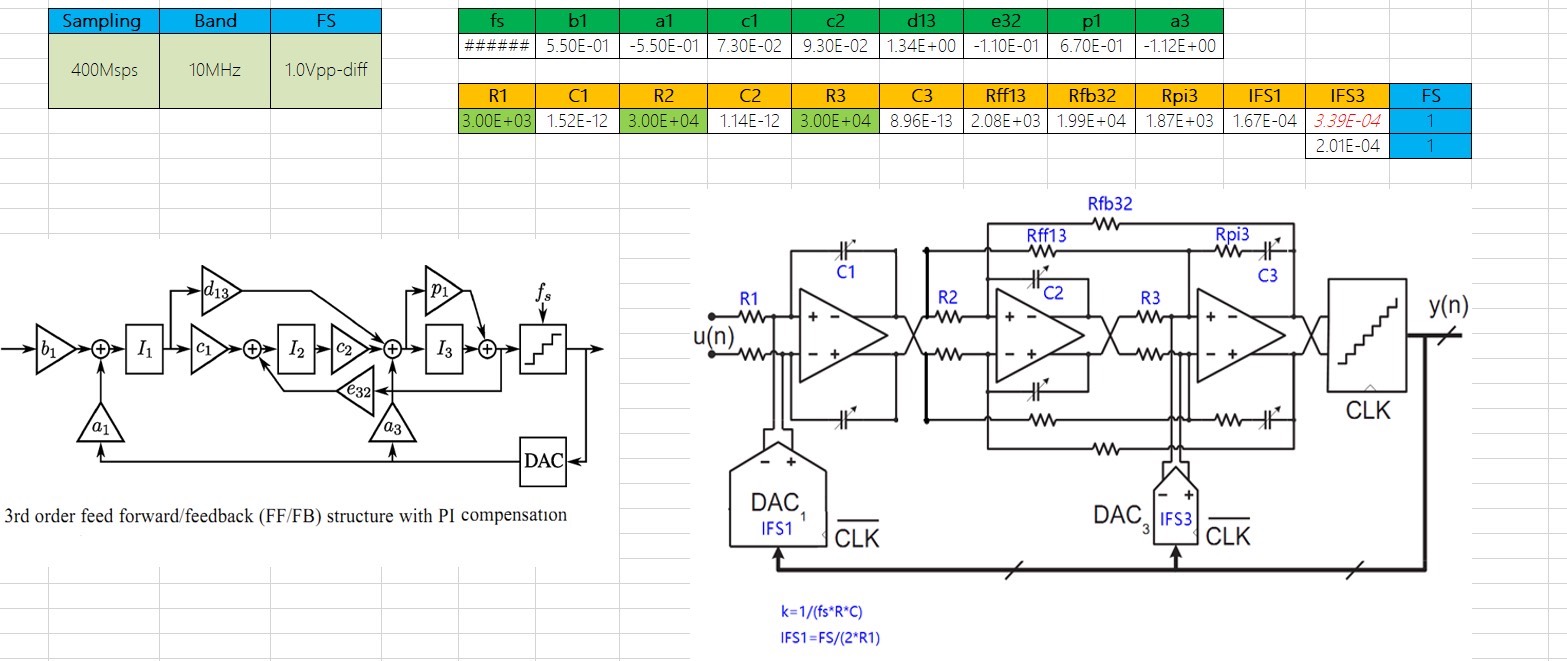

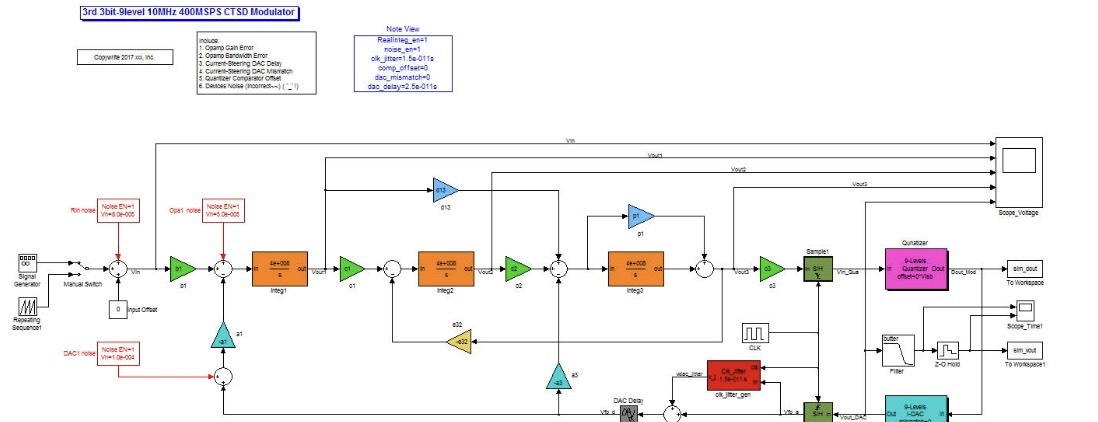

Sigma-Delta ADC Matlab Model 包含实例和说明,多种MATLAB代码和simulink模型都整合在里面了。 包含一个3rd 3bit-9level 10MHz 400MSPS CTSD Modulator Matlab Simulink Model 模拟ic设计,adc建模 ADC的动态fft,静态特性inl、dnl仿真 教程,动态静态参数分析。 东西很多,就不一一介绍了。 打开有惊喜 Continuous-Time Sigma-Delta ADC Matlab Model,有的地方也不是特别严谨,不过可以方便入门学习。 这是一个3rd 3bit-9level 10MHz 400MSPS CTSD Modulator Matlab Simulink Model,包含: 1. CTSDM_3rd3b20osr400M.mdl 2. CTSDM_3rd3b20osr400M_GoRun.m 3. CTSDM_3rd3b20osr400M_GoFFT.m 4. SDM_Dynamic_GoTest.m 5. CTSDM_3rd3b20osr400M_Calculate.xlsx 6. 参考文献 (注: 其中一篇参考论文的电路连接图画的不太正确,xlsx里更新了下) (注:这个是计算好的调制器系数后,用这个model来进行时域仿真验证的,所以调制器系数大家可以自行求解。 )。 所有的参数都直接在.m程序中进行修改,具体参见程序内详,操作步骤如下

Sigma-Delta ADC Matlab 模型全景解读

——从行为级到电路级的 160 文件一站式开发框架

- 引言

在精密信号链、音频 SOC 与计量芯片中,Sigma-Delta ADC 以其天然的高分辨率、低模拟复杂度与数字可编程性,成为“高性能 + 低成本”首选架构。然而其设计横跨离散时间系统、连续时间噪声整形、非理想电路效应三大维度,传统“原理图→SPICE→手算”流程周期长、收敛慢。本文介绍的 Matlab/Simulink 开源工程包,通过 160 个高度解耦的脚本/模型,把系统级行为建模、RTL 级数字滤波、电路级非理想因素、乃至射频前端阻抗匹配,全部纳入一条“可执行规范”链路,实现算法→电路→验证的垂直整合。

- 整体架构

2.1 目录分层

ADC_理想 DAC 恢复/ – 验证核心调制器与理想重建

AllTypeADC_Model/ – 行为级比较(SAR、Pipeline、Flash、SD)

AnalogBlockMatlab_Model/ – 运放、开关、电阻、电容、LC 滤波、PLL 相位噪声

电路级/ – 被动网络综合(Bessel、Elliptic)、S 参数后处理

adc/ – 针对 SD-ADC 的专用绘图与量化函数

pll/ – 时钟抖动、相位噪声建模

lc_passive/ – 无源椭圆/切比雪夫综合 GUI

RFblockset/ – 射频链路(匹配、LNA、滤波器)协同仿真

2.2 数据流抽象

① 系统指标输入(ENOB、BW、Power、Area)

② 调制器阶数/位数/过采样率自动权衡(NTF 零极点优化)

③ 数字抽取滤波器自动生成长度与系数(CIC-HB-FIR 级联)

④ 电路非理想映射(kT/C 噪声、运放 GBW、开关电阻、时钟抖动)

⑤ 返回有效位数、功耗、面积、稳定性量化结果

⑥ 一键生成可综合 RTL(Verilog)与电路级网表(SPICE)

- 核心模块深度拆解

3.1 行为级 Sigma-Delta 调制器

- 基于 ds modulator 的 NTF 零极点优化,支持 1~6 阶、1~5 bit 量化器

- 内置抖动、量化器迟滞、积分器饱和等非线性;支持实数/复数信号路径

- 关键脚本:

sdmod2.m —— 离散时间模型

sdmodCT.m —— 连续时间模型(支持 RZ/NRZ/HRZ 脉冲)

sd_map2circuit.m —— 系数→RC/SC 网络映射

3.2 数字抽取滤波器

- CIC 级联半带 FIR 自动分段:CIC 阶数与差分延迟由带内纹波、带外抑制联合优化

- HB-FIR 采用 Parks-McClellan 或 Remez,支持系数 CSD 编码,可直接输出 Verilog

- 关键脚本:

ciccompensator.m

hbfir_auto.m

fir2csd.m —— 系数转 CSD,降低乘法器为移位-加法

3.3 电路级非理想模型

- 开关电容 kT/C 噪声:在时域注入高斯随机序列,功率谱与 1/C 成正比

- 运放宏模型:增益/GBW/PM/SR 四参数表,支持压摆率限幅与时域可变增益

- 时钟抖动:采用 1/f 滤波器(noiseinvf.m)产生相关随机序列,叠加到采样沿

- 关键脚本:

opampmacro.m

switchresistor.m

jitter_gen.m

3.4 无源网络综合

- qsynth.m 提供 GUI:输入带通/带阻、阶数、纹波、抑制,一键生成 L/C 值

- 支持单端/差分、源端匹配/负载端匹配两种拓扑;内部调用 ellip() 后做综合与验证

- 关键脚本:

qsynth.m(GUI)

pabcd.m —— ABCD 参数级联,用于快速验证插入损耗

3.5 射频链路协同

- 采用 RF Blockset 的 rfckt 对象,把 LC 滤波器、匹配网络、封装寄生、PCB 走线模型化

- 支持 S 参数实时回传至 Simulink,直接叠加到 ADC 行为模型,评估阻塞、交调、相噪折叠

- 关键脚本:

rabfilter.m —— 10 级 LC 梯形示例

rfnaplot.m —— Smith 圆图/极坐标交互显示

- 典型设计流程示例

Step1 系统指标

BW = 24 kHz, ENOB ≥ 20 bit, Power ≤ 1 mW, 1.8 V 供电

Step2 快速权衡

运行 >> sd_tradeoff('ENOB',20,'BW',24e3,'Power',1e-3)

Sigma-Delta ADC Matlab Model 包含实例和说明,多种MATLAB代码和simulink模型都整合在里面了。 包含一个3rd 3bit-9level 10MHz 400MSPS CTSD Modulator Matlab Simulink Model 模拟ic设计,adc建模 ADC的动态fft,静态特性inl、dnl仿真 教程,动态静态参数分析。 东西很多,就不一一介绍了。 打开有惊喜 Continuous-Time Sigma-Delta ADC Matlab Model,有的地方也不是特别严谨,不过可以方便入门学习。 这是一个3rd 3bit-9level 10MHz 400MSPS CTSD Modulator Matlab Simulink Model,包含: 1. CTSDM_3rd3b20osr400M.mdl 2. CTSDM_3rd3b20osr400M_GoRun.m 3. CTSDM_3rd3b20osr400M_GoFFT.m 4. SDM_Dynamic_GoTest.m 5. CTSDM_3rd3b20osr400M_Calculate.xlsx 6. 参考文献 (注: 其中一篇参考论文的电路连接图画的不太正确,xlsx里更新了下) (注:这个是计算好的调制器系数后,用这个model来进行时域仿真验证的,所以调制器系数大家可以自行求解。 )。 所有的参数都直接在.m程序中进行修改,具体参见程序内详,操作步骤如下

返回:2-2 MASH、OSR = 128、1-bit 量化、功耗 0.85 mW

Step3 行为验证

sim('sdmash22.slx')

SNDR = 124 dB,符合目标

Step4 电路映射

>> sdmap2circuit('mod','mash22','type','SC','process','65nm')

自动生成:

- 积分电容值(kT/C 噪声约束)

- 运放 GBW ≥ 3.5 × Fs,DC Gain ≥ 60 dB

- 开关电阻 ≤ 50 Ω(带宽约束)

Step5 数字滤波器

>> cichbfir_gen('OSR',128,'BW',24e3,'ripple',0.001,'atten',120)

返回:

CIC:5 阶,差分延迟 1

HB1:31 阶,HB2:59 阶,FIR:123 阶

整体衰减 120 dB,通带纹波 0.001 dB

一键输出:verilog/sd_decimator.v

Step6 协同仿真

将生成的 SPICE 网表与 Verilog 同时代入 Virtuoso + ModelSim 混合平台,运行 65536 点 FFT,SNDR 122.8 dB,与行为级误差 < 2 dB,满足设计余量。

- 关键可视化与调试

- plot_signal.m:同时显示模拟波形、数字码流、步长自适应曲线,快速定位饱和/振荡

- rfna_plot.m:交互式 Smith 圆图,支持鼠标读取阻抗、VSWR、稳定性圆

- sdspfscope2_r13.m:频域示波器,支持在线 FFT、自动 ENOB/SNDR 计算,可替代昂贵硬件分析仪

- 扩展场景

6.1 多通道 TI-SDM

通过 time-interleaved 子模型,自动注入通道失配(增益、失调、时间偏斜),评估 SFDR 劣化;内置校准引擎(数字后矫正)。

6.2 射频 ADC

将射频前端与 SD-ADC 合并为单模块,支持阻塞/交调/相噪折叠联合预算,适用于射频采样或低中频接收机。

6.3 数字 PLL 闭环

集成相位噪声模型,可评估时钟抖动对 SNDR 的灵敏度,输出闭环传递函数,指导 VCO/环路滤波器设计。

- 小结

本工程包以“可执行规范”为核心,打通算法→电路→验证全链路,把 Sigma-Delta ADC 设计从“经验 + 试错”转变为“脚本 + 量化”。开发者可在数小时内完成 20 bit 级 ADC 的系统级定案,并在同一框架内持续细化到晶体管级,实现真正的 top-down / bottom-up 双向收敛。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献21条内容

已为社区贡献21条内容

所有评论(0)