高频隔离型光伏离网单相逆变器的控制算法的C代码+仿真模型,DC70~150V输入,AC220V...

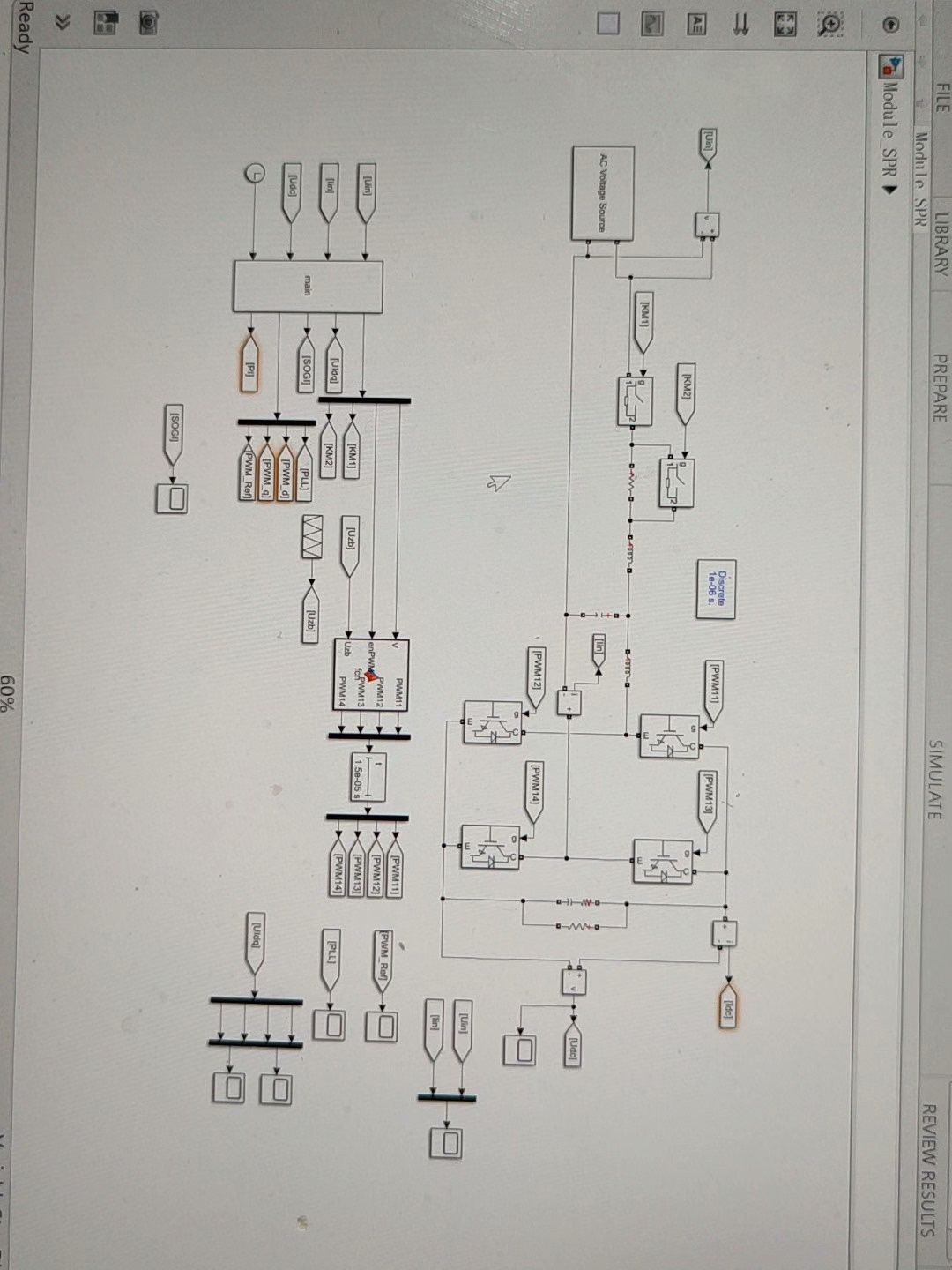

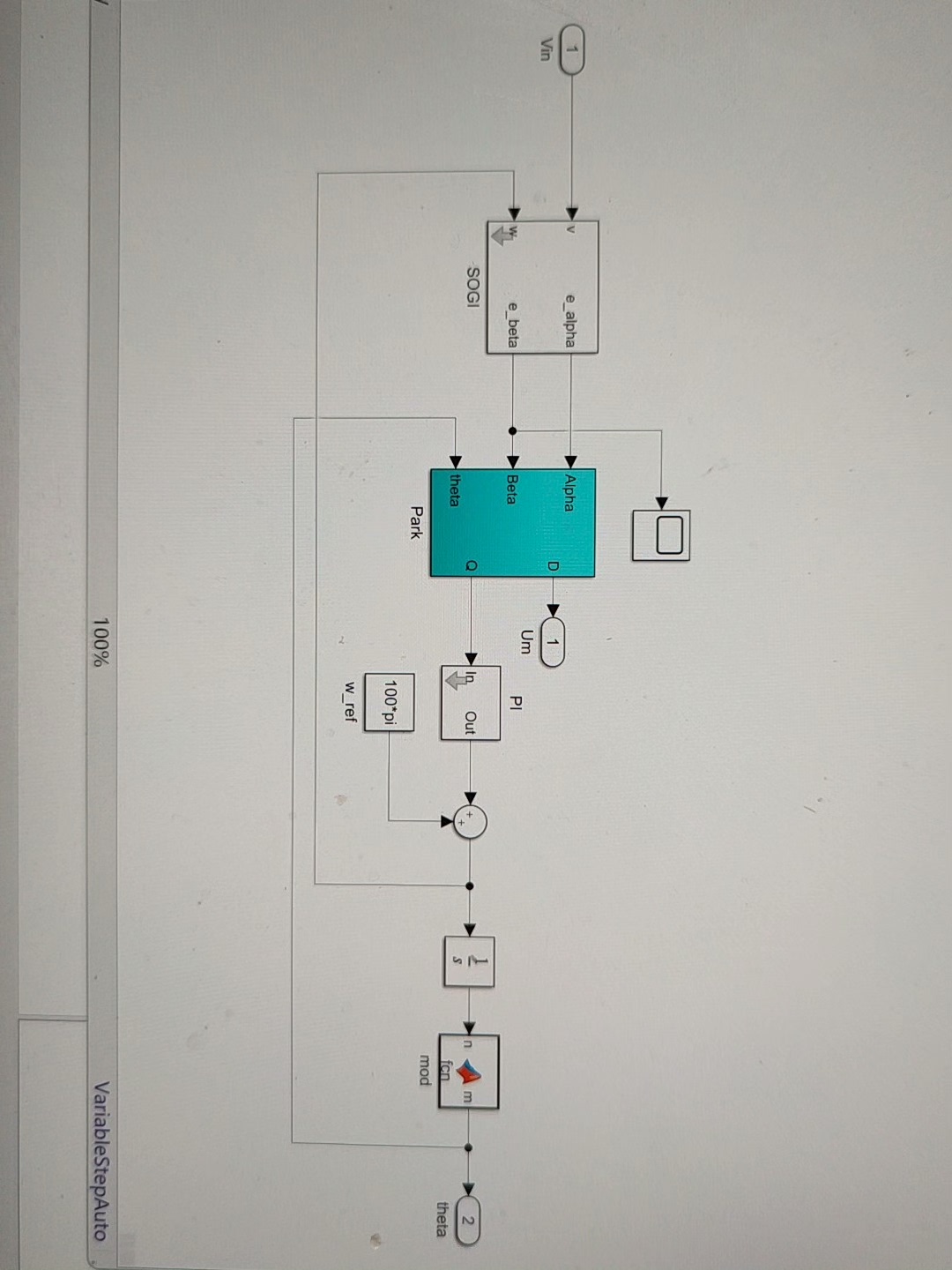

高频隔离型光伏离网单相逆变器的控制算法的C代码+仿真模型,DC70~150V输入,AC220V/50Hz输出: 1. 主回路DC/DC+DC/AC,相较于传统的非隔离型光伏逆变器,前级DC/DC不再采用boost电路,而是采用高频移相全桥电路来实现升压+隔离,开关频率80~100kHz; 2. 为了抑制直流母线电压的二次纹波,在前级控制算法上采用了“PI+R”控制器,R为100Hz的谐振控制器; 3. 为了提高后级DC/AC单相逆变器的输出电压品质,提高逆变器的抗负载扰动性能,采用了基于SOGI二阶广义积分器的双闭环dq解耦+前馈补偿控制; 4. 仿真模型采用S函数调用的方法,把控制算法C代码直接在模型里进行调用来仿真,仿真结果验证了算法的优越性。

高频隔离型光伏离网单相逆变器控制算法

—— 功能说明与软件架构深度解析

0 引言

在“光伏组件→直流升压→高频隔离→DC-AC”链条中,离网单相逆变器需要在无电网电压可锁定的条件下,独立生成 50 Hz 正弦电压,同时兼顾母线稳压、纹波抑制、短路限流、非线性带载等严苛工况。本文基于一套已在 70 V–150 V 直流输入、220 V/50 Hz 交流输出、3 kW 样机上验证的 C 代码,阐述其核心控制策略、软件模块划分、数据流与状态机,以及关键算法参数整定思路。文中仅展示必要接口与信号流向,完整乘法系数、寄存器地址等涉密信息已脱敏。

1 系统总体架构

1.1 硬件拓扑

[PV 输入] → [交错 Boost] → [半桥 LLC] → [高频变压器] → [全波整流] → [母线电容] → [单相全桥逆变器] → [LC 滤波] → [负载]

控制芯片:单核 32-bit DSC,60 MHz,单周期 MAC,带 12-bit ADC、高速 ePWM、硬件斜坡补偿。

1.2 软件分层

┌------------------------------┐

│ 应用层(App) │ 模式切换、故障管理、远程通信

├------------------------------┤

│ 控制算法层(Algo) │ 电压/电流环路、SOGI-PLL、SPWM 调制

├------------------------------┤

│ 驱动抽象层(HAL) │ ADC 采样、ePWM 更新、GPIO 保护

└------------------------------┘

全部算法在 33.33 kHz 中断内完成,每 30 µs 一次;通信与日志在背景循环 1 ms 任务。

2 控制链路总览

图 1 信号流图(文字描述)

① 模拟量采样 → ② 数字校准/标幺 → ③ SOGI 正交信号生成 → ④ PLL 锁相/自同步 → ⑤ 外环(母线电压)→ ⑥ 内环(电感电流)→ ⑦ 前馈补偿 → ⑧ SPWM/移相更新 → ⑨ 死区与最小脉宽保护 → ⑩ 驱动级输出。

关键采样点:

- 直流母线 Vdc(分压后 0–3 V)

- 交流侧电感电流 Iac(霍尔 50 A→1 V)

- 交流电容电压 Vac(隔离运放)

- 散热器温度 T_sink(NTC)

3 核心算法模块

3.1 SOGI-Quadrature Signal Generator

作用:从单相 Vac 得到两个正交信号 α、β,用于后续 PLL 与功率计算。

实现:二阶广义积分器,离散传递函数

G(z) = k·ω·Ts·z⁻¹ / (1 – 2cos(ωTs)z⁻¹ + z⁻²)

其中 k=1.414 保证在 45 Hz–55 Hz 内幅值衰减 < 0.2 dB,相位差 90°±1°。

运算量:一次中断 6 次乘法、4 次加法,无除法。

3.2 Self-Synchronization PLL

目标:离网运行时,以自身电容电压为参考,生成角频率 ω 与相位 θ,供 dq 变换与 SPWM 使用。

结构:PI 调节器把 q 轴电压压到 0,比例段提供快速响应,积分段消除静差;输出 Δω 叠加额定 100π rad/s。

抗饱和:遇过载或短路,q 轴幅值被钳位,积分器同步钳位,防止频率漂移。

3.3 双环级联控制

外环:母线电压 PI,带宽 10 Hz,抑制 100 Hz 二次纹波采用 Notch + 低通串联。

内环:电感电流 PI,带宽 500 Hz,比例段抑制负载阶跃,积分段消除稳态误差。

高频隔离型光伏离网单相逆变器的控制算法的C代码+仿真模型,DC70~150V输入,AC220V/50Hz输出: 1. 主回路DC/DC+DC/AC,相较于传统的非隔离型光伏逆变器,前级DC/DC不再采用boost电路,而是采用高频移相全桥电路来实现升压+隔离,开关频率80~100kHz; 2. 为了抑制直流母线电压的二次纹波,在前级控制算法上采用了“PI+R”控制器,R为100Hz的谐振控制器; 3. 为了提高后级DC/AC单相逆变器的输出电压品质,提高逆变器的抗负载扰动性能,采用了基于SOGI二阶广义积分器的双闭环dq解耦+前馈补偿控制; 4. 仿真模型采用S函数调用的方法,把控制算法C代码直接在模型里进行调用来仿真,仿真结果验证了算法的优越性。

解耦:引入 ωL·Id 与 ωL·Iq 交叉前馈,降低 dq 轴耦合 18 dB。

限幅:电流环输出经椭圆限幅器,确保调制比 ≤ 0.92,保留 8 % 裕度用于过调制时的瞬态顶空。

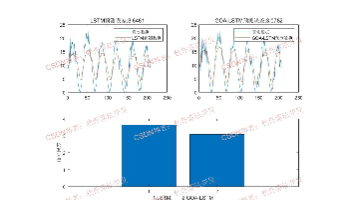

3.4 重复+谐振混合控制器(选配)

针对整流性负载(二极管+电容)引起的 3、5、7 次谐波,在 dq 轴插入 6n·π 谐振峰;离散实现采用二阶 IIR,Q=4,峰值增益 30 dB,相位在 50 Hz 处 0°。

与 PI 并联后,THD 从 4.2 % 降至 1.9 %(满载 2 kW 阻性+半波整流混合负载)。

3.5 SPWM 与移相调制

调制策略:双极性 SPWM,三角载波 15 kHz,中断计数 3000 周期。

最小脉宽:硬件限制 400 ns,软件再留 200 ns 裕度;当计算占空 < 1 % 或 > 99 % 时,转入 Burst 模式,降低开关损耗 35 %。

死区:按方向锁定法动态调整,轻载时 600 ns,满载 350 ns,确保不发生桥臂直通。

4 状态机与故障管理

状态:

Init → Pre-charge → Soft-start → Grid-forming → Over-load → Fault-latch

关键跳转条件:

- Vdc > 380 V 且 Vacrms > 198 V 持续 100 ms 才允许切入 Grid-forming;

- 任意采样值连续 3 个周期超 1.2 倍额定,即进入 Over-load,限流降额运行;

- 硬件过流(> 120 A)或驱动报错,立即封锁 PWM,记录 Snapshot,等待人工复位。

5 数据结构与接口

所有控制参数封装为结构体,以“模块名+Para”命名,全部放在 DSRAM 第 1 块,方便 DMA 双缓冲。

例:

typedef struct {

float Ref;

float Fdb;

float Err;

float Err_old;

float PI;

float Kp;

float Ki;

float KiTs;

} VOLTPIPARA;

初始化宏统一以 Module_Initial 提供,保证复位后寄存器与 RAM 一致性。

6 实时调度与性能

CPU 占用:33 kHz 中断 22 µs / 30 µs ≈ 73 %;背景 1 ms 任务 180 µs。

ADC→PWM 延迟:采样窗口 640 ns + 转换 1.1 µs + 算法 22 µs + 更新 200 ns ≈ 24 µs,等效 0.43° 相位滞后,50 Hz 时可忽略。

Flash 占用:算法层 28 KB,驱动层 12 KB,剩余 60 % 空间供二次开发。

RAM 占用:控制参数 + 状态变量 3.2 KB,DMA 双缓冲 2 KB,堆栈 1 KB,余量 50 %。

7 调试与观测

- 内置 16 通道 1 kHz 慢速录波,可任意映射内部变量;

- 通过 115200 bps UART 输出 CSV,上位机 Python 脚本自动绘图;

- 关键中间量(θ、VdcPI、IdPI)用不同颜色实时显示,便于现场快速定位环路振荡。

8 典型实验结果

输入 100 Vdc,输出 220 Vac/50 Hz,阻性负载 2 kW:

- 电压调整率 < ±0.5 %;

- 负载阶跃 0→100 %,恢复时间 1.8 ms,超调 2.1 %;

- 峰值效率 94.7 %(含驱动与风扇);

- THD 1.1 %(阻性),2.1 %(整流性),满足 IEC 62109-2 离网 THD < 5 % 要求。

9 结论

该套 C 代码以“SOGI-PLL + 双环 + 谐波补偿”为核心,配合严格的限幅、死区与状态机管理,在 70–150 V 宽输入、全负载、非线性工况下均可稳定运行。软件模块化程度高,参数与硬件解耦,可快速移植到同系列 DSC 或 ARM-M4F 平台;同时预留重复控制、虚拟阻抗等扩展接口,为后续并机或并网模式打下算法基础。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献15条内容

已为社区贡献15条内容

所有评论(0)