Multisim数字电子钟仿真电路模型:搭建你的时间小管家

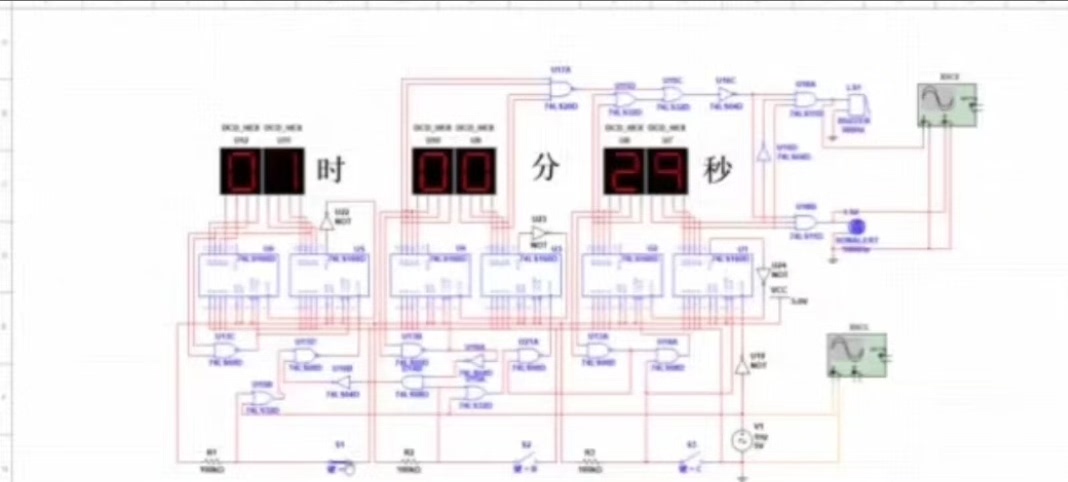

Multisim数字电子钟仿真电路模型 数字电子钟采用74LS160、74LS48、74LS00、74LS11等逻辑芯片搭建形成,可以完成时分秒,计时、译码驱动与时钟显示、校时较分以及整点报时。 有参考文档,文档包括设计方案和原理分析,以及仿真结果及分析。

嘿,各位电子爱好者!今天咱们来聊聊用Multisim搭建数字电子钟仿真电路模型,这可是个超有趣的小项目,能让你对数字电路有更深入的理解。

核心芯片大揭秘

这个数字电子钟主要是靠74LS160、74LS48、74LS00、74LS11等逻辑芯片搭起来的。

74LS160 - 计数担当

74LS160是一个同步十进制计数器。它有清零(CLR)、预置(LOAD)、使能(CEP、CET)等引脚。比如下面这段简单的Verilog代码,就能模拟它的部分功能:

module counter_74LS160 (

input wire clk, // 时钟信号

input wire clr, // 清零信号

input wire load, // 预置信号

input wire cep, // 计数使能信号1

input wire cet, // 计数使能信号2

input wire [3:0] d, // 预置数据输入

output reg [3:0] q // 计数输出

);

always @(posedge clk or posedge clr) begin

if (clr) begin

q <= 4'b0000; // 清零

end else if (load) begin

q <= d; // 预置数据

end else if (cep & cet) begin

if (q == 4'b1001) begin

q <= 4'b0000; // 计数到9后归零

end else begin

q <= q + 1; // 正常计数

end

end

end

endmodule在实际电路里,74LS160就负责实现时、分、秒的计数功能,为整个电子钟的计时打下基础。

74LS48 - 译码显示能手

74LS48是BCD - 七段译码器,它能把4位二进制代码转换为七段数码管能识别的信号,让数字显示出来。看下面这个VHDL代码片段:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity decoder_74LS48 is

Port ( bcd_in : in STD_LOGIC_VECTOR (3 downto 0);

seg_out : out STD_LOGIC_VECTOR (6 downto 0));

end decoder_74LS48;

architecture Behavioral of decoder_74LS48 is

begin

process(bcd_in)

begin

case bcd_in is

when "0000" => seg_out <= "0000001"; -- 显示0

when "0001" => seg_out <= "1001111"; -- 显示1

when "0010" => seg_out <= "0010010"; -- 显示2

-- 省略其他数字的译码

when others => seg_out <= "1111111"; -- 无效输入时全灭

end case;

end process;

end Behavioral;在数字电子钟里,它接收74LS160的计数结果,然后把对应的数字显示在数码管上,让我们能直观看到时间。

74LS00与74LS11 - 逻辑控制大师

74LS00是四2输入与非门,74LS11是三3输入与门。它们主要用于逻辑控制,比如校时、校分以及整点报时的逻辑判断。举个简单例子,如果要用74LS00实现一个简单的逻辑反转:

module not_gate_using_74LS00 (

input wire a,

output wire y

);

assign y = ~(a & a); // 用与非门实现非门功能

endmodule在整个数字电子钟系统里,它们巧妙地组合起来,实现各种复杂的逻辑功能。

功能实现全解析

计时、译码驱动与时钟显示

通过74LS160的级联实现时、分、秒的计数,秒满60向分进位,分满60向时进位,时满24归零。74LS48把这些计数值转换成数码管能显示的信号,让时间清晰呈现。

校时校分

通过74LS00和74LS11组成的逻辑电路,我们可以实现校时校分功能。比如按下校时按钮,就能单独调整小时数,这背后就是通过逻辑门控制74LS160的计数使能和预置功能。

整点报时

利用逻辑门判断是否到整点,到整点时触发蜂鸣器报时。这就需要把时、分的计数结果通过逻辑门进行判断,当分钟为0且小时为整数时,输出信号驱动蜂鸣器发声。

参考文档助力项目

要是你在搭建过程中遇到问题,参考文档可是个好帮手。里面详细的设计方案和原理分析,能帮你理清思路,仿真结果及分析又能让你快速定位可能出现的错误。

Multisim数字电子钟仿真电路模型 数字电子钟采用74LS160、74LS48、74LS00、74LS11等逻辑芯片搭建形成,可以完成时分秒,计时、译码驱动与时钟显示、校时较分以及整点报时。 有参考文档,文档包括设计方案和原理分析,以及仿真结果及分析。

总之,用Multisim搭建数字电子钟仿真电路模型,既能锻炼你的数字电路知识,又能做出一个超实用的小玩意。赶紧动手试试吧!

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献35条内容

已为社区贡献35条内容

所有评论(0)