GD32F30x时钟树

目录

1、RCU 时钟介绍

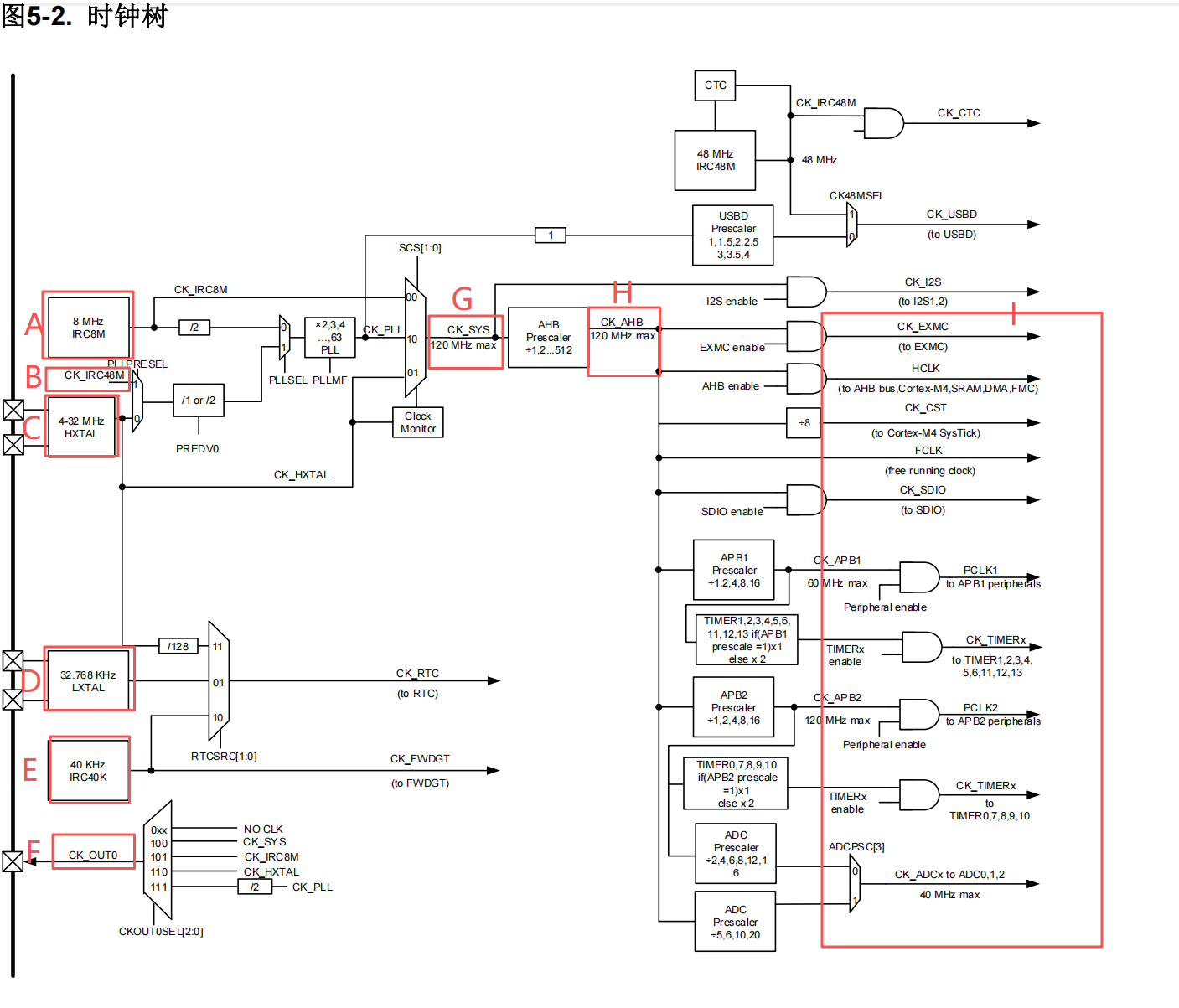

RCU(Reset and Clock Unit,复位和时钟单元),时钟如同MCU的"心跳",为内核和外设提供工作节拍,是MCU能正常运行的基本条件。时钟控制单元提供了一系列频率的时钟功能,包括一个内部RC振荡器时钟(IRC)、一个外部高速晶体振荡器时钟(HXTAL)、一个外部低速晶体振荡器时钟(LXTAL)、一个HXTAL时钟监视器、时钟预分频器、时钟多路复用器和时钟门控电路等,RCU主要提供以下几种时钟源:

| 如图5.2 | 时钟源 | 名称 | 典型频率 | 主要用途 |

|---|---|---|---|---|

| A | IRC8M | 内部8MHz RC振荡器 | 8MHz | 上电默认时钟,可软件微调 |

| B | IRC48M | 内部48MHz RC振荡器 | 48MHz | 专供USB模块,精度满足USB要求 |

| C | HXTAL | 外部高速晶振 | 4-32MHz | 高精度主时钟源(常用8MHz) |

| D | LXTAL | 外部低速晶振 | 32.768kHz | 为RTC提供精准时钟 |

| E | IRC40K | 内部40kHz RC振荡器 | 40kHz | 独立看门狗专用 |

2、GD32F30x时钟配置

初始化时,调用由GD32官方库提供的SystemInit()函数,时钟的初始化,就是在这个函数中进行,其主要的功能是配置系统时钟CK_SYS(即主频),AHB、APB1以及APB2时钟。不同系列的MCU有一些差别,但实现方式基本相同:首先将RCU关于CK_SYS,AHB、APB1以及APB2时钟配置的一些寄存器恢复到默认值,然后再执行system_clock_config()函数。

void SystemInit (void)

{

/* FPU settings */

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

SCB->CPACR |= ((3UL << 10*2)|(3UL << 11*2)); /* set CP10 and CP11 Full Access */

#endif

/* reset the RCU clock configuration to the default reset state */

/* Set IRC8MEN bit */

RCU_CTL |= RCU_CTL_IRC8MEN;

RCU_MODIFY

RCU_CFG0 &= ~RCU_CFG0_SCS;

#if (defined(GD32F30X_HD) || defined(GD32F30X_XD))

/* reset HXTALEN, CKMEN and PLLEN bits */

RCU_CTL &= ~(RCU_CTL_PLLEN | RCU_CTL_CKMEN | RCU_CTL_HXTALEN);

/* disable all interrupts */

RCU_INT = 0x009f0000U;

#elif defined(GD32F30X_CL)

/* Reset HXTALEN, CKMEN, PLLEN, PLL1EN and PLL2EN bits */

RCU_CTL &= ~(RCU_CTL_PLLEN |RCU_CTL_PLL1EN | RCU_CTL_PLL2EN | RCU_CTL_CKMEN | RCU_CTL_HXTALEN);

/* disable all interrupts */

RCU_INT = 0x00ff0000U;

#endif

/* reset HXTALBPS bit */

RCU_CTL &= ~(RCU_CTL_HXTALBPS);

/* Reset CFG0 and CFG1 registers */

RCU_CFG0 = 0x00000000U;

RCU_CFG1 = 0x00000000U;

/* configure the system clock source, PLL Multiplier, AHB/APBx prescalers and Flash settings */

system_clock_config();

}3、GD32F30x时钟树

GD32F30x时钟树,来源于官方用户手册。

图 5-2. GD32F303系统时钟树

预分频器可以配置AHB、APB2和APB1域的时钟频率。AHB、APB2、APB1域的最高时钟频率分别为120MHz、120MHz、60MHz。RCU通过AHB时钟(HCLK)8分频后作为Cortex系统定时器(SysTick)的外部时钟。通过对SysTick控制和状态寄存器的设置,可选择上述时钟或AHB(HCLK)时钟作为SysTick时钟。

ADC时钟由APB2时钟经2、4、6、8、12、16分频或由AHB时钟经5、6、10、20分频获得,它们是通过设置RCU_CFG0和RCU_CFG1寄存器的ADCPSC位来选择。

TIMER时钟由CK_APB1和CK_APB2时钟分频获得,如果APBx(x=0,1)的分频系数不为1,则

TIMER时钟为CK_APBx(x=0,1)的两倍。

现在,我们结合图 5-1. GD32F303系统时钟树对时钟树进行分析:

(1) 标注G为CK_SYS,即系统主时钟,它一条线连接至CK_I2S,给I2S外设提供时钟,另一条线经过AHB分频器,输出到CK_AHB,即标注H。

(2) CK_AHB为AHB总线时钟,AHB总线时钟或直连,或经过APB1/APB2分频I位置的外设提供时钟。

(3) 那么,CK_SYS从何而来呢,我们看标注G的左边,CK_SYS通过SCS位域选择CK_IRC8M、CK_PLL、CK_HXTAL作为时钟来源,其中CK_IRC8M来源于标注A,即IRC8M(MCU内部8M RC时钟);CK_HXTAL来源于标注C,即HXTAL(外部时钟)。

(4) CK_PLL来源于锁相环倍频器输出,倍频系数通过PLLMF位域选择,而PLLMF来源于两个地方,一 个 为 IRC8M 的 2 分 频 , 另 外 一 个 为 预 分 频 器 PREDV0 , 而 PREDV0 来 源 于 标 注 B , 即CK_IRC48M(内部48M RC时钟)和标注C,即HXTAL(外部高速时钟)。

(5) 通过以上分析可以得出结论,CK_PLL的时钟源为A:IRC8M、B:IRC48M、C:HXTAL,用户通过相关寄存器设置选择时钟线。

(6) 和前面分析相同,RTC的时钟来自于C:HXTAL的128分频、D:LXTAL(外部32.768K低速时钟)、E:IRC40K(内部40K RC时钟);FWDGT的时钟来源于C:IRC40K。

(7) 标注E位置为时钟输出线,它的作用是将MCU内部的一些时钟信号线输出到特定IO口上(大部分系列MCU的PA8口都可被设置为时钟输出口0,有些系列MCU含有两组输出IO,具体IO配置请参考各系列MCU Datasheet)用来给其他器件提供基准时钟。由图中可看出通过设置位域CK_OUT0,输出的时钟包括CK_PLL、CK_IRC8M、CK_HXTAL、CK_PLL的2分频。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)