为什么用目前的AI大模型无法独立开发FPGA系统

目录

AI在图像识别、自然语言处理、代码生成甚至游戏策略等多个领域取得了令人瞩目的成就。特别是大型语言模型(LLM)的出现,使得AI能够辅助人类编写软件代码,极大地提高了软件开发效率。但是尽管AI可以辅助FPGA开发的某些环节,但至今为止,AI仍然无法完全独立地完成一个复杂FPGA程序的开发任务。

1.FPGA开发的特殊性

1.1硬件描述语言与软件编程的差异

FPGA开发主要使用硬件描述语言(HDL),如Verilog或VHDL,这些语言虽然语法上与传统的软件编程语言有相似之处,但其思维模式和设计却不同。软件编程关注的是指令的顺序执行和状态变化,而硬件描述语言描述的是并行运行的电路结构。这种并行性是FPGA的核心特性,也是AI难以把握的关键点。

当AI生成软件代码时,它主要处理的是线性逻辑流,即使涉及多线程或异步操作,最终在处理器上仍然是通过时间分片或中断机制来实现的"伪并行"。而FPGA中的并行是真正的物理并行,数百个逻辑单元可以同时工作,这种思维方式对人类工程师来说都需要长时间训练才能掌握,对基于统计模式的AI而言更是巨大的挑战。

另外一方面,由于整个网络公开的EDA资源,相对于传统的软件程序,其数量和质量微乎其微,因此AI无法从中训练得到较好的硬件语言编程能力。

1.2 时序约束的敏感性

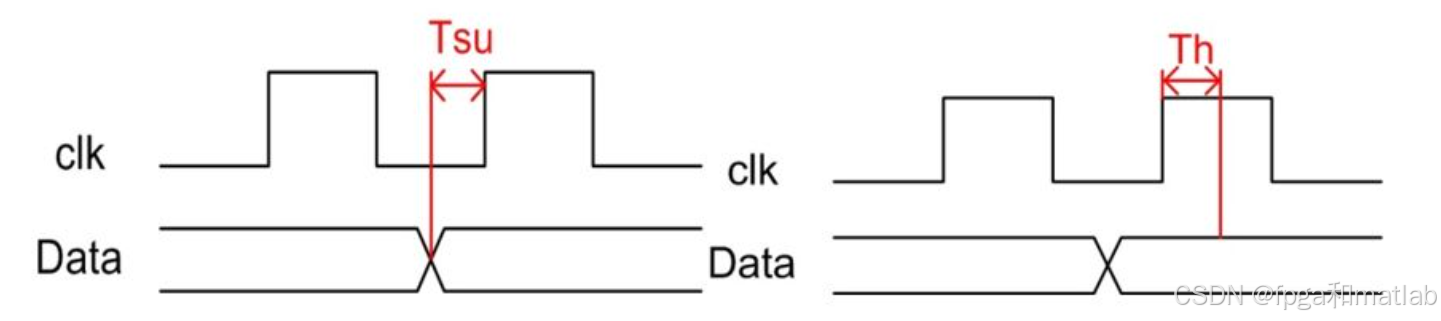

FPGA设计中最具挑战性的是时序约束(Timing Constraints)。在FPGA中,信号必须在规定的时钟周期内从一个寄存器传播到另一个寄存器,否则会导致建立时间(Setup Time)或保持时间(Hold Time)违例,从而使整个系统失效。这种时序要求不仅取决于逻辑设计本身,还受到物理布局、布线延迟、温度变化、电压波动等多种因素的影响。

AI模型在生成代码时,很难准确预测这些物理层面的影响。当前的AI模型主要基于文本模式进行训练,缺乏对物理世界电磁特性、信号完整性、时钟树分布等硬件知识的深刻理解。即使AI能够生成语法正确的Verilog代码,也无法保证这些代码在综合、布局布线后能够满足严格的时序要求。

1.3 资源优化与面积效率的平衡

FPGA芯片上的逻辑资源(如查找表LUT、触发器FF、块RAM、DSP切片等)是有限的。优秀的FPA设计需要在功能实现、时序性能和资源利用率之间找到最佳平衡点。这种优化往往需要设计师根据具体应用场景做出权衡决策,而这些决策通常基于丰富的经验和对目标器件架构的深入理解。

AI模型虽然可以通过学习大量优秀设计案例来模仿某些优化模式,但面对新的、独特的设计需求时,往往难以做出恰当的权衡。特别是在资源极度紧张的情况下,如何重新架构设计、流水线化关键路径、共享资源等高级优化技巧,目前仍然是人类工程师的专属领域。

2.AI大模型的局限性

2.1 训练数据的稀缺性

与软件代码相比,高质量、标注完善的FPGA设计数据要少得多。GitHub等平台上虽然有大量的软件代码仓库,但专业的FPGA项目相对较少,而且很多涉及商业机密或专利技术的设计并不公开。这导致AI模型在训练时缺乏足够的优质样本,难以学习到FPGA设计的精髓。

此外,FPGA设计不仅仅是代码本身,还包括综合约束文件、时序约束文件、仿真测试平台、综合报告、布局布线报告等一系列配套文件。一个完整的FPA设计流程产生的数据量巨大,但这些数据之间的关联性复杂,很难被AI模型有效学习和利用。现有的AI模型大多只学习了HDL代码的表层语法模式,而未能深入理解设计意图、架构选择和优化策略。

2.2 缺乏物理世界的感知能力

FPGA设计最终要映射到具体的物理器件上,这个过程涉及到半导体物理、电磁学、热力学等多个物理学分支的知识。AI模型作为纯软件实体,缺乏对这些物理现象的直接感知和理解能力。它无法"感受"信号在导线上传播的延迟,无法"体验"温度变化对电路性能的影响,也无法"观察"布局布线工具产生的实际结果。

这种物理感知的缺失使得AI在设计迭代过程中处于劣势。人类工程师可以通过查看综合报告、时序分析报告、功耗分析报告等,结合自己的经验判断问题所在并进行针对性优化。而AI只能基于文本模式进行推测,无法真正理解这些报告背后的物理意义,更难以提出有效的改进方案。

2.3 验证与调试的复杂性

FPGA开发的验证和调试过程极其复杂,通常需要构建完善的测试平台(Testbench),进行功能仿真、时序仿真,甚至需要在实际硬件上进行板级验证。这个过程往往占据整个开发周期的60%以上。AI在生成测试用例方面有一定能力,但面对复杂的边界条件、异常场景和并发问题时,往往难以覆盖所有可能的情况。

更重要的是,当设计出现问题时,调试过程需要工程师具备深厚的系统知识和直觉判断能力。波形分析、逻辑分析仪数据解读、硬件探针测量等技能都是基于长期实践形成的"工程直觉",这种直觉很难通过数据统计的方式传递给AI模型。即使AI能够指出代码中可能存在的问题,也往往无法提供准确的根本原因分析和有效的解决方案。

3.硬件调试问题

FPGA程序的“代码正确”不等于“硬件可用”——HDL代码经过综合、布局布线生成比特流后,还需在实际电路板上调试,解决物理层问题:如I/O电平不匹配导致的数据错误、电源噪声导致的时序抖动、布线寄生参数导致的信号完整性问题(SI)、电磁干扰(EMI)导致的功能异常等。

这一环节的核心是“真实物理世界的反馈与修正”:例如,工程师通过示波器观察到某路输出信号有纹波,会判断是电源滤波不足,进而修改硬件电路(如增加电容)或调整FPGA的输出驱动强度;而AI无法接入真实的硬件调试环境,既无法获取示波器、逻辑分析仪的物理信号数据,也无法理解“信号纹波”与“FPGA代码中I/O配置”的因果关系。即使 AI 能生成理论上正确的代码,也无法解决实际板级调试中的物理问题,而这些问题往往是FPGA开发中最耗时、最依赖经验的环节。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献22条内容

已为社区贡献22条内容

所有评论(0)