以太网PHY芯片简介 —— (一)物理架构

前言

以太网作为当今网络通信的核心技术,从日常上网到工业互联、数据中心高速传输,都离不开底层硬件的支撑。而PHY芯片(物理层收发器)正是连接数字世界与物理传输介质的“桥梁”,是以太网物理层的核心器件。本文作为PHY芯片系列开篇,将从以太网七层协议切入,逐步拆解PHY芯片的核心定位、作用场景,重点详解其物理架构(PCS/PMA/PMD)的底层逻辑,帮你快速建立对PHY芯片的基础认知。

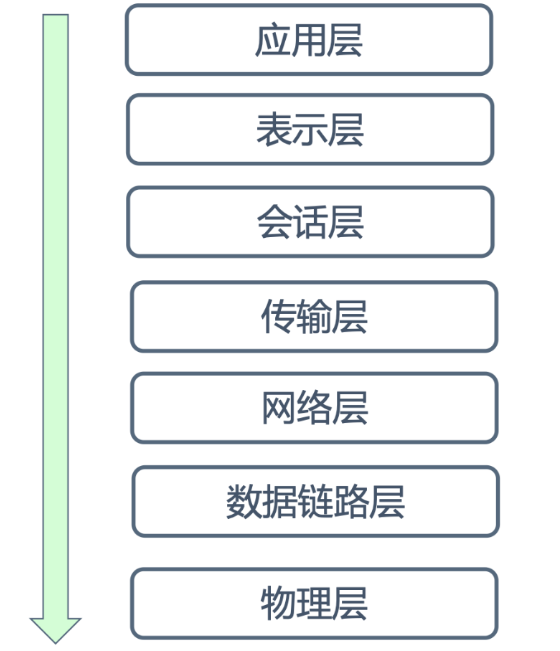

一、以太网七层协议:

网络通信的“标准化框架”

1. 历史背景

从“混乱割据”到“统一标准”

在OSI七层模型诞生前(20世纪70-80年代),网络领域处于“厂商割据”状态——IBM、DEC、惠普等企业各自推出私有网络架构,协议互不兼容,不同品牌设备无法互通,严重阻碍网络技术普及。

为打破壁垒,国际标准化组织(ISO) 于1984年正式发布ISO/IEC 7498标准,定义开放式系统互联(OSI :Open System Interconnection)参考模型,将复杂网络通信拆解为7个标准化层次,成为网络设备互通的核心框架 。

2. 七层协议概述

分层协作,各司其职

OSI七层模型遵循“下层为上层提供服务,上层依赖下层实现功能”的逻辑,每层仅聚焦单一核心任务,降低通信复杂度,具体分层及核心作用如下:

- 7层(应用层):直接面向用户,提供文件传输、邮件、网页访问等服务(如HTTP、FTP协议);

- 6层(表示层):负责数据格式转换、加密解密(如SSL/TLS);

- 5层(会话层):建立、管理、终止应用间的通信会话;

- 4层(传输层):实现端到端可靠传输(如TCP的流量控制、UDP的无连接传输);

- 3层(网络层):负责数据路由寻址(如IP协议,决定数据传输路径);

- 2层(数据链路层):将数据封装成帧,实现相邻设备间可靠传输(MAC层属于此层);

- 1层(物理层):最底层核心,负责原始比特流(0/1信号)在物理介质(网线、光纤)上的传输,定义电气特性、接口标准、信号时序。

3. 核心作用

标准化与解耦

OSI七层模型的价值在于两点:

1. 实现“跨厂商互通”,不同设备遵循同一分层标准即可通信;

2. 分层解耦,每层功能独立优化,无需改动上层逻辑(如物理层升级传输介质,不影响应用层服务)。

二、从物理层到PHY芯片:

网络通信的“硬件翻译官”

1. 物理层的核心痛点

物理层作为网络通信的“地基”,需解决数字信号与物理介质的适配问题——上层(数据链路层MAC)输出的是并行数字信号,无法直接在网线、光纤等介质中传输,必须经过编码、串行化、信号转换等处理,而PHY芯片正是承担这一核心任务的硬件载体。

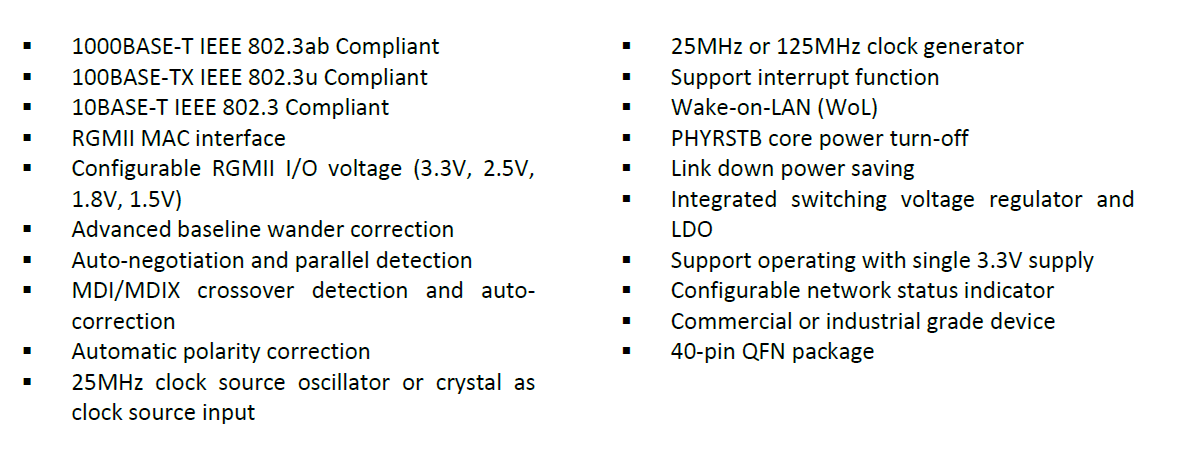

2. PHY芯片的定义与核心作用

PHY(Physical Layer Transceiver,物理层收发器)是实现OSI物理层功能的专用芯片,核心定位是“数字信号与物理信号的翻译官”,核心作用包括:

- 发送端:将MAC层的并行数字信号,转换为适合物理介质传输的差分电信号/光信号;

- 接收端:将物理介质传输的微弱信号,还原为MAC层可识别的并行数字信号;

以目前主流国产千兆PHY 联芸MAE0621A-Q3C芯片为例,芯片还支持速率协商(10M/100M/1000M)、双工模式匹配、网络唤醒等功能:

3. 典型应用场景

PHY芯片作为网络设备的“必备组件”,覆盖全场景网络通信:

- 消费电子:电脑网卡、路由器、光猫、智能电视;

- 工业领域:工业交换机、PLC、运动控制器(适配-40℃~85℃严苛环境);

- 通信与安防:5G小基站、IPC摄像头、DVR/NVR录像机;

- 数据中心:服务器、交换机高速端口(2.5G/5G/10G以太网)。

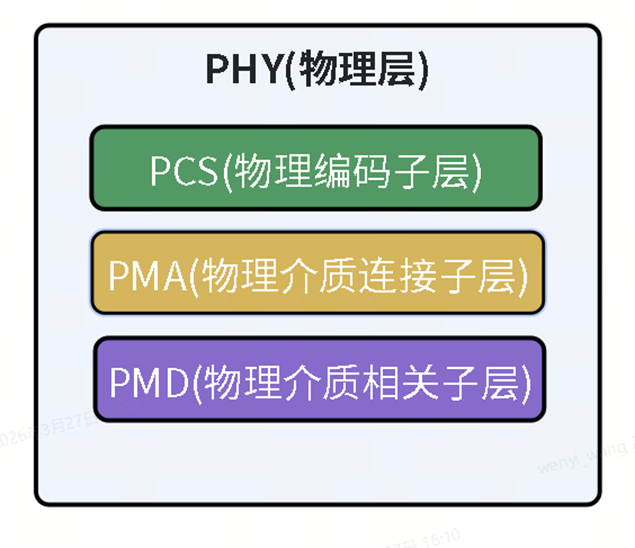

三、PHY芯片物理架构

PCS-PMA-PMD三层协作逻辑

PHY芯片的物理架构遵循IEEE 802.3以太网标准,核心分为PCS(物理编码子层)、PMA(物理介质附加子层)、PMD(物理介质相关子层) 三层,每层分工明确、逐级衔接,完成从数字信号到物理信号的全流程转换 。

1. PCS(Physical Coding Sublayer,物理编码子层)

核心定位

PHY的“数字处理核心”,位于MAC与PMA之间,负责数字信号的编码、解码与格式转换,解决信号传输的可靠性问题。

核心功能

1. 编码/解码:将MAC层的原始数据转换为适合传输的编码格式,不同速率对应不同方案——10Base-T用曼彻斯特编码、100Base-TX用4B/5B编码、千兆以太网用4D-PAM5+8状态网格编码,实现直流平衡、时钟恢复与错误检测;

2. 加扰/解扰:通过伪随机序列打乱数据,避免长串0/1导致的时钟失锁,降低电磁干扰(EMI);

3. 帧同步与对齐:插入同步标记,让接收端识别数据起始位置,多通道传输时实现通道偏差补偿;

4. 载波监听/冲突检测(CSMA/CD):半双工模式下,检测介质占用状态,避免数据冲突。

关键作用

屏蔽上层MAC对物理传输细节的感知,实现“介质无关性”——无论用双绞线还是光纤,MAC层逻辑无需改动。

2. PMA(Physical Media Attachment,物理介质附加子层)

核心定位

PHY的“高速串行核心”,衔接PCS与PMD,负责并行信号与串行信号的转换,是高速传输的关键。

核心功能

1. 串并/并串转换(SerDes):发送端将PCS输出的并行编码数据转为高速串行比特流,接收端将串行数据还原为并行数据,适配高速传输需求;

2. 时钟数据恢复(CDR):接收端从串行信号中提取时钟信号,确保收发时序同步(核心依赖PLL锁相环);

3. 信号预加重/均衡:发送端对高频信号增强(预加重),接收端对失真信号补偿(均衡),抵消长距离传输的信号衰减;

4. 链路状态监测:检测信号丢失、载波异常,反馈给上层做故障处理。

关键作用

实现“低速并行”到“高速串行”的转换,是PHY芯片支持千兆、万兆速率的核心模块。

3. PMD(Physical Media Dependent,物理介质相关子层)

核心定位

PHY的“介质适配核心”,直接对接物理传输介质,是PHY与外部硬件的接口层。

核心功能

1. 介质信号转换:电口PHY将PMA输出的串行电信号转为差分电压信号(双绞线传输);光口PHY通过激光驱动器将电信号转为光信号(光纤传输),接收端反向转换;

2. 线路驱动与接收:驱动RJ45、SFP+等接口,匹配介质阻抗(如双绞线100Ω差分阻抗),接收微弱信号并放大;

3. 电气特性控制:定义信号电压、抖动容限、共模抑制比,适配不同介质的传输标准;

4. 接口适配:支持MDI(介质无关接口)自动翻转(Auto-MDIX),无需区分直连/交叉网线。

关键作用

实现PHY与物理介质的无缝对接,不同介质(双绞线、光纤、背板)对应不同PMD设计,是PHY“介质适配性”的核心保障。

四、三层架构协作流程(发送/接收全链路)

发送端(MAC→PHY→介质)

1. MAC层输出并行数字数据→PCS层编码、加扰、插入同步标记→生成编码后并行数据;

2. PMA层将并行数据串行化,添加时钟信息,做预加重处理→输出高速串行电信号;

3. PMD层转换为介质适配信号(差分电信号/光信号),驱动接口发送至物理介质。

接收端(介质→PHY→MAC)

1. PMD层接收介质信号,转换为PMA可识别的电信号,初步放大;

2. PMA层通过CDR恢复时钟,均衡补偿失真信号,解串为并行数据;

3. PCS层解码、解扰、去除同步标记→还原原始数据,传输给MAC层。

总结

PHY芯片作为以太网物理层的核心,其PCS-PMA-PMD三层架构实现了“数字处理→高速串行→介质适配”的全链路功能,是网络通信从“软件逻辑”到“硬件传输”的关键纽带。理解这一架构,是掌握PHY芯片工作原理、排查底层通信故障、优化硬件设计的基础。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)