基于TSV的多芯片三维堆叠结构高速信号完整性分析与建模

摘要

随着三维系统级封装(3D SiP)与三维集成电路(3D-IC)技术的快速发展,硅通孔(TSV)已成为实现芯片垂直互连的关键技术。相比传统二维封装,TSV能够显著缩短互连路径、减小封装面积,为高性能电子系统提供了更紧凑、更高效的集成方案。然而,高频信号在TSV-RDL-凸点构成的复杂三维互连结构中传输时,会面临插入损耗、串扰、阻抗不连续等信号完整性(SI)问题。本文基于全波电磁仿真与时域眼图分析,系统研究了多芯片堆叠结构中芯片数量、互连拓扑及TSV几何尺寸对信号传输性能的影响,并构建了GSG配置下TSV的传输线等效电路模型,实现了物理参数变化与电路元件值之间的映射。研究结果表明,堆叠芯片数量的增加会显著恶化插入损耗与串扰,氧化层厚度与TSV间距的增大有助于改善传输性能,而增大TSV直径在固定间距下可能适得其反。本文为TSV高速互连的设计优化提供了系统的理论依据与工程指导。

关键词:硅通孔(TSV);三维系统级封装(3D SiP);信号完整性;插入损耗;串扰;等效电路建模

一、引言

在摩尔定律逐渐逼近物理极限的背景下,半导体产业正加速向三维集成方向演进。三维系统级封装(3D SiP)通过将多颗芯片在垂直方向进行堆叠,实现了系统功能的高度集成。与传统二维封装或仅依赖引线键合的方案相比,3D SiP利用TSV、再分布层(RDL)和微凸点构成的垂直互连通道,大幅缩短了芯片间的信号传输路径,同时显著降低了封装基板的占用面积。这种结构在提升带宽密度、降低功耗、缩小系统尺寸方面具有显著优势。

然而,三维集成的引入也带来了新的电气挑战。随着数据速率向6 Gbps乃至更高方向发展,TSV、RDL和凸点所构成的互连通道不再是理想的传输路径。有耗硅衬底的存在、TSV之间的耦合效应、以及由几何结构引起的阻抗不连续,都会引发信号衰减、时序抖动和串扰等问题。因此,对TSV多芯片堆叠结构进行精确的电磁建模与全面的信号完整性分析,已成为高性能3D系统设计不可或缺的环节。

本文围绕TSV多芯片堆叠结构,从系统架构、互连配置、频域特性、时域响应及等效电路建模等多个维度展开研究,旨在揭示关键设计参数对信号传输质量的影响规律,为高速三维集成系统的设计与优化提供理论支撑。

二、堆叠结构与互连建模

2.1 堆叠系统架构

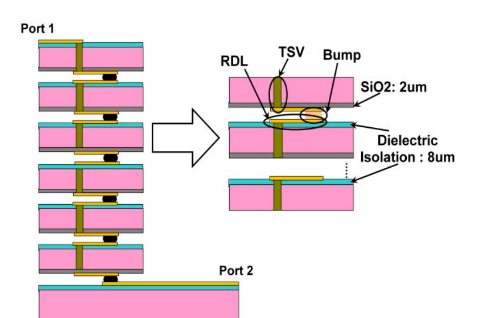

本文研究的模型为最多包含6片芯片的垂直堆叠结构,其中底部为一颗控制器芯片,上部为多颗相同功能的存储芯片。完整的垂直互连路径由交替排布的TSV、RDL和微凸点构成。信号从顶部芯片出发,依次穿过TSV、RDL和凸点,逐层传递至底部芯片。

在实际结构中,TSV与微凸点之间设置了水平偏移量。这种“非堆叠”设计有效避免了TSV直接位于凸点上方所引发的热机械应力集中问题,提高了封装结构的可靠性。

2.2 互连配置与仿真方法

为全面评估信号完整性,本文采用了两种互连配置:

- GSSG(地-信号-信号-地)配置:用于分析插入损耗(S21),该配置提供了清晰的信号返回路径。

- GSG(地-信号-地)配置:用于分析串扰(S31)以及后续等效电路的提取,该配置能够有效表征单信号路径与地之间的耦合关系。

仿真流程包括以下步骤:首先,利用三维全波电磁场仿真器提取互连结构的S参数模型;随后,将S参数导入电路仿真器进行时域眼图分析;最后,基于GSG-TSV结构建立传输线等效电路,并通过参数拟合实现与电磁仿真结果的匹配。

三、堆叠效应与互连拓扑对SI性能的影响

3.1 芯片堆叠数量对插入损耗与串扰的影响

仿真结果表明,随着堆叠芯片数量的增加,插入损耗(S21)和近端串扰(S31)均呈现恶化趋势。具体而言,每增加一片芯片,在关键频点处的插入损耗平均增加约0.3~0.4 dB。这一现象主要归因于两方面:一是RDL金属导体在高频下的趋肤效应与表面粗糙度引起的导体损耗;二是有耗硅衬底导致的能量泄漏,信号通过氧化层电容与硅衬底电导发生耦合,以热形式耗散。

与此同时,近端串扰随堆叠数量增加而加剧,主要原因在于更长的互连路径导致相邻信号线之间的并行耦合长度增加,从而使电磁耦合能量累积效应更加显著。

3.2 “梯状”与“阶梯状”拓扑对比

除了垂直堆叠数量,TSV与凸点的平面布局拓扑同样影响SI性能。本文对比了两种典型拓扑:

- 梯状拓扑:TSV与凸点基本垂直对齐或仅有微小偏移。

- 阶梯状拓扑:TSV与凸点在各层之间存在较大水平偏移,整体呈“之”字形布局。

从插入损耗的角度看,两种拓扑的性能差异不大。然而,阶梯状拓扑在整个路径上需要占用更大的硅衬底面积,导致布线面积增加,进而提高了与邻近电路的串扰风险以及对电磁干扰(EMI)的敏感度。因此,在同等性能条件下,梯状拓扑通常更具优势。

四、时域眼图分析

为直观评估互连系统对实际数字信号传输的影响,本文基于提取的S参数模型进行了眼图仿真。仿真条件设置如下:

- 数据速率:6 Gbps

- 激励信号:伪随机二进制序列(PRBS),寄存器长度为32位

- 信号幅度:200 mVpp

- 终端负载:50 Ω

仿真结果,随着堆叠芯片数量从1片增加到6片,眼图张开度逐渐减小,抖动增加,上升/下降时间延长。这表明路径的插入损耗与频率选择性衰减共同作用,导致了码间干扰(ISI)和时序抖动。尽管如此,在6 Gbps速率下,6片堆叠结构的眼图仍保持一定张开度,说明当前设计在该速率下仍具备良好的传输质量。

五、GSG-TSV等效电路建模与参数化分析

5.1 等效电路模型

为便于快速设计与优化,本文建立了GSG配置下TSV的传输线等效电路模型。该模型包含以下关键元件:

- R与L:分别表示信号TSV的电阻与电感,反映导体损耗与自感效应。

- C_oxide:信号TSV与硅衬底之间氧化层形成的电容,决定了低频隔离能力。

- C_silicon与G_silicon:分别表征有耗硅衬底的容性耦合与阻性损耗,是高频能量泄漏的主要通道。

通过优化调整RLCG元件值,可使等效电路的S参数响应与三维电磁仿真结果高度匹配,验证了模型的准确性。

5.2 几何参数变化对传输性能的影响

利用该等效电路,本文系统分析了TSV氧化层厚度、间距与直径变化对插入损耗的影响,并建立了物理尺寸与电路元件值之间的映射关系。

- 氧化层厚度增加(0.2μm→0.5μm):提高了信号与硅衬底的隔离度,C_oxide减小,插入损耗改善。

- TSV间距增大(30μm→50μm):信号与地之间的C_silicon和G_silicon减小,泄漏电流下降,插入损耗改善。

- TSV直径增大(5μm→10μm):在固定间距下,虽降低了R与L,但C_oxide、C_silicon和G_silicon显著增大,导致整体插入损耗恶化。

上述分析表明,在设计优化中,氧化层厚度与TSV间距是改善信号完整性的有效手段,而单纯增大TSV直径需谨慎评估其对衬底耦合的负面影响。

六、结论与设计指导

本文基于全波电磁仿真与等效电路建模,系统分析了TSV多芯片堆叠结构的高速信号完整性,得出以下主要结论与设计建议:

- 堆叠数量的影响:芯片堆叠数量每增加一片,插入损耗增加约0.3~0.4 dB,串扰亦随之加剧。在系统设计时,需根据目标数据速率与链路预算合理选择堆叠层数。

- 互连拓扑的取舍:梯状拓扑在插入损耗性能上与阶梯状拓扑相当,但占用面积更小,串扰风险更低,应作为优先选择。

- TSV几何参数的优化方向:

- 适当增加氧化层厚度有助于提升信号隔离度;

- 增大TSV间距可降低衬底耦合效应;

- 增大TSV直径需谨慎评估,避免因间距相对缩小而导致损耗恶化。

- 等效电路模型的应用价值:所建立的GSG-TSV等效电路模型能够有效映射几何尺寸变化对电气性能的影响,为高速互连的早期设计与快速迭代提供了有力工具。

综上所述,TSV多芯片三维堆叠技术在实现更高集成度的同时,也对信号完整性提出了更高要求。通过系统的仿真分析与合理的参数优化,可以在性能、密度与可靠性之间实现平衡,推动三维集成技术在下一代高性能电子系统中的应用与发展。

参考文献

[1] 三维系统级封装(3D SiP)与硅通孔(TSV)技术相关研究文献

[2] 高速互连信号完整性分析相关标准与方法

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)