AI系统-18自动驾驶AI SoC芯片趋势

目前主流的IT技术路线就是电脑-》手机-》汽车-》机器人的路线来发展的,然后衍生出无数其他产品,特别是手机技术应用到各种终端上。

AI SoC的应用目前在汽车上应用最广泛,所以地平线本来做机器人的反而在汽车智驾领域崛起。本来从汽车的智能驾驶角度看看未来AI SoC芯片一些可能的趋势,或许可更好的把握技术的学习和使用。

1. SoC组成相关

MCU是SoC的不?

–是的。系统级芯片(SoC)是一个将计算处理器和其它电子系统集成到单一芯片的集成电路。尽管微控制器(MCU)通常只有不到100 kB的RAM,但是事实上它是一种简易、功能弱化的SoC。

不同的SoC类型有不同的应用场景,围绕微控制器(MCU)构建的系统级芯片一般用于计算性能要求不高的消费电子、家电和IoT产品。基于微处理器(MPU)的SoC在性能和功能方面相对较高,比如手机的应用处理器(AP)。还有一种可以编程的SoC(PSoC),其部分功能可以灵活编程,就像FPGA一样。当然,针对某些特定应用领域而定制开发的SoC可能更为复杂,比如集成ADC/DAC、显示驱动,以及无线射频等功能模块。

SoC的一般组成:

-

核:至少一个微控制器(MCU)或微处理器(MPU)或数字信号处理器(DSP),但是也可以有多个处理器内核;

-

存储器:RAM、ROM、EEPROM和闪存中的一种或多种;

-

电源频率相关:电源和频率相关电路,以及计时器等

-

接口:UART、SPI、USB、CAN、Eth等

-

功能电路:例如数模转换,AI等

-

总线:AXI、APB、NOC等

复杂的SoC还会在上面分类中附带很多小IP,例如存储相关的DMA,TZC,TCM等。

在一个复杂产品中,例如汽车,上有很多的控制电路板,每个电路板上都有自己的芯片,有了SoC就可以把这些芯片使用异构核和子系统的模式都集成到一个SoC上,这样:

1. 一个芯片上通信快,消耗小,准确率高,故障小

2. SoC上所有的资源可以动态分配取用,这样就可以节省很多硬件资源,1+1>2的效果

3. 升级维护更加的容易。

当然也有缺点就是SoC坏了就全坏了,不像分散的板子,一个坏了,如果不是核心控制,其他板子还可以工作,系统不至于一下就死了。

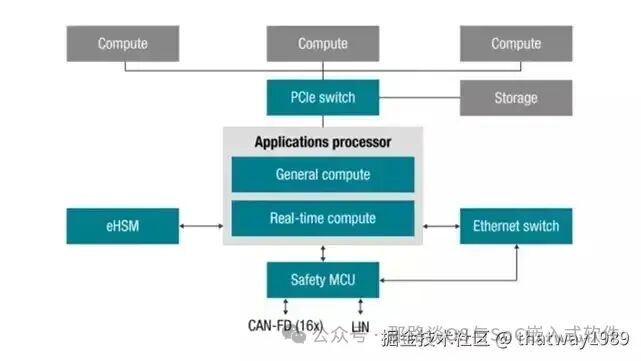

自动驾驶芯片的特点:

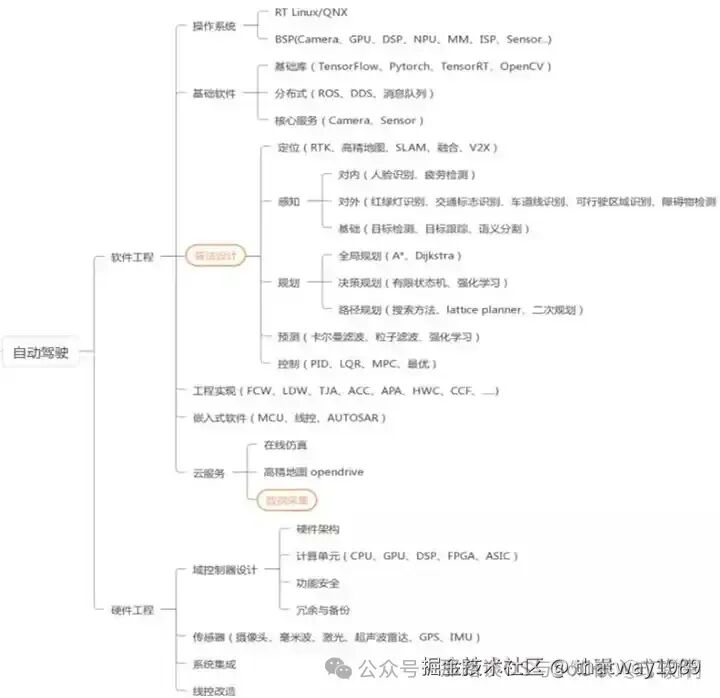

娱乐系统芯片,其实和消费电子几乎一模一样,关注音频、视频、显示、图像等、Modem等。自动驾驶芯片,注重高性能计算,一般配备有强大的NPU、GPU、DSP等。另外去集成汽车上其他的ECU电路板(运行AUTOSAR)。

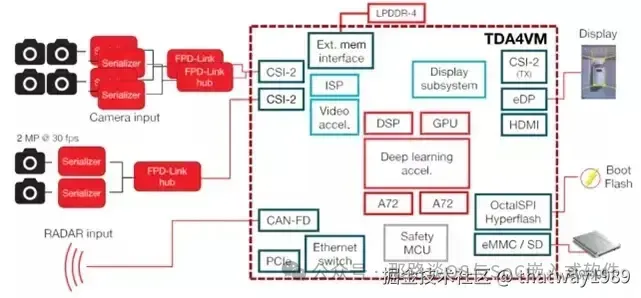

中央控制器作为自动驾驶核心部件,作为自动驾驶的“大脑”端,通常需要外接多个摄像头、毫米波雷达、激光雷达,以及IMU等设备,完成的功能包含图像识别、数据处理等。因此,其需要具备多传感器融合、定位、路径规划、决策控制、无线通讯、高速通讯的能力,因而从始至终牵动着整个处理及控制命脉。

由于自动驾驶传感器对于驾驶辅助系统的复杂度影响力(主要表现在计算能力、传输带宽、存储能力等)几乎是成倍的增加,特别是侧视摄像头的加入导致需要预处理的视频数据成倍的增加,同时,激光雷达的加入又不断地生成千万级的待处理点云信息,这就对其自动驾驶控制器计算性能及算法能力提出了比较大的需求,这也使得我们需要对自动驾驶控制器芯片选型单独提出的需求。

总之,SoC要实现汽车上的:车控域、智驾域、座舱域的三域融合,三合一,大芯片,大软件,中央集中式。

2. 芯片软硬件分工

参考之前芯片设计文章:芯片-设计流程入门

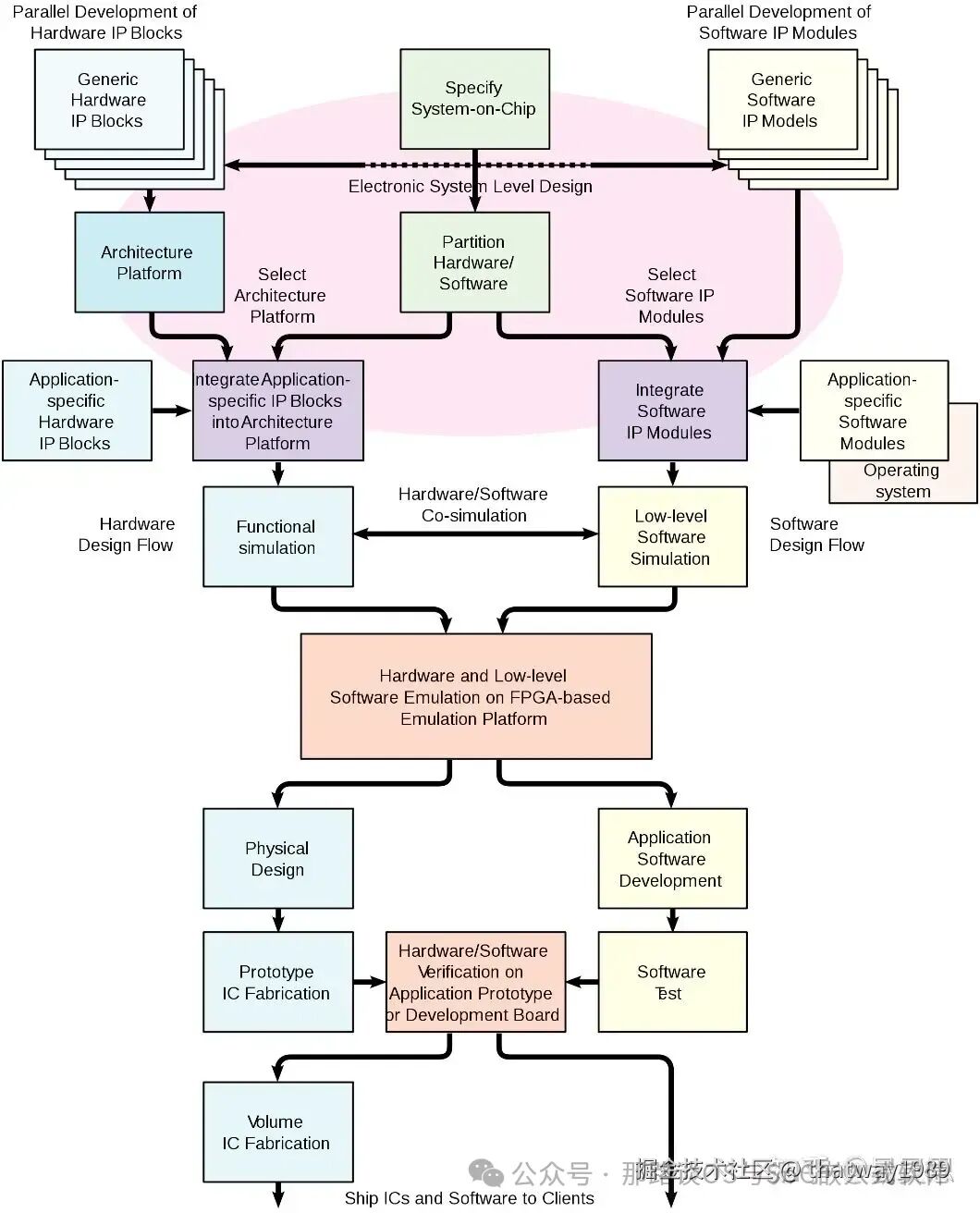

由于系统级芯片的集成度越来越高,设计工程师必须尽可能采取可复用的设计思路。

现今大部分SoC都使用预定义的IP核(包括软核、硬核和固核),以可复用设计的方式来完成快速设计。

在软件开发方面,协议栈是一个重要的概念,它用来驱动USB等行业标准接口。在硬件设计方面,设计人员通常使用EDA工具将已经设计好(或者购买)的IP核连接在一起,在一个集成开发环境(IDE)下集成各种子功能模块。系统级芯片的设计流程示意图如下:

芯片设计在被送到晶圆厂进行流片生产之前,设计人员会采取不同方式对其逻辑功能进行验证。

仿真与验证是SoC设计流程中最复杂、最耗时的环节,约占整个芯片开发周期的50%~80% ,采用先进的设计与仿真验证方法已成为SoC设计成功的关键。

在重点考虑面积、延迟、功耗的基础上,向成品率、可靠性、EMI 噪声、成本、易用性等方面转移,使系统级集成能力快速提升。

SoC芯片设计技术可以大幅度地提高系统可靠性,减少系统面积和功耗,降低系统成本。但随着人工智能以及5G的发展,传统的设计方法已经无法满足这些芯片的功能需求,将一颗SoC设计切割成不同的合适工艺节点小芯片(Chiplet),再用先进封装技术提供的高密度互联将多颗Chiplet包在同一个封装体内,将是未来的发展趋势。

Chiplet的优点:

-

可以不用那么先进的制造工艺,例如16nm以上,达到同样的效果。

-

复杂SoC中大量IP的验证变的容易

SoC的另一个巨大挑战:复杂系统对计算密度的不确定性,而这主要体现在AI计算方面。

自动驾驶软硬件涉及到的主要技术如下:

AI计算的发展其实算法很早就有,就是硬件造不出来,汽车上也是需要大的算力,就需要依赖硬件技术的进步,工艺制程、封装技术等,提供强大的算力才是王道。

3. 新技术趋势

3.1 异构计算

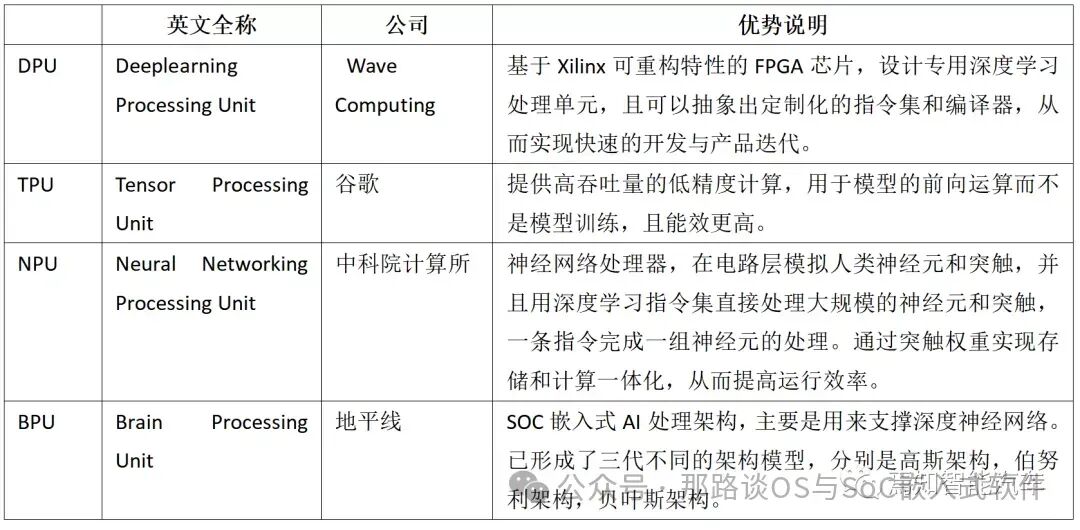

计算子系统通常包含CPU、GPU、以及AI处理器等同构或异构的计算单元。

随着人工智能应用及技术的成熟,对于AI终端运行及计算的高效、可靠、稳定的需求与日俱增,不同的应用场景对于芯片PPA的需求存在差异,单个内核已经达不到AI应用场景所需的多通路多运算流并且兼顾功耗及运算资源的目的。所以异构多核计算技术成了应对这些应用最好的解决方案。

选择核的时候考虑的点:

-

如果要运行Linux,考虑是否支持Linux

-

是否需要浮点计算及双精度浮点计算等去选择对应的核

-

结合应用场景和需求进行选择

-

方便的开发环境和平台

硬件指标主要包括:

-

在特定工艺下,频率、面积、功耗参数要求,以及典型CPU基准测试跑分(DMIPS,CoreMark等);

-

不同的指令集组合,如RISC-V 32位或是RISC-V 64位指令集、DSP、单双精度FPU等;

-

存储单元结构及大小;

-

中断个数和优先级,响应速度等;

-

支持的总线接口类型及时钟频率比等。

软件指标主要包括:

-

完善的软件开发环境和开发平台(IDE,SDK等);

-

成熟稳定的工具链(编译器,仿真器,调试器等);

-

标准的软件接口以及丰富的算法软件库等;

-

友好的第三方软件支持((Segger、IAR、Lauterbach等);

-

主流的操作系统支持(RTOS,Linux等)。

自动驾驶芯片对算力要求较高。特别是其中的AI部分,L2级别需要2个TOPS的算力,L3需要24个TOPS的算力,L4为320TOPS,L5为**4000+**TOPS。

-

通常是GPU或TPU,承担大规模浮点数并行计算需求,主要用于环境感知和信息融合,包括摄像头、激光雷达等传感器信息的识别、融合、分类等,如Xavier的GPU单元、升腾310。

-

通用核大多为ARM架构,类似于CPU,主要负责逻辑运算和决策控制,处理高精度浮点数串行计算。

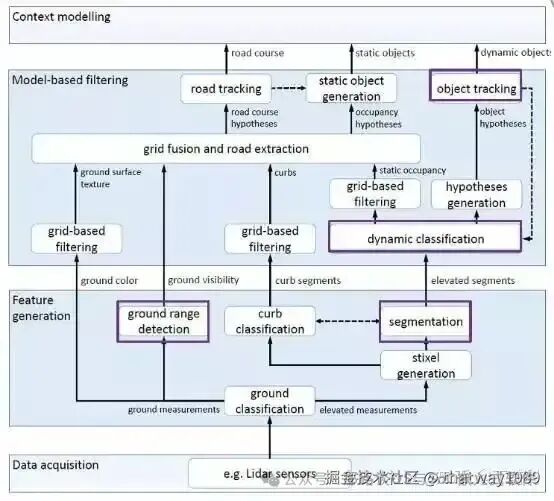

自动驾驶的实现,需要依赖环境感知传感器对道路环境的信息进行采集,将采集到的数据传送到汽车AI SoC进行处理,用来识别障碍物、可行道路等,依据识别结果,规划路径、制定车速,自动控制汽车行驶。整个过程需要在一瞬间完成,延时必须要控制在毫秒甚至微秒级别,才能保证自动驾驶的行驶安全。

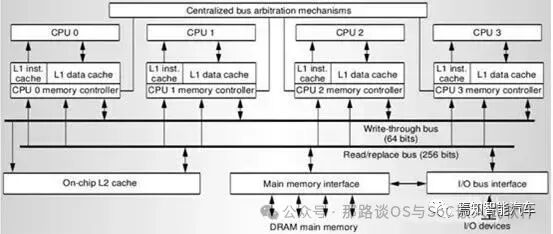

3.2 存储单元

存储子系统通常会采用DDR/LPDDR/HBM/GDDR等标准的大容量外部动态随机存储器,以及基于SRAM的静态高速片上存储器。

在AI芯片里面,NPU的瓶颈一大部分就是存储速率跟不上,所以需要采用LPDDR5、SRAM等更高速的存储技术。另外存储容量也在增大,以空间换时间,把海量数据直接放入高速内存中,运算更快。

选择合适的存储器解决方案是满足目标系统对车载控制器芯片的功能和性能要求的关键,帮助设计人员解决其目标片上系统 (SoC) 的功耗、性能和面积要求。同时,附加存储控制主要可以扩充SOC芯片由于内部存储资源不充足所产生的存储数据溢出。通常附加存储可临时作为操作系统、数据驱动的资源池,大大降低了程序调用的难度,提升了运行效率。

3.3 丰富的外设

对于自动驾驶芯片来讲,足够多且有效的接口外设是必不可少的,因为对于下一代智能网联域控制器来说,其架构所带来的传感器数据量的变化是成指数级增加,因此,芯片内部预设足够的接口是非常必要的。基本上,我们需要SOC具备多路CANFD、PCIe、ethernet、GPIO、MIPI、UART、I2C、I2S等接口。具体情况需要根据架构来指定选用哪几路。

外部设备接口IP的种类更加丰富,我们生活中接触到的各类总线都有机会出现在系统芯片中。这其中负责承担高性能系统扩展功能的有PCI Express(CXL/CCIX)、HBI等接口标准,它们可以实现高速外设、Die-to-Die或多芯片互联的功能。目前PCI Express正在发展最新的6.0版本,而CXL已经演进到1.2版本。

另外,我们还会有一些面向特定应用需求的专门接口总线,这包括USB、SATA、MIPI、DisplayPort、HDMI、UFS和以太网等种类繁多的技术标准。这其中新一代USB4已经随着苹果采用自研M1芯片的MacBook走进了大众视野,提供最高40Gbps的传输速率。DisplayPort也在朝着2.0标准发展,并最终会以80Gbps的带宽支持多路超高清显示输出。MIPI总线也在响应移动通信、多媒体和车载应用所提出的更高要求,逐步走向多元化。

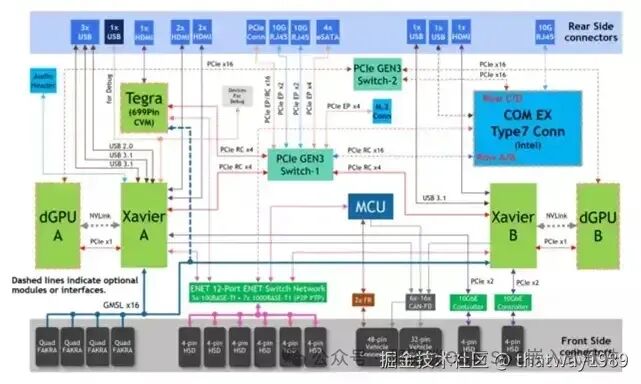

PCIE的应用:一般的应用场景中,集成一个主芯片就能够满足计算资源的需求,但是自动驾驶对算力有着更高的要求,有时候于安全的考虑,也需要同时集成多个主芯片,其结构一般如下图所示:

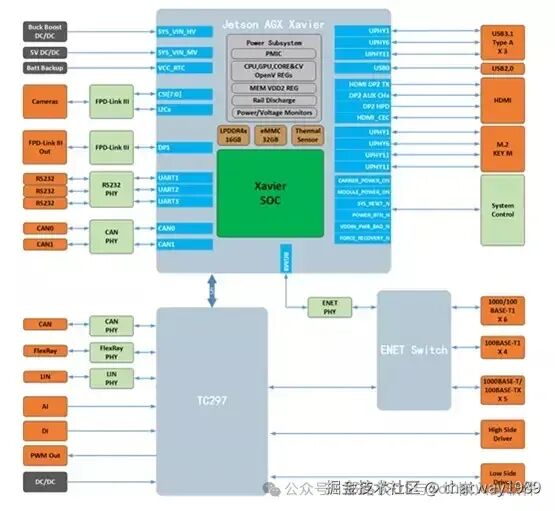

多个芯片在需要在PCIe Switch的连接下共同组成一个计算单元,如果以后发展成可动态拓展的形式(类似于刀片机),该结构依然适用,以下是采用两个Xavier芯片组成的一个高性能计算单元的示意图:

单个xavier的算力只有30TPOS,但是通过PCIE等连接方式,这样计算平台的算力明显提升,计算平台英伟达的DRIVE PX Pegasus的算力达到320TPOS,比特斯拉HW3.0的算力还大。

进一步还可以使用光纤速度更快。

3.4 NOC总线

人工智能、5G等新兴的应用场景,对芯片设计提出了更高的要求。SoC设计方法已经无法满足这些芯片的设计。随着集成电路的发展,片上网络(Network-on-Chip, NoC)作为一种全新的设计方法学很好地解决了SoC的单一总线的通信瓶颈问题。

IP复用比较好的时候,大家实现SoC的差异变小,主要就在于用了哪些IP以及如何链接****这些IP,来满足系统的要求。这就要提到NoC设计构架的差异非常重要。

NoC的优缺点:

-

优点:减少布线和片上面积,减少功耗,支持QoS,保护数据,高带宽

-

缺点:内部互连异常复杂以及串扰现象明显

3.5 RISC-V

RISC-V拥有非常丰富的生态资源,而且其软核形态是依托FPGA的,使得FPGA立即能拥有这些丰富的生态资源。经过优化的RISC-V,不单降低了对FPGA的资源消耗,还通过外设的多样性,赋予FPGA在并行算法应用中对各功能模块更快捷的调度和配置能力。FPGA擅长高性能的并行应用,加入RISC-V就可以完成多映像加载、网络协议的缝合,甚至是多个独立RISC-V集成的应用。

当前的软核RISC-V,在平台的移植性方面也非常轻松。有很多嵌入式应用,例如基于ARM Cortex M4的应用,要集成在低成本的FPGA中还有一定难度。软核的RISC-V处理器(达到450Mhz)可以跟硬核的Cortex M4处理器分庭抗礼。在性能相当的情况下,RISC-V所有总线以AXI的形式内置于FPGA,可以带来高度灵活性、快速上市时间和极低的IP集成风险等额外的价值。

3.6 信息安全

信息安全监控。主要包含数字身份认证、看门狗程序、底层安全驱动、加密引擎等几个方面。其目的是在系统运行期间实现系统的安全、认证启动或主机监测。

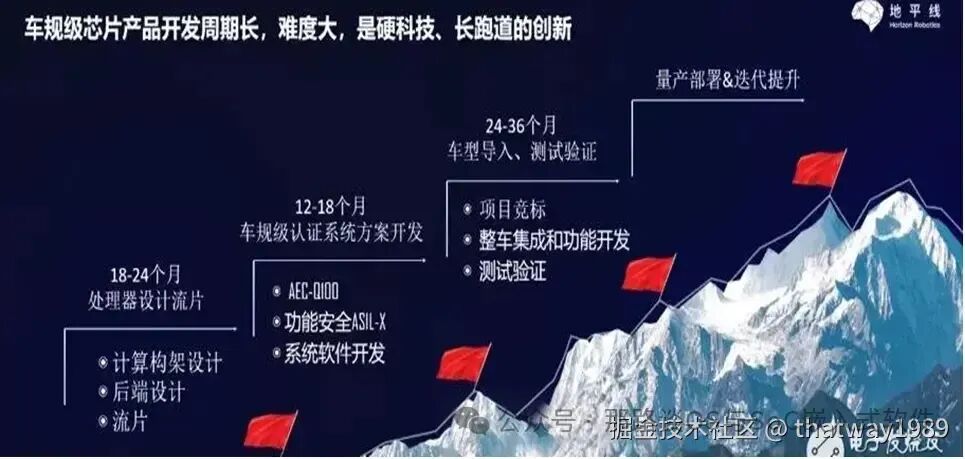

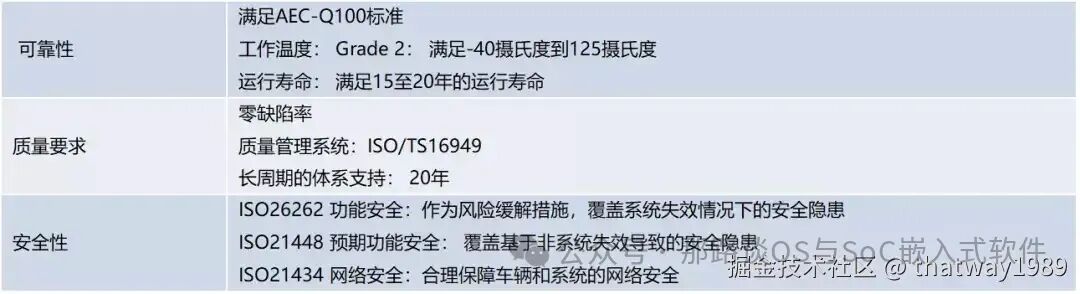

3.7 车规级功能安全

人工智能时代车规级AI芯片成为皇冠上的明珠,竞争壁垒高。由于车规级标准极难认证,车规级人工智能芯片代表了芯片行业中的最高标准,与消费级和工业级芯片相比,车规级AI芯片在安全性、可靠性和稳定性上都有最高的要求。必须要达到,车载环境温度在-40℃到125℃区间,故障率为0。

由于车规级芯片开发周期长、设计难度大,属于长跑创新,一旦建立起领先优势,龙头厂商将具有较高的竞争壁垒,人工智能时代车规级AI芯片成为皇冠上的明珠,领先厂商竞争壁垒较高。

功能安全在芯片上的设计原则是要尽可能多的找出芯片上的失效场景并纠正。失效又分为系统和随机两种,前者依靠设计时的流程规范来保证,后者依赖于芯片设计上采取的种种失效探测机制来保证。我们在这主要谈后者。简单来说,芯片的失效率,是基于单个晶体管在某个工艺节点的失效概率,推导出片上逻辑或者内存的失效概率。面积越大,晶体管越多,相应的失效率越大。

ISO26262把安全等级做了划分,常见的有ASIL-B和ASIL-D级。ASIL-B要求芯片能够覆盖90%的单点失效场景,而ASIL-D则是99%。这其实是个非常高的要求。一个晶体管的失效概率虽低,可是通常一个复杂芯片是上亿个晶体管组成的,如果不采取任何措施,那任何一点的错误都可能造成功能失效,失效率很高,这对于芯片设计来说需要增加非常多的冗余措施和开发成本,不是一蹴而就的,目前过了产品的芯片的ISO26262的功能认证的自动驾驶芯片不多,特斯拉就没有过,当然它是特独立的芯片厂家,但是我们在选择自动驾驶平台的时候需要考虑这个因素。

自动控制需要负责可靠性和车辆控制,也就是功能安全和冗余监控作用,不要求很高的算力,但是可靠性必须要有保障,ISO26262等级要求达到ASIL-D,目前用的较多的就是Infineon的TC297或者TC397,为了达到功能安全, 这部分控制的MCU可以给到符合ISO26262的英飞凌芯片做控制,自动驾驶芯片输出对应的图像或雷达处理信息,给到英飞凌的MCU去做最终的控制算法。

这一点做技术有时不能钻牛角尖了,非要搞一个多安全的芯片,要多站在系统的角度看,只要系统安全就可以了,没必要单独一个芯片有多安全。搞点冗余或者把核心部分外包给安全独立的芯片就可以,ASIL-D规则也是达到99%也不是100%,规则也没写死钻牛角尖。

这一点做技术有时不能钻牛角尖了,非要搞一个多安全的芯片,要多站在系统的角度看,只要系统安全就可以了,没必要单独一个芯片有多安全。搞点冗余或者把核心部分外包给安全独立的芯片就可以,ASIL-D规则也是达到99%也不是100%,规则也没写死钻牛角尖。

4. AI趋势

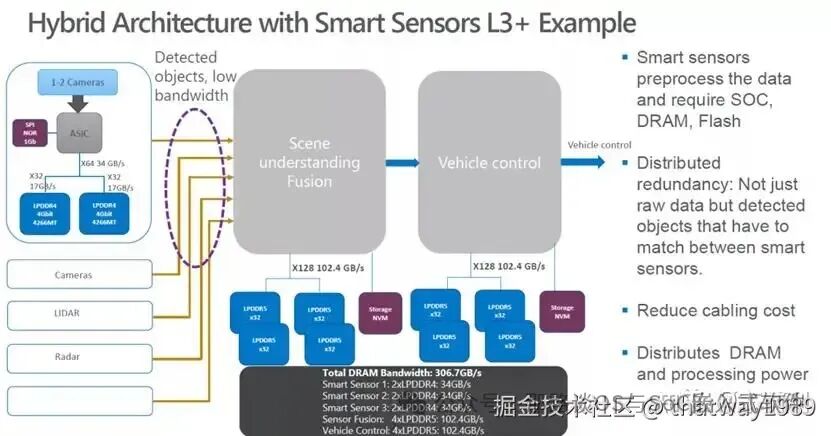

4.1 自动驾驶对DDR带宽要求

上图是目前比较主流的L3+自动驾驶的架构,从这里可以看到,摄像头那部分的处理需要的DDR的带宽是34GB/s,ASIC的DDR带宽为64bit,ADAS需要处理摄像头的raw dater,这样才是最原始的数据,不是压缩,也没有处理过的数据,这样ADAS处理起来才比较灵活,所以ADAS的带宽要求非常高。

可以看到除了要处理高清摄像头的raw dater的数据,还需要处理超声波雷达和****激光雷达的数据,这些传感器的作用是不同的,激光雷达主要用于3D建模、超声波雷达用于倒车、超车,摄像头主要用于部分ADAS功能,比如ACC自适应巡航、AEB紧急制动等等。

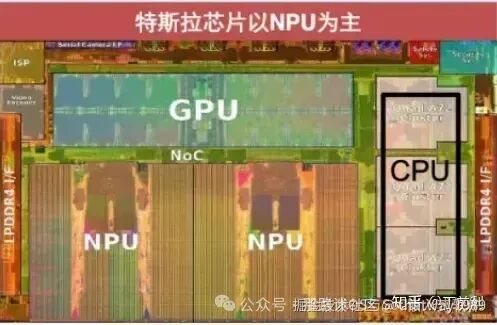

4.2 特斯拉NPU

特斯拉芯片的片上面积以NPU为主,一些通用的处理任务不适合由神经网络处理器处理、而由CPU来完成的。特斯拉解释说,芯片中有12个ARM Cortex A72 64位CPU,运行速度为2.2 GHz。

NPU对带宽要求很高,使用了昂贵的SRAM。强大的SRAM容量是其相对于其他类型芯片的最大优势之一。

人工智能中最消耗运算量的地方是卷积,就是乘和累加运算Multiply Accumulate,MAC:

y = w[0]*x[0] + w[1]*x[1] + w[2]*x[2] + … + w[n-1]*x[n-1]

w 和 x 都是向量,y 是标量。上式是全连接层****或卷积层的典型运算。

-

MACCs(乘-加操作(点积运算)):一次乘-加运算即一次乘法+一次加法运算,所以上式的 MACCs 是n。

-

FLOPS(每秒浮点运算次数),而换到 FLOPS 的情况,点积做了 2n-1 FLOPS,即 n-1 次加法和 n 次乘法。

可以看到,MACCs 大约是 FLOPS 的一半。实际就是MAC只需一个指令,一个运算周期内就可完成乘和累加。卷积运算、点积运算、矩阵运算、数字滤波器运算、乃至多项式的求值运算都可以分解为数个 MAC 指令,人工智能运算也可以写成MAC运算。

AI芯片就是简单暴力地堆砌MAC单元。

-

增加MAC数量,这是提升算力最有效的方法。而增加MAC数量意味着芯片裸晶面积即成本的大幅度增加,这也是为什么AI芯片要用到尽可能先进的半导体制造工艺。

-

除了增加数量,还有提高MAC运行频率,但是功耗也会上升。

-

提高MAC效率,不让MAC空闲空等。其中主要就是存储速度低引起。如果你的算法或者说CNN卷积需要的算力是1TOPS,而运算平台的算力是4TOPS,那么利用效率只有25%,运算单元大部分时候都在等待数据传送,特别是batch尺寸较小时候,这时候存储带宽不足会严重限制性能。但如果超出平台的运算能力,延迟会大幅度增加,存储瓶颈一样很要命。

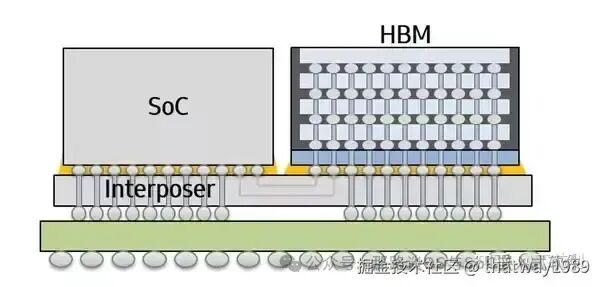

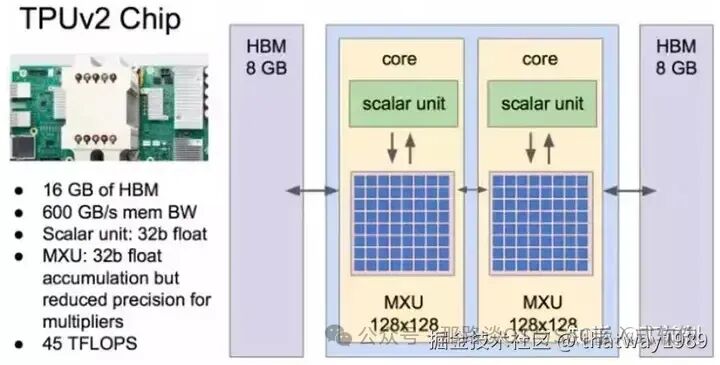

决定算力真实值最主要因素是内存( SRAM和DRAM)带宽,还有实际运行频率( 即供电电压或温度),还有算法的batch尺寸。例如谷歌第一代TPU,理论值为90TOPS算力,最差真实值只有1/9,也就是10TOPS算力,因为第一代内存带宽仅34GB/s。而第二代TPU下血本使用了HBM内存,带宽提升到600GB/s(单一芯片,TPU V2板内存总带宽2400GB/s)。

提高系统存储效率最为有效的方法还是减小运算单元与存储器之间的物理距离。CPU与HBM2之间通过Micro-bump连接,线宽仅为55微米,比传统的板上内存或者说off-chip内存要减少20倍的距离。可以大大缓解内存瓶颈问题。

另外退而求其次的方法是优化指令集,尽量减少数据的访存,CNN算法会引入大量的访存行为,这个访存行为的频繁度会随着参考取样集合的增加而增加(原因很简单,缓存无法装下所有的参考取样,所以,即便这些参考取样会不断地被重复访问,也无法充分挖掘数据本地化所带来的cache收益)。针对这种应用类型,实际上存在成熟的优化范式——脉动阵列:让数据尽量在处理单元中多流动一会儿。

除了降低精度以外,还可以结合一些数据结构转换来减少运算量,比如通过快速傅里叶变换(FFT)变换来减少矩阵运算中的乘法;还可以通过查表的方法来简化 MAC 的实现等。

对于使用修正线性单元(ReLU)作为激活函数的神经网络,激活值为零的情况很多 ;而在对神经网络进行的剪枝操作后,权重值也会有很多为零。基于这样的稀疏性特征,一方面可以使用专门的硬件架构,比如 SCNN 加速器,提高 MAC 的使用效率,另一方面可以对权重和激活值数据进行压缩。

4.3 谷歌TPU

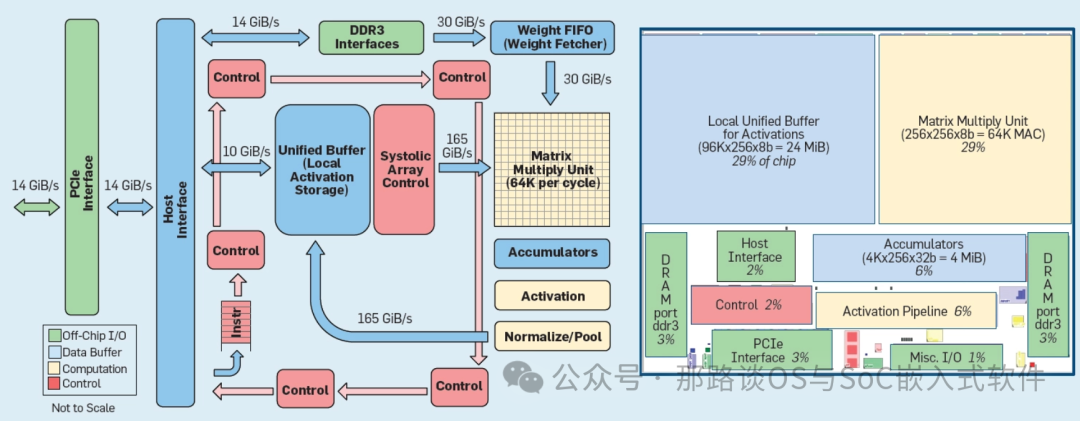

这是Google的TPU。从上边的芯片框图可以看到,有一个64K的乘加MAC阵列对乘加运算进行加速。从论文中可以看到里面已经用到了脉动阵列的架构方法来对运算进行加速,另外也有我们前面提到的大量的片上Memory 这样的路径。上面蓝色框图中大家可以看到有一个24MiB的片上Memory,而且有两个高速DDR3接口能够与片外的DDR做交互。

上图展示的第二代TPU。从图中可以很直观的看到,它用到了我们前面所说到的HBM Memory。从其论文披露的信息也可以看到,二代TPU在第一代的基础上增加了我们前面说到的剪枝,权重压缩等方面做了很多尝试,也是一个非常经典的云端AI加速芯片的例子。

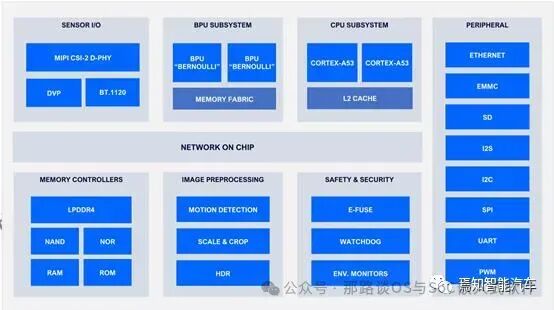

4.5 地平线BPU

地平线的BPU内承载了进行神经网络运算的积累加运算(英语:Multiply Accumulate, MAC)单元。通过应用MAC 指令,可以使的乘加运算用一个指令完成。而许多运算(例如卷积运算、点积运算、矩阵运算、数字滤波器运算、乃至多项式的求值运算)都可以分解为数个MAC 指令,因此可以提高上述运算的效率。

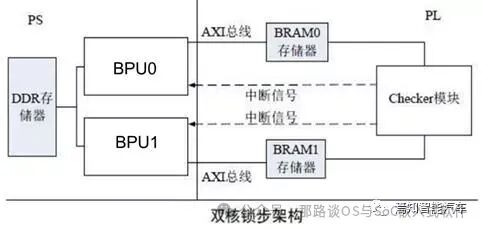

地平线的BPU采用双核的结构,同时在其控制单元里跑两套相同的程序,并对对方运算结果进行相互校验,由检查器模块对比两个BPU应用程序的执行输出,在输出结果一致的情况下,由检查器模块产生中断,将两个BPU当前状态以检查点文件的形式保存到存储器上,在输出结果不一致的情况下,由检查器模块产生中断,两个CPU处理器调取最近一次保存的检查点文件实施回卷以恢复系统进行重新计算。这一过程类似于实现了BPU内的锁步功能,这样可以很大程度上提升其运算结果的准确性,确保其SOC的功能安全性能。

功能安全岛高性能自动驾驶芯片需要在多核架构上承载功能安全拆解的功能目标值,其中包括在软错误发生后,可以及时的进行错误纠正,将系统恢复到安全状态。这就要求在多核系统上实现一定的软硬件的功能安全设计目标。通常情况下,各个芯片厂家会倾向于纳入功能安全岛来作为实现芯片功能安全的机制。从原理上分析,功能安全岛可划分为硬件锁步,软件分区的方式来进行功能安全目标提升。

所谓硬件锁步,就是在芯片设计中同时搭载两套硬件内核,每个内核分别承载两套相同的软件模型,当输入源相同时,则实现了两个硬件内核的相同运算机制,同时该过程需要保持两个运算核的独立性,其运算的结果将会在每个周期都进行一次比较,当出现差异时,生成一个trap,该trap触发一个中断,将两个锁步核中运行状态以文件行驶保存在存储器上,并调用最近一次保存的文件回卷以恢复系统重新进行计算。整个过程相当于不断进行自检与互检的过程。

所谓软件分区,其目的是确保程序的并行运行和安全计算能力。其过程是根据软件的可并行性核相关安全架构,将上层软件模块分配给AUTOSAR中定义的操作系统应用程序执行相应的作业Task,且该过程需要确保ECU在运行时不会引起内部区域之间的相互干扰。片上网络由于SOC中的处理器采用了多MIPS 处理核心,每个核心拥有私有的指令缓存(I-Cache)和数据缓存(D-Cache)。片上网络,本质上是为了解决片上多核系统中不同的核心之间,核心与非核心(Un-Core)硬件单元之间数据传输问题的一种“片上通信”方案。

图像/视频处理单元SOC芯片上的图像处理单元主要包括几个部分功能:数字图像信号处理、图像分割(Pyramid)、图像拼接(Stitch)、图像渲染(GDC)以及视频编解码功能。

ISP模块接收感光元件(Sensor)的原始信号数据,并处理图像传感器输出的图像信号,对图像质量起着非常重要的作用。ISP内部包含多个图像算法处理模块,其中主要包含如下几种:

-

通过扣暗电流去掉底电流噪声;

-

通过线性化解决数据非线性问题;

-

解决镜头带来的亮度衰减与颜色变化;

-

通过去坏点,剔除sensor中坏点数据);

-

通过数字图像滤波进行图像去噪;

-

通过感光半导体处理将原始环境光源数据转为RGB数据;

-

自动白平衡,自动对焦,自动曝光

-

亮度映射曲线,优化局部与整体对比度

此外,ISP的处理过程还包括如下几个部分:**即旋转(角度变化),锐化(调整锐度),缩放(放大缩小),色彩空间转换(转换到不同色彩空间进处理),颜色增强(可选,调整颜色),肤色增强(可选,优化肤色表现)**等。

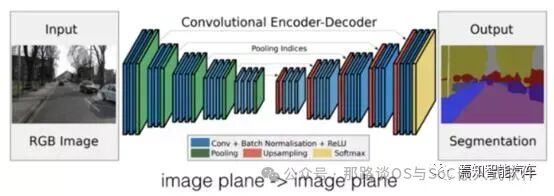

图像分割实在神经网络处理逻辑之前进行简单的场景分割,将环境中明显可表达的语义进行分别输出。图像拼接是针对有一定overlap的图像进行全场景范围拼接,拼接的结果主要用于流媒体显示。

此外,图像处理单元一版还会额外搭载一些视频编解码核,一般可应用HEVC的方式进行编解码。更为强大的图像/视频处理单元会有能力进行3D图像渲染。这一部分可能会用到GPU的相关计算能力。这里需要说明一下的是,在我们设计域控制器的时候,很多情况下,我们选择的SOC芯片是不具备足够的3D渲染能力的,这时,从整个先进的显示方案需求出发,我们就需要采用额外的处理器进行渲染。这里有两种方案:其一,是采用驾驶域控制器的芯片扩充方案,即在自动驾驶域控制器AI芯片外围在增加相应的GPU芯片进行集成,两者可通过PCIe进行图像传输。其二,是采用座舱域控制器芯片扩充方案,即在智能座舱控制器芯片中集成GPU处理能力的芯片直接做渲染和显示。

4.6 AI视觉方案

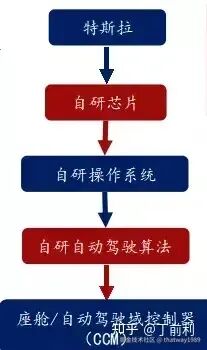

特斯拉的自研模式很有价值,可以垂直整合做到更高效的利用软硬件资源来实现更先进的技术和性能,而且不受外部很多规范规则限制。

-

摄像头就传感器,收集视频画面

-

再进行后续图像分割、物体分类、目标跟踪、世界模型、多传感器融合、在线标定、视觉SLAM、ISP 等一系列步骤进行匹配与深度学习

图像接口和图像处理能力

a)图像接口CSI:

CSI作为前端-配置逻辑接口,可以支持大多数通用的可用的CMOS摄像头接口,支持方便YCC,YUV,Bayer或者是RGB的数据格式输入,完全可控的8-bit或16-bit数据到32-bit的FIFO进行打包,32*32大小的FIFO存储接受到的的图像像素数据,该FIFO可以通过可编程的IO或者是DMA进行读取。

后端-提供了直接到eMMA的预处理PrP块接口(PrP和PP组成了MX27图形加速器eM MA,PrP和PP能够用来给视频做预处理和后期处理,例如,放大,缩小,颜色转换)。提供sensor的可屏蔽中断源,该中断源也是中断可控的,提供给外部sensor用的,可配置的主时钟频率,由统计数据产生的自动曝光(AE)和自动白平衡(AWB)控制。

b)视觉处理芯片ISP

ISP作为视觉处理芯片核心,其主要功能包括AE(自动曝光)、AF(自动对焦)、AWB(自动白平衡)、去除图像噪声、LSC(Lens Shading Correction)、BPC(Bad PixelCorrection),最后把Raw Data 保存起来,传给videocodec 或CV 等。通过ISP 可以得到更好的图像效果,因此在自动驾驶汽车上对ISP的要求很高,比如开始集成双通道甚至三通道的ISP。

一般来说ISP 是集成在AP 里面(对很多AP 芯片厂商来说,这是差异化竞争的关键部分),但是随着需求的变化也出现了独立的ISP,主要原因是可以更灵活的配置,同时弥补及配合AP 芯片内ISP 功能的不足。

c)图像绘制芯片GPU:

GPU是基于大的吞吐量设计,用来处理大规模的并行计算。GPU的控制单元可以把多个的访问合并成少的访问。GPU将更多的晶体管用于执行单元,而非像CPU那样用作复杂的数据cache和指令控制。由于GPU具有超强的浮点计算能力,可用于在智能汽车前端的图像或视频处理领域的应用,也越来越多地应用在中央控制器高性能计算的主流设计中。

4.7 AD(自动驾驶控)的算力分配

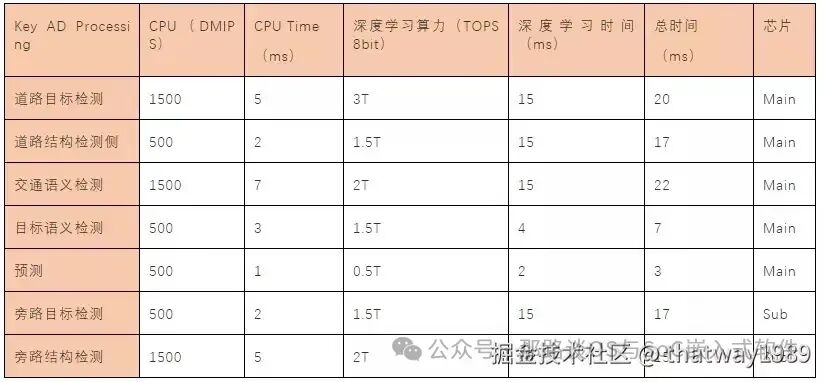

自动驾驶控制器的整个ECU资源需要在其具体的算法控制中得到算力分配,其中关键的AD处理过程包括如下主要的几个部分。道路运动目标检测、道路结构检测(基于前视摄像头)、目标形态检测、预测分析、道路结构检测(基于侧视摄像头)、道路运动目标检测(基于侧视摄像头)。各部分参数主要包括了对CPU运行资源、算力、运行带宽、运行时间等,如下表表示了一种典型的各个算法对于算力运行占用的资源统计分析,其中两个不同的芯片分别暂用不同计算需求。

如上软件模块算法的算力效率牵涉到MAC计算效率问题。如果相应的自动驾驶模块算法或者说CNN卷积需要的算力是1TOPS,而运算平台的算力是4TOPS,那么利用效率只有25%,运算单元大部分时候都在等待数据传送,特别是批量待处理的尺寸较小时候,存储带宽不足会严重限制性能。但如果超出平台的运算能力,延迟会大幅度增加,存储瓶颈一样很要命。效率在90-95%情况下,存储瓶颈影响最小,但这并不意味着不影响了,影响依然存在。然而平台不会只运算一种算法,运算利用效率很难稳定在90-95%。

5. AI芯片的NPU发展趋势

5.1 并行计算

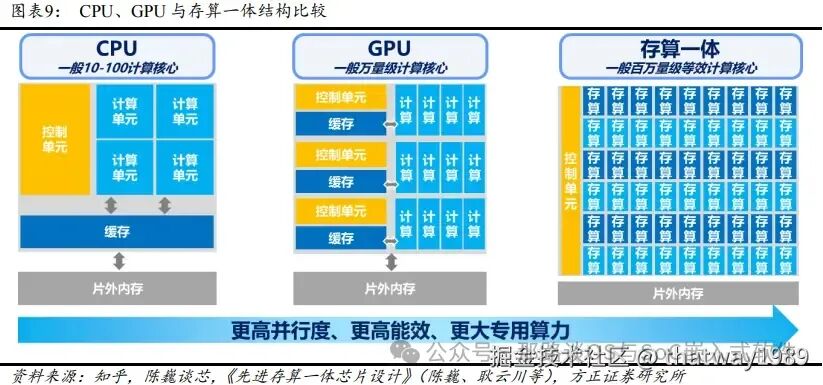

芯片中的AI Core数量会不断增加,来实现并行计算。并且需要近存加快计算速度。

并行分布式计算,就是利用网络把计算任务分发到不同的处理单元上,并且处理单元有自己的一些存储及附属配件来提供服务。

这样就不是CPU那样集中式的存储和计算,在SoC的NPU中,就会分散到不同的核和存储。NPU计算单元跟存储单元在芯片布局上是在一块的,这样距离近,速度快。

广播对并行处理很重要

对于多个处理单元,不能一个一个的给数据和控制信号,太慢了,不利于并行处理,需要这些处理单元几乎同时拿到数据,不是自己的可以丢弃,但是自己的就必须第一时间拿到并进行处理,虽然设计上有硬件的浪费,但是为了快速软件都可以硬化,其实就是用成本来提高了运行速度。

为了让NPU中的大量PE并行,数据总线和控制总线都需要设计为环线,就像一条环形的大路,路两边均匀分布不同的存储和运算单元,可以进行广播给各个存算一体的处理单元。

并行要用到两个概念SIMD和MAC,下面介绍下:

什么是SIMD?

SIMD(Single Instruction Multiple Data,单指令多数据)是一种并行处理技术,它允许处理器在一个周期内对多个数据执行相同的指令。这种技术特别适合于神经网络等需要大量并行计算的应用场景。在NPU中,通过一维MAC来实现SIMD的并行处理,可以显著提高计算效率。

什么是MAC?

MAC(Multiply-Accumulate,乘累加)运算是指执行两个数的乘法,并将结果累加到一个累加器上的操作。在神经网络中,尤其是深度神经网络中,大量的计算涉及到矩阵乘法和向量加法,这些操作都可以通过MAC运算来实现。

5.2 存算一体

并行计算需要立即拿到数据和指令,传统的CPU架构指令到达时去找数据,这时候数据可能在cache立即拿到也可能不在cache里面,在DDR里面,或者在Flash、硬盘里面等,充满了不确定性,这时候就比较耗时了,本来并行就需要协同处理,一个并行子任务就可能卡住整个计算的队列,就像流水线,一个充满不确定性的工人歇了,其他人就干瞪眼,充满了不确定性,对应一个高效的系统是不可容忍的,宁可以多分配资源也要保证高效运算。当然不使用cache,保证了确定性,代价也是很大的。cache就是花小钱办大事也可能办不成,但是100%办成就需要花大钱才能办大事了。需要很大的SRAM,然后把需要的数据100%的进行搬运,有需要强调的调度核软硬件和DMA硬件的加入。有了存算一体的确定性,就可以衍生出一系列基于编译器的调度技术,可以更加确定的对任务进行分割,因为信赖硬件会按照顺序不卡壳的运行。虽然硬件有设计冗余但是调度器会榨干这些分布式计算单元的性能,有活就直接把性能榨干到100%。传统CPU架构虽然硬件上更精简但是处理的是复杂任务,经常平均性能可能不到10%。所以应用场景的不同,需要对应不同的硬件设计,在SoC上各种系统都存在就需要把不同的计算任务分配到不同的硬件上,再进行系统级的协同工作。为了保障存算一体数据的确定性,保障计算单元能准确的时间内拿到存算一体数据,需要有一个同步机制。这样就保证了系统中知道某个时间数据在哪里,数据的运动情况,数据到新位置后需要同步机制知道数据的新位置。具体就是数据到了计算单元就同步给计算单元开始运算,计算单元运算完结果放入存储就同步告诉调度器数据返回给AI APP。

并行计算需要立即拿到数据和指令,传统的CPU架构指令到达时去找数据,这时候数据可能在cache立即拿到也可能不在cache里面,在DDR里面,或者在Flash、硬盘里面等,充满了不确定性,这时候就比较耗时了,本来并行就需要协同处理,一个并行子任务就可能卡住整个计算的队列,就像流水线,一个充满不确定性的工人歇了,其他人就干瞪眼,充满了不确定性,对应一个高效的系统是不可容忍的,宁可以多分配资源也要保证高效运算。当然不使用cache,保证了确定性,代价也是很大的。cache就是花小钱办大事也可能办不成,但是100%办成就需要花大钱才能办大事了。需要很大的SRAM,然后把需要的数据100%的进行搬运,有需要强调的调度核软硬件和DMA硬件的加入。有了存算一体的确定性,就可以衍生出一系列基于编译器的调度技术,可以更加确定的对任务进行分割,因为信赖硬件会按照顺序不卡壳的运行。虽然硬件有设计冗余但是调度器会榨干这些分布式计算单元的性能,有活就直接把性能榨干到100%。传统CPU架构虽然硬件上更精简但是处理的是复杂任务,经常平均性能可能不到10%。所以应用场景的不同,需要对应不同的硬件设计,在SoC上各种系统都存在就需要把不同的计算任务分配到不同的硬件上,再进行系统级的协同工作。为了保障存算一体数据的确定性,保障计算单元能准确的时间内拿到存算一体数据,需要有一个同步机制。这样就保证了系统中知道某个时间数据在哪里,数据的运动情况,数据到新位置后需要同步机制知道数据的新位置。具体就是数据到了计算单元就同步给计算单元开始运算,计算单元运算完结果放入存储就同步告诉调度器数据返回给AI APP。

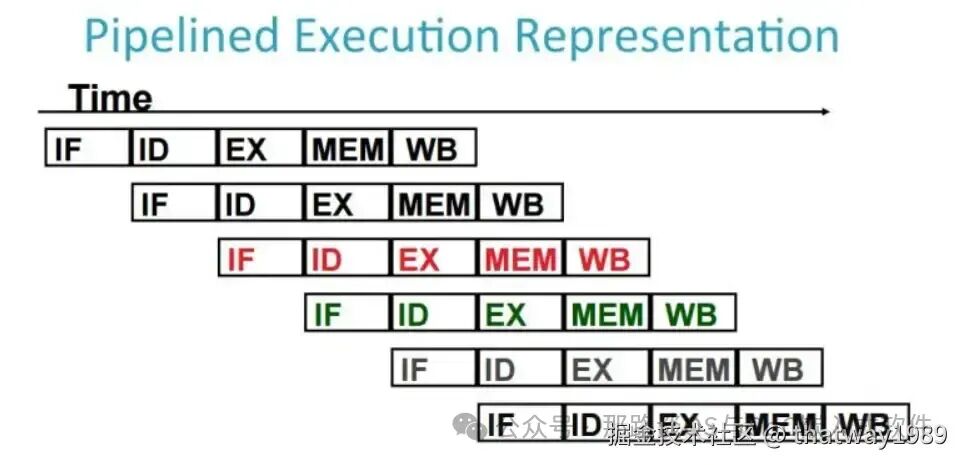

5.3 流水线

NPU中有各种各样的算子,对于一个计算任务可以进行分解并行计算,但是有些还是有依赖的串行才能操作,就存在某个时刻会空出来一些算子闲置没有进行运算工作,但是这些算子都是硬件,闲置就闲置了,所以整个NPU算子利用率从理论上也达不到100%,但是我们要通过调度策略尽量让算子去并行执行,来提高利用率。

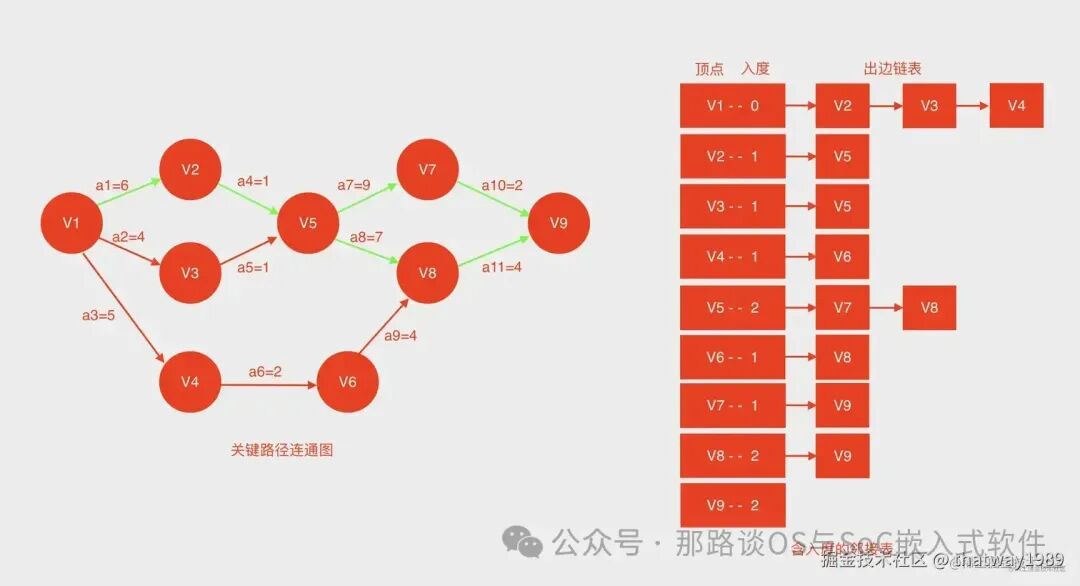

可以把上图中的一个圈看成一个算子,那第二列是依赖第一列的,但是第一列不是一次就可以计算完,例如第一列需要100个计算,但是一次只计算了10个,这时第一列中的100个计算其中2个有了第一列的10个计算输入就可以进行计算了,就可以并行开始工作了。这其中就是串行中有并行,并行中有串行,都是相对的。跟数据结构里面的关键路径算法非常类似:

关键路径是指工程项目从开始到结束经过的耗时最长的逻辑路径,因此优化关键路径是一种提高工程项目有效方法。

关键路径基于拓扑排序,且引出了以下四个概念。

Ve(j):表示事件(顶点)的最早开始时间,在不推迟整个工期的前提下,表示从源点开始到该节点的需要的最长时间

Vl(j):表示事件(顶点)的最晚开始时间,在不推迟整个工期的前提下,表示从结束顶点到该点最短需要多少时间

e(i):表示活动(边)的最早开始时间,就是活动边的起点的最早发生时间, 表示该边起点的最早开始时间

l(i):表示活动(边)的最晚开始时间,就是该活动边起点的最晚发生时间,表示该边起点的最晚开始事件

这四个概念后面分别用顶点最早开始时间、顶点最晚开始时间、活动最早开始时间、活动最晚开始时间表示。

详细算法可以自己去搜这个关键路径算法。这里关键路径就是工程项目所用的最短时间,工程里面会去优化这个关键路径,缩短关键路径就可以缩减工期。跟我们这里串行并行的这些是一样的,算出来整个任务最短运行的时间,并进行优化,才能进行并行任务分配。

串行的算子之间由于是存算一体的实现,数据不必传出去到cache或者DDR,直接在NPU内部的算子之间流转,距离近,效率高。所以并行要从存储(存算一体数据)和计算(算子)两个维度去进行。

之前讲过算子的概念,其可大可小,大的来说可以对于一个NPU计算核心,小的来说可以针对一个计算核心里面的例如一个TCC张量运算单元,这里面都有并行的概念。就是需要在各个层级上去进行并行,整体并行,火力全开。

参考:https://juejin.cn/post/6901966187392385037

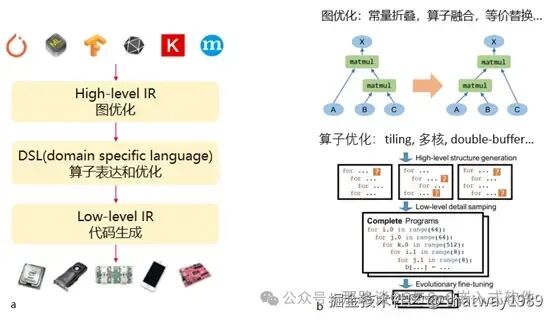

5.4 图编译器

上面的NPU并行的思想机制,其实都需要软件去实现,硬件的NPU只是计算和存储的功能,怎么用这些功能需要软件去调度去发指令。特别是并行处理,就需要编译器去分割任务并分配硬件资源,这样处理就像流水线一样,让数据流动起来,最大化利用硬件,这就是数据流芯片框架的软件实现。

调度的核心就是图依赖

并行计算中的依赖就像关键路径里面的图表达一样,这里也需要把这个图给抽象描绘出来,再使用软件算法进行规划,最后参与编译生成固定序列的运行指令,这就是图编译器的作用。

能做到编译的时候,而不是运行时进行任务调度是因为业务场景的固定,例如智能驾驶,固定的处理图片视频数据,固定的业务。

其实上面用到的流水线、数据结构等都是一些计算机体系结构最基础的知识,组合到一块,又有具体的应用场景就是创新了。

另外在具体的实现上,硬件还可以,软件上的实现可能比这些思想要复杂千万倍,需要进行分模块,大量的人员投入去梳理清楚业务变为代码。

从计算机技术的发展来看

计算机技术的一些核心思想感觉已经老早被一些聪明人发明出来了(本科阶段就可以学习到,例如计算机组成原理、数据结构、计算机网络、操作系统等),其实就是模拟人的思维,人的思维就那些都被用完了,现在的创新就是这些模式的组合也就是体系结构的变化,还有就是芯片制造工艺的提升,来增加技术能力。

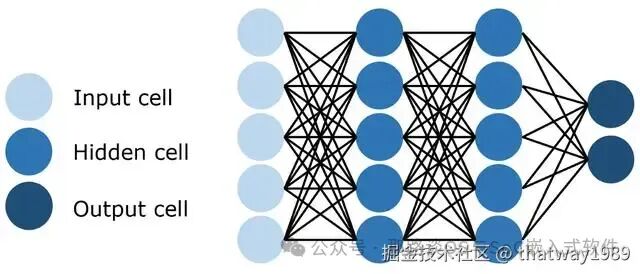

5.5 编程模型

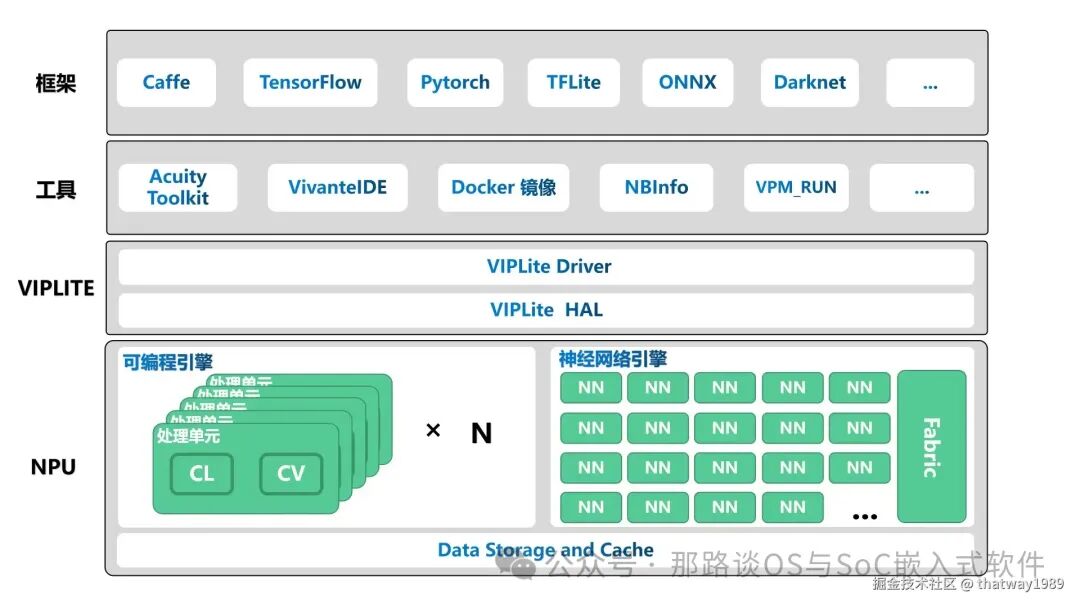

NPU (NeuralNetworks Process Units)神经网络处理单元。其针对于矩阵等运算进行了专门的优化设计,解决了传统芯片在神经网络运算时效率低下的问题。NPU工作原理是在电路层模拟人类神经元和突触,并且用深度学习指令集直接处理大规模的神经元和突触,一条指令完成一组神经元的处理。相比于CPU和GPU,NPU通过突出权重实现存储和计算一体化,从而提高运行效率。

神经网络处理器(NPU)采用“数据驱动并行计算”的架构,特别擅长处理视频、图像类的海量多媒体数据。NPU处理器专门为物联网人工智能而设计,用于加速神经网络的运算,解决传统芯片在神经网络运算时效率低下的问题。

NPU是模仿生物神经网络而构建的,CPU、GPU处理器需要用数千条指令完成的神经元处理,NPU只要一条或几条就能完成,因此在深度学习的处理效率方面优势明显。

神经网络中存储和处理是一体化的,都是通过突触权重来体现。冯·诺伊曼结构中,存储和处理是分离的,分别由存储器和运算器来实现,二者之间存在巨大的差异。当用现有的基于冯·诺伊曼结构的经典计算机(如X86处理器和英伟达GPU)来跑神经网络应用时,就不可避免地受到存储和处理分离式结构的制约,因而影响效率。这也就是专门针对人工智能的专业芯片能够对传统芯片有一定先天优势的原因之一。

对于编程来说,NPU的挑战更大,需要极强的程序控制能力。NPU把自己的硬件:计算单元和存储单元都暴露给软件去控制,整个并行的组织和执行都需要软件去协调,增加了编程的复杂度,降低了软件的灵活性和通用性。所以其必须用于特定的场景才变的可控。数据和算法都必须是确定的,这样配合AI APP、runtime及调度器和编译器等一起完成这个巨大的软件工程。

这里就是随着硬件的体系结构变的复杂,软件的复杂度也随着上升。NPU硬件中随处可见的DMA、SRAM、RISC-V、算子等,这些需要一个庞大的软件及编译器去控制,work起来。

后记:

本文汇总了一些资料,总体上有点杂乱,而且概括度比较高,但是已经紧跟目前AI SoC设计的一些热点,希望有些参考作用。

这个系统的文章其实都比较虚,因为都是文字,不像“Show me the code”,但是其实现过程现在软硬件也都是去coding,硬件写RTL,软件写OS+应用代码,但是要入门还是先看看这些文字内容。

参考:

-

系统级芯片(SoC)的复杂设计选择:内核、IP、EDA和NoC—易灵思

-

自动驾驶主流芯片及平台架构(二)特斯拉自动驾驶芯片平台介绍–阿宝说车

-

自动驾驶主流芯片及平台架构(二)

-

自动驾驶主流芯片及平台架构(一)–阿宝说车

-

自动驾驶域控芯片内部架构与性能影响

“啥都懂一点,啥都不精通,

干啥都能干,干啥啥不是,

专业入门劝退,堪称程序员杂家”。

欢迎各位有自己公众号的留言:申请转载!

纯干货持续更新,欢迎分享给朋友、点赞、收藏、在看、划线和评论交流!

公众号:“那路谈OS与SoC嵌入式软件”,欢迎关注!

个人文章汇总:https://thatway1989.github.io

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献56条内容

已为社区贡献56条内容

所有评论(0)