一文看懂DFT Memory Repair技术

在现代SoC芯片中,存储器(Memory)通常占据芯片面积的50%以上,某些高性能芯片甚至达到70%-80%。随着工艺节点不断缩小到7nm、5nm乃至3nm,存储器密度越来越高、单元尺寸越来越小,缺陷出现的概率呈指数级上升。哪怕是最成熟的工艺,也无法保证 100% 的存储单元完美无缺。光刻偏差、材料杂质、晶圆级工艺波动,都可能导致存储器出现固定型故障、耦合故障、地址译码故障等问题。

据统计,在先进制程下,约有20%-30%的芯片因存储器缺陷而被判为废品。如果没有修复技术,只要有一个存储单元失效,整片芯片就会被判定为废品,这将直接导致良率暴跌、生产成本翻倍,尤其是对于 AI 芯片、车规级芯片这类集成了海量SRAM的产品,损失更是不可估量。

关键数据

• 存储器占SoC面积:50%-80%

• 因存储器缺陷导致的废品率:20%-30%

• 采用BISR技术后可修复比例:>90%

• 修复后良率提升:15%-25%

一、Memory Repair技术概述

1.1 什么是Memory Repair?

Memory Repair(内存修复)是一种在芯片制造测试阶段检测并修复存储器缺陷的技术。其核心思想是在存储器设计中预留“冗余”(Redundancy)资源——额外的备用行(Spare Row)和备用列(Spare Column)

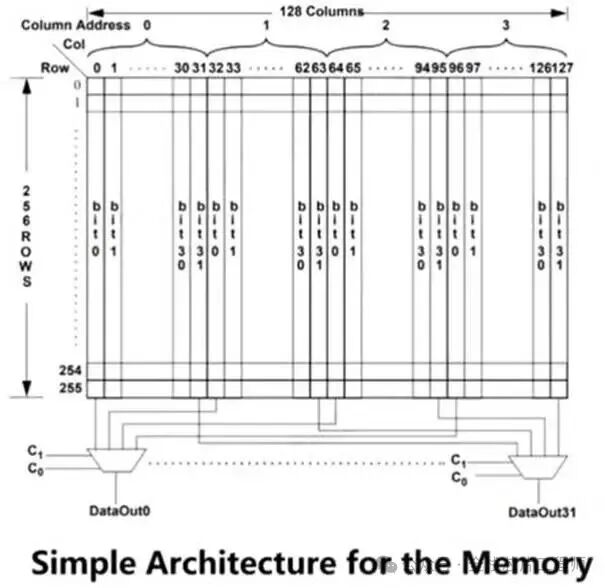

基础存储器阵列与 Column MUX 架构示意图

当检测到存储单元故障时,用这些冗余资源替换故障单元,从而使芯片恢复正常功能。而这个过程最严苛的要求,就是时序收敛:替换路径的延迟必须与原始路径完全一致,否则会导致建立 / 保持时间违例,反而引发芯片功能失效 —— 这也是 Memory Repair 设计中最核心的技术难点之一。

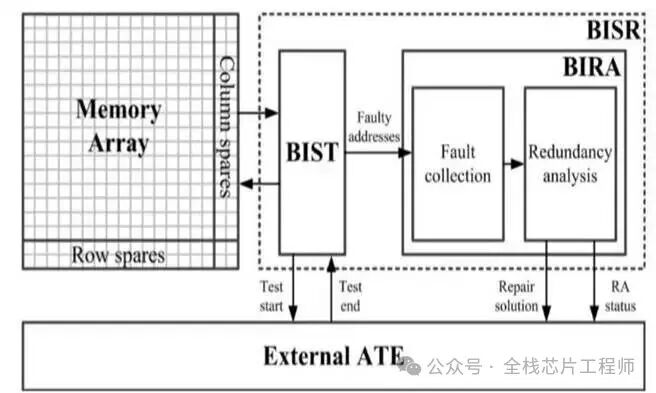

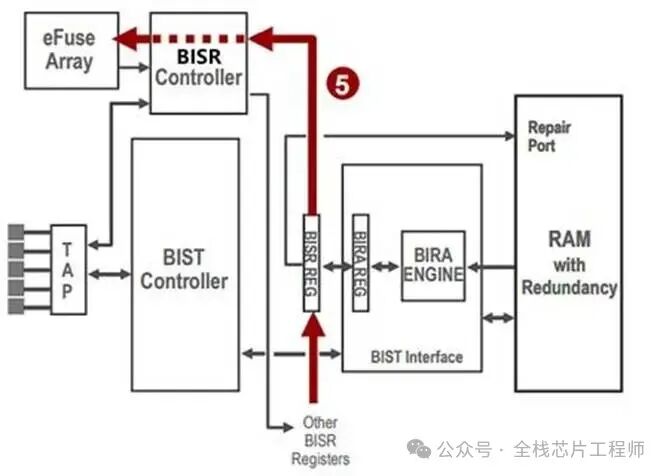

图1:典型BISR架构框图

Memory Repair主要分为两种类型:

|

特性 |

硬修复(Hard Repair) |

软修复(Soft Repair) |

|

存储介质 |

eFuse / 激光熔丝 |

SRAM / 寄存器 |

|

持久性 |

永久 |

掉电丢失 |

|

修复时机 |

制造阶段 |

每次上电 |

|

适用场景 |

量产芯片 |

原型验证 |

1.2 Hard Repair(出厂固化的永久修复)

Hard Repair 是芯片量产阶段最核心的修复方式,它的修复信息会被烧录到 eFuse(电子熔丝)、反熔丝等非易失性存储介质中,掉电后不会丢失,一次烧录,终身生效。

它的核心流程是:晶圆测试阶段,通过 ATE(自动测试设备)触发 MBIST测试,定位所有故障单元,BIRA 模块计算出最优修复方案,然后通过高压脉冲将修复签名烧录到芯片的 eFuse 阵列中。芯片每次上电后,BISR 控制器会自动从 eFuse 中读取修复信息,加载到修复寄存器中,完成地址重映射。

这种模式的优势是稳定可靠、不占用额外的启动时间,适合修复芯片制造过程中产生的永久性物理缺陷,也是目前量产阶段的主流修复方案。

1.2 Soft Repair(全生命周期的动态修复)

Soft Repair 的修复信息不会被永久固化,通常存储在 SRAM 配置寄存器或外部非易失性存储器中,芯片每次上电复位后,都需要重新加载或重新计算修复信息。

它的核心价值,在于应对芯片使用过程中出现的新增故障 —— 比如车规级芯片在高温、振动环境下的老化失效,航天芯片在太空辐射环境下出现的单粒子翻转故障,这些使用阶段产生的新缺陷,无法通过出厂时的 Hard Repair 提前修复,而 Soft Repair 可以通过上电时重新执行 MBIST+BIRA 流程,动态更新修复方案,实现 “边用边修”。

当然,Soft Repair 也有局限性:它会增加芯片的启动时间,同时需要更复杂的控制电路,因此在实际应用中,通常会采用“Hard+Soft” 的组合方案 —— 出厂时用 Hard Repair 固化制造缺陷,运行中用 Soft Repair 应对新增故障,兼顾可靠性与全生命周期的可用性。

1.2 修复的基本原理

存储器修复的基本原理可以用“地址重映射”来理解:

Step 1:检测阶段— 通过MBIST(Memory Built-In Self Test)检测存储器中的故障单元

Step 2:分析阶段— BIRA(Built-In Redundancy Analysis)模块分析故障分布,制定最优修复方案

Step 3:修复阶段— 将故障地址映射到冗余资源,实现物理替换

Step 4:存储阶段— 将修复信息写入eFuse(电子熔丝),永久保存

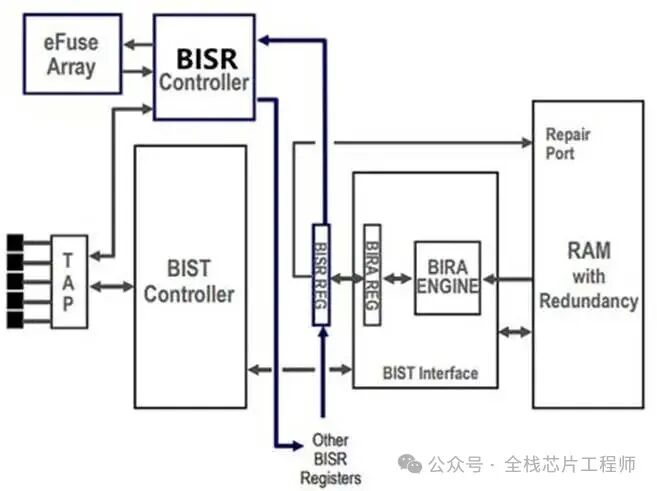

二、核心技术:MBIST、BIRA与BISR

2.1 MBIST:内存自测试

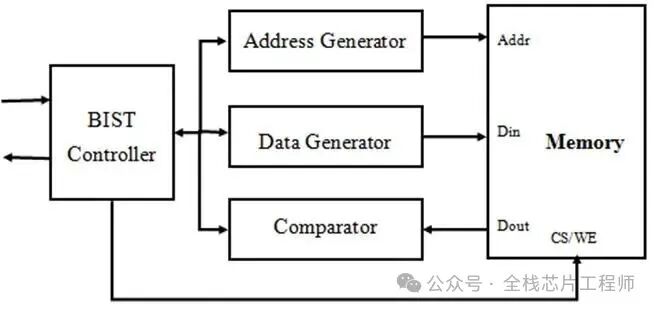

MBIST(Memory Built-In Self Test,内存内建自测试)是Memory Repair的第一步。它在芯片内部集成测试电路,自动生成测试向量并分析测试结果,无需外部测试设备即可完成存储器测试。

图2:MBIST控制器结构

MBIST常用的测试算法包括:

▸Checkerboard算法:检测相邻单元间的短路和漏电故障

▸March算法:最广泛使用的算法,可检测 stuck-at、transition、coupling等多种故障

▸SMarchCKBD算法:工业界常用,结合Serial March和Checkerboard的优势

2.2 BIRA:冗余分析引擎

BIRA(Built-In Redundancy Analysis,内建冗余分析)是Memory Repair的“大脑”。它接收MBIST传来的故障信息,根据预设的冗余分析算法,计算出最优的修复方案。

BIRA需要解决的核心问题是:

冗余分析核心问题

1. 如何用有限的冗余资源修复最多的故障?

2. 行修复和列修复如何组合最优?

3. 多个存储器如何共享冗余资源?

4. 修复方案是否可行(Repairable)?

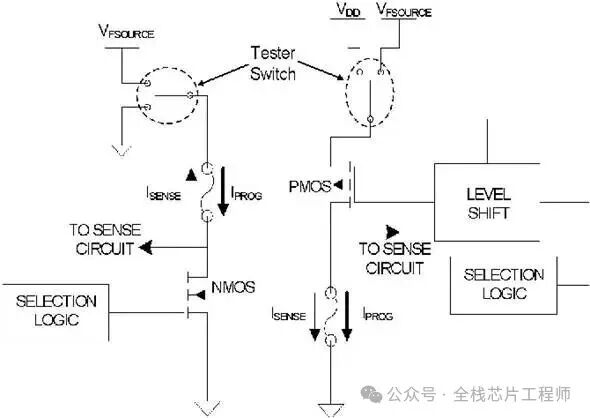

2.3 BISR:自修复实现

BISR(Built-In Self Repair,内建自修复)是Memory Repair的执行环节。它根据BIRA生成的修复方案,将修复信息写入eFuse,并在芯片上电时自动加载修复配置。

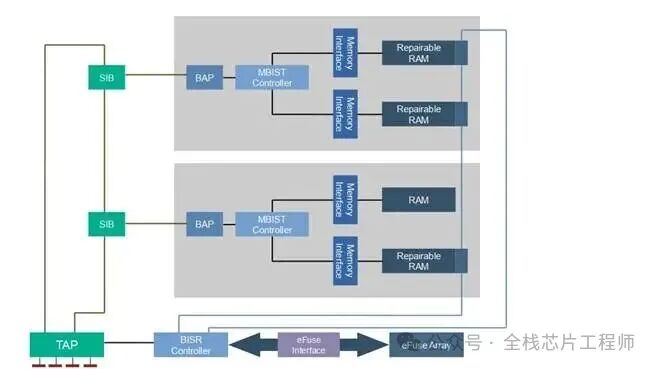

图3:BISR修复架构与Fusebox接口

三、eFuse:修复信息的永久存储

3.1 什么是eFuse?

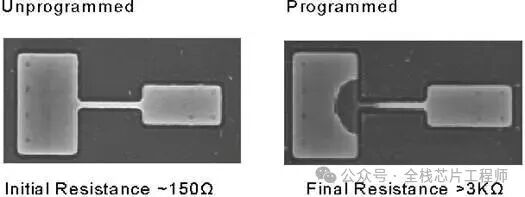

eFuse(Electrically Programmable Fuse,电子可编程熔丝)是一种一次性可编程的非易失性存储器。它通过施加高电压熔断金属熔丝来存储数据,一旦熔断便不可恢复,因此适合存储最终的修复信息。

图4:eFuse电路原理图

3.2 eFuse的工作原理

eFuse的工作原理类似于保险丝:未编程时,熔丝保持完整,电阻约为150Ω;编程时,通过熔丝的电流产生热量,使熔丝熔断,电阻增大到3kΩ以上。通过检测电阻值的变化,即可读取存储的比特信息。

图5:eFuse编程前后电阻变化

3.3 eFuse在Memory Repair中的作用

在Memory Repair流程中,eFuse承担着“记忆”修复信息的重任:

Step 1:测试阶段— MBIST检测故障,BIRA生成修复方案

Step 2:编程阶段— 修复信息被压缩后写入eFuse

Step 3:上电阶段— eFuse中的修复信息自动加载到BISR寄存器

Step 4:运行阶段— 存储器根据修复配置正常工作

四、Memory Repair的工作流程

完整的Memory Repair流程可以分为以下几个阶段:

|

阶段 |

执行模块 |

主要任务 |

|

1. 测试 |

MBIST |

运行测试算法,检测故障单元 |

|

2. 分析 |

BIRA |

计算最优修复方案 |

|

3. 编程 |

BISR Controller |

将修复信息写入eFuse |

|

4. 加载 |

BISR Chain |

上电时自动加载修复配置 |

|

5. 验证 |

MBIST |

验证修复后的存储器 |

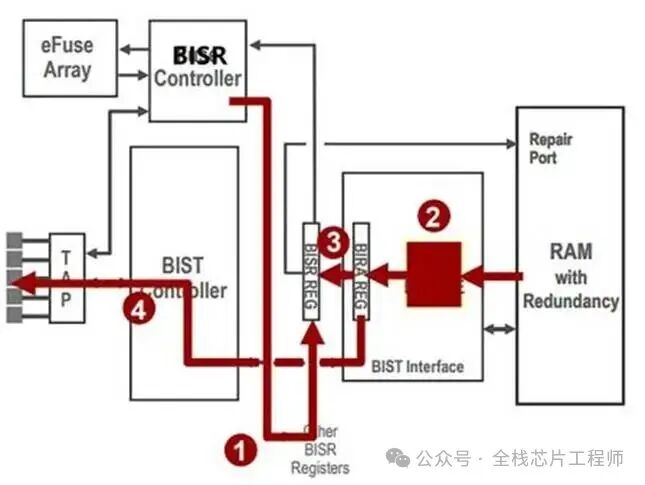

一套完整的 Memory Repair 体系,是 MBIST(内建自测试)、BIRA(内置冗余分析)、BISR(内建自修复)三大模块的协同工作,完整的修复流程可分为 5 个核心步骤,全程可实现自动化执行。

基于 Tessent 的 Memory Repair 标准架构图

步骤 1:上电初始化,修复链路就绪

芯片上电或复位后,BISR 控制器会先将 BISR 扫描链(修复寄存器)配置为初始状态,同时完成 MBIST 电路的初始化,为后续的测试与修复做好准备。

步骤 2:MBIST 测试,精准定位故障地址

MBIST 控制器启动测试流程,通过 March 算法、Checkerboard 算法等成熟的测试算法,向存储器写入测试向量,再读取回读数据与预期值对比,逐地址、逐单元检测故障,同时记录故障的地址、类型、数量等核心信息。

步骤 3:BIRA 分析,计算最优修复方案

BIRA(内置冗余分析)模块是整个修复流程的 “大脑”,它会接收 MBIST 输出的故障数据,结合预先设计的冗余资源配置,通过专用算法快速计算出最优的修复方案 —— 也就是用最少的冗余资源,覆盖最多的故障单元,同时判断该芯片是否具备可修复性(故障数量超过冗余资源上限则判定为废品)。

计算完成后,最终的修复签名会被存储到 BIRA 专用寄存器中。

步骤 4:修复信息传输与烧录

通过专用指令,BIRA 寄存器中的修复信息会被传输到 BISR 扫描链中。如果是 Hard Repair 模式,BISR 控制器会将修复信息进行压缩,然后通过 TAP 测试访问端口,将压缩后的修复数据烧录到 eFuse 阵列中,完成永久固化。

如果是 Soft Repair 模式,则直接将修复信息加载到修复寄存器中,无需烧录 eFuse。

步骤 5:修复生效与回测验证

芯片复位后,BISR 控制器会自动从 eFuse 或配置寄存器中读取修复信息,解压缩后加载到存储器的修复端口,完成故障地址到冗余单元的重映射,修复正式生效。

最后,会再次运行 MBIST 测试,对修复后的存储器进行全地址回测,验证所有故障单元都已被成功修复,确保存储器的功能、时序完全符合设计要求,只有通过验证的芯片才能进入后续的封装环节。

五、先进技术的应用与挑战

5.1 并发BISR(Concurrent BISR)

传统的BISR链是串行加载的,对于大型SoC,修复数据加载时间可能成为系统启动的瓶颈。并发BISR技术允许同时处理多条BISR链,显著缩短修复数据加载时间,特别适用于对启动时间敏感的应用场景。

5.2 硬增量修复(Hard Incremental Repair)

硬增量修复允许在不同测试阶段(如晶圆测试、封装测试、系统测试)分别进行修复分析,并将新的修复信息追加到已有的eFuse数据中。这种技术可以更充分地利用冗余资源,提高整体修复率。

5.3 3D存储器的全局BISR

随着3D堆叠存储器技术的发展,传统的局部BISR架构面临挑战。全局BISR(Global BISR)技术允许跨层共享冗余资源,并通过并行测试大幅缩短测试时间。研究表明,全局BISR相比传统方案可提升27%的修复率。

六、行业应用案例

6.1 车用电子芯片

车用电子芯片对可靠性要求极高,Memory Repair技术在此领域发挥着关键作用。除了传统的BISR,车用芯片还结合了以下技术:

▸POT(Power-On Test):上电即进行内存测试和修复

▸ECC(Error-Correcting Code):运行时纠正单比特错误

▸Error Injection:自我检测内存测试电路的正确性

6.2 HPC(高性能计算)芯片

HPC芯片包含大量存储器,功耗和测试时间是关键挑战。针对HPC的Memory Repair方案采用多链并行、功耗控制算法(PCA)和智能分群(MGD)等技术,在保证修复效果的同时优化功耗和性能。

总结与展望

DFT Memory Repair技术是现代芯片制造不可或缺的一环。通过MBIST、BIRA、BISR和eFuse的协同工作,它能够有效提升芯片良率,降低制造成本。随着工艺节点的不断演进和3D存储技术的发展,Memory Repair技术也在持续创新,向着更高效率、更低功耗、更强可靠性的方向迈进。

技术趋势展望

• AI辅助的冗余分析算法

• 更高效的eFuse压缩技术

• 支持Chiplets的分布式BISR

• 与DFT其他技术的深度融合

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)