sdc中set_multicycle_path的解释

目录

2.launch clk是快时钟,capture clk是慢时钟

3.launch clk是慢时钟,capture clk是快时钟

最近遇到了set_multicycle_path的问题,网上看到几篇文章有些有自相矛盾的地方。自己研究了半天先将自己的理解整理如下。理解错误之处欢迎指正。

该命令的格式如下:

set_multicycle_path path_multiplier [-setup|-hold] [-start|-end] \

-from <StartPoint> -through <ThroughPoint> -to <EndPoint>其中:

Default path_multiplier: Setup 1, Hold 0.

setup/hold :表明path_multiplier是针对setup(max delay)或者是hold(min delay)的操作。

start:表示要移动的clock为start clock也就是launch clock。hold默认移动该clk。

end:表示要移动的clock为end clock也就是capture clock。setup默认移动该clk。

当start clk和end clk为同频时,指定这两个选项是无意义的,因为此时两个clock频率一致。

关于这个问题分为3类

- 同频时钟。

- launch clk是快时钟,capture clk是慢时钟

- launch clk是慢时钟,capture clk是快时钟。

下面对于上述情况依次分析。

1.同频时钟,时钟上升沿对齐

如下图所示,为默认的STA检查情况。

这种情况对应的multicycle设置如下

set_multicycle_path 1 -setup -from CLK1 -to CLK2

set_multicycle_path 0 -hold -from CLK1 -to CLK2

可以看出默认情况下

setup 检查是从 launch clk的一个上升沿到下一个capture clk的上升沿。

hold检查是从 launch clk的一个上升沿到capture clk往前一个capture clk的边沿

当进行如下设置时

set_multicycle_path -setup 5 -from CLK1 -to CLK2

对应的时序检查关系如下

由于默认setup检查是从launch clk的0时刻开始对capture的3时刻,默认setup已经是1了。此时-setup设置为5就是从capture clk(默认setup就是对应的end clk也就是capture clck)的4时刻开始数5个clk,即-1时刻。

同时hold的检查是默认设置,即跟随capture移动X个capture clk到capture clk的0时刻。

此时的hold的检查过于严格,实际上应该检查launch clk的0时刻和capture clk的4时刻。

【怎么理解此时的hold检查过于严格?launch clk 0时刻和capture clk 0时刻的hold检查,就需要满组launch clk0时data变化,在capture clk0时 data还没变,这样就需要极长的path delay,而且此时留给setup的窗口也变短了,相当于setup 没有放松,用公式描述:

| 参数 | 计算公式 | 说明 |

| Setup Slack | T_capture(N) - T_launch - T_data - T_setup | 用N周期后的捕获沿 |

| Hold Slack | T_launch + T_data - T_capture(M) - T_hold | M=(N-1)或0 |

要满足hold时序则T_data > T_capture(M)+T_hold-T_launch,那么相对于setup检查来说时间窗口还是只有1T clk,就没有放松

】

set_multicycle_path -hold 4 -from CLK1 -to CLK2

hold检查应该向后移动4个capture clock。此时要注意hold的检查默认移动的是launch clk也就是CLK1向前移动了4个clk,检查的是clk1的4时刻和clk2的0时刻的hold也就相当于检查clk1的0时刻和clk2的4时刻的hold。

2.launch clk是快时钟,capture clk是慢时钟

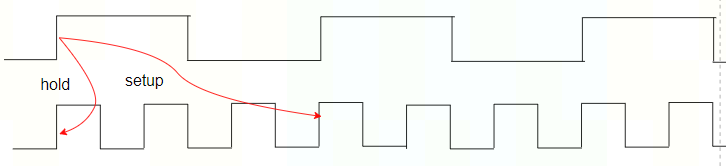

如下图所示,为默认的STA检查情况。

由于PT默认检查最悲观的情况所以,默认检查是这样的。这样setup和hold的检查最为悲观。默认的设置为

set_multicycle_path 1 -setup -end -from CLK1 -to CLK2

set_multicycle_path 0 -hold -start -from CLK1 -to CLK2

但在实际STA过程中,我们要放松一个setup检查,即

set_multicycle_path 2 -setup -start -from CLK1 -to CLK2

此时,对应的时序关系如下

由于launch clk和capture clk的频率并不相同所以要指定移动的clk这样PT才不会出错。

对于setup来说默认移动的是end clk也就是capture clk要想移动不同频率launch clk所以要指定

-start才行

同样的holdtime检查此时也会随之前移一个launch clk

如果不想让hold检查变化那么就要设置,其中start可以省略但是由于是频率不同的时钟为了易读性建议还是加上。

set_multicycle_path 1 -hold (-start) -from CLK1 -to CLK2

对应的时序关系为

3.launch clk是慢时钟,capture clk是快时钟

默认的检查如下

对应的设置如下

set_multicycle_path 1 -setup -end -from CLK1 -to CLK2

set_multicycle_path 0 -hold -start -from CLK1 -to CLK2

如果要放宽setup检查则应该设置

set_multicycle_path 2 -setup -end -from CLK1 -to CLK2

解释同前一小节

对应的时序检查如下。注意此时hold time检查也随之变化

如果想让holdtime检查在CLK的第二个上升沿应该进行如下设置

set_multicycle_path 1 -hold -start -from CLK1 -to CLK2

set_multicycle_path 2 -setup -end -from CLK1 -to CLK2

这里对于hold相当于launch clk后移了一个clk,同时由于setup的capture clk后移一个capture clk,hold的capture clk也自动跟着后移一个capture clk

时序检查如下。

注意这里和下面的约束不一样,相比于上图,下面的setup更松,上面的hold检查会更松。

set_multicycle_path 3 -setup -from CLK1 -to CLK2

set_multicycle_path 2 -hold -end -from CLK1 -to CLK2

总结

seup or hold和start or end时钟的对应关系如下

setup 默认是-end 向后移动capture clk,反过来加start就是前移launch clk

hold 默认是-start向后移动launch clk,反过来加-end就是前移capture clk

对于存在快慢时钟的MCP约束,-start和-end永远跟随工作在快时钟的寄存器。

如果launch clk是快时钟,就用setup + -start

set_multicycle_path N -setup -start -from CLK1 -to CLK2

set_multicycle_path N-1 -hold -from CLK1 -to CLK2如果capture clk是快时钟,就用hold + -end

set_multicycle_path N -setup -from CLK1 -to CLK2

set_multicycle_path N-1 -hold -end -from CLK1 -to CLK2而且两种情况下都是 setup的cycle为N,hold的cycle为N-1

————————————————

版权声明:本文为CSDN博主「进击的芯片」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/zyn1347806/article/details/97659093

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)