开源示波器项目SCOPEFUN学习日志-模拟前端设计(2)

本文为学习笔记,本项目为一个完整的双通道250MSps采样率示波器的开源项目 ,包含信号调理、采集、DAC输出、I/O控制,FPGA等多项内容,是硬件爱好者进阶学习的范例,项目地址为:https://www.scopefun.com/

第二部分(增益、偏置调节与触发)

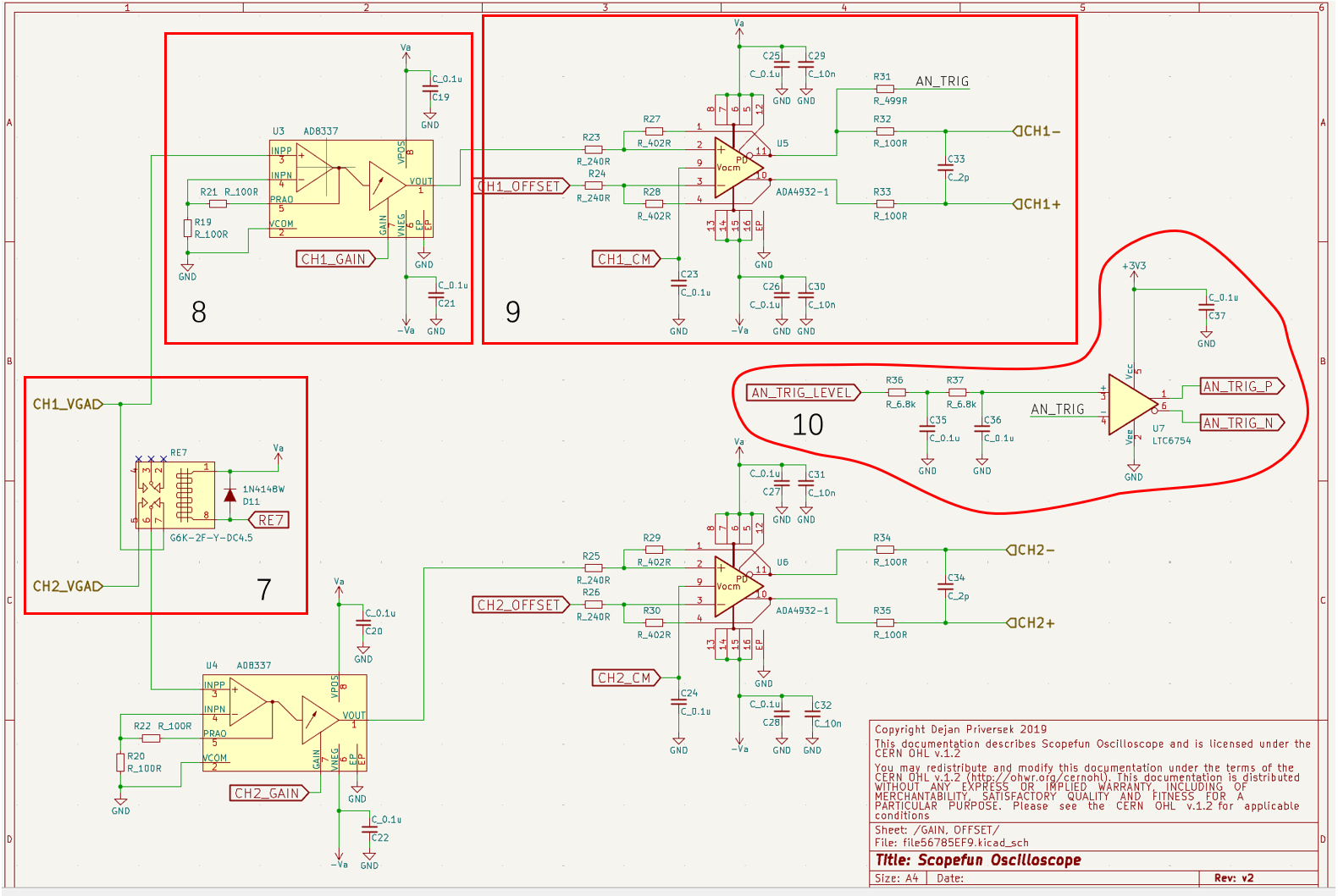

第二部分包含以上4各模块,本文将依次介绍这四个模块的功能的设计思想。

7.采样切换电路

这个继电器可以将第二路采样的输入也切换成CH1_VGA,通过ADC的时序控制,可以实现对CH1-VGA信号的双通道采样,从而将采样率提升到500Msps。

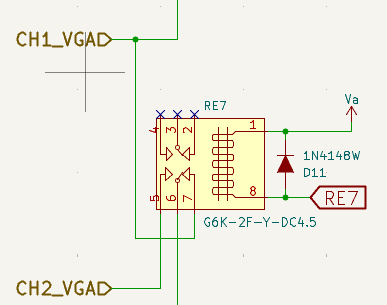

8.低噪声可调增益放大电路

这里使用了一个AD8337,这是一个低噪声VGA(Variable Gain Amplifier, 可变增益放大器),包含一个低噪声前置放大器以及一个VGA构成,从而具备低噪声特性。

我当时看的时候就有一个疑惑,既然是放大器,为什么不和第一部分的跟随器放在一起设计(把跟随器改成放大器)?这有以下两个方面的原因:

阻抗方面:第一部分的分压电路阻抗接近MΩ,是一个高阻电路,因此,要想基本无损的读取电压,必须需要一个极高输入阻抗的放大器。在阻抗上:MOSFET>JFET>>BJT,所以第一部分中的电压跟随器使用MOSFET放大器的原因。

噪声方面:MOSFET、BJT以及JFET三种晶体管具有不同的噪声特性,在电压噪声上:BJT<JFET<MOSFET,在电流噪声上:MOSFET≈JFET<BJT。对于高源阻抗电路,可有效降低由电流噪声带来的电压噪声(Vn=In*Rs)。而在电压跟随器完成阻抗变换后,AD8337前置了一个BJT的放大器,从而保证了整条链路的低噪声。

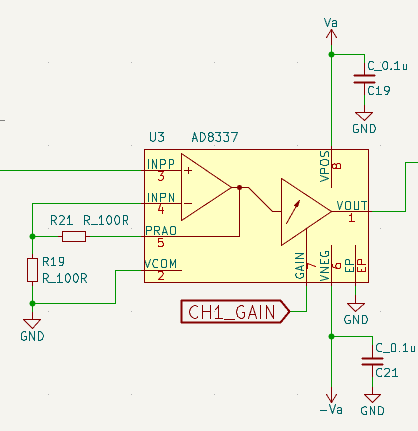

9.单端转差分/偏置注入/共模钳位

这个部分是信号进入ADC之前的最后环节,他完成了单端转差分/偏置注入以及共模钳位三个功能。

这部分使用了一个全差分放大器ADA4932-1。全差分放大器和一般放大器不同,他有两个输入,两个输出,以及一个Vocm端口。从而实现差分输入和差分输出。我们将OFFSET加在输入负极上,就可以将Vin-OFFSET进行放大,从而实现偏置调节。而Vocm则将差分输出的共模电压调成CH1_CM,这个是用于满足部分高速ADC对于直流偏置的需求,避免采样失真。

这个电路的输出接了两个100欧姆的电阻以及一个2pF的电容,这部分作用有两个作用:1.电荷缓冲 2.抗混叠滤波。

电荷缓冲是指:每次当ADC进行采样时,会有一个开关导通,使用一个极小的电容对外部电压进行采样,当两次采样的电压变化时,有极少电荷在极短时间流入ADC内部的电容当中,这个极短的电流脉冲会影响到前级差分放大器的工作(影响反馈从而影响电路输出稳定性),为了避免这个影响,我们加入一个电容,这个电容代替了放大器向ADC输出电荷,100欧姆的电阻也保证了通过放大器的电流的稳定,从而保证放大器稳定工作。

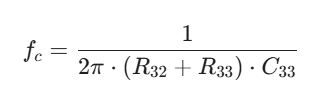

抗混叠滤波是指:这两个电阻和电容组成了一个一阶低通滤波器,他的截止频率为:

代入计算可知,截止频率为398MHz,从而滤除了398MHz以上的高频信号。我认为针对250MHz的ADC,我们应该将截止频率放在125MHz从而防止混叠,不知道这里为什么选了398MHz,可能是后续还有滤波。

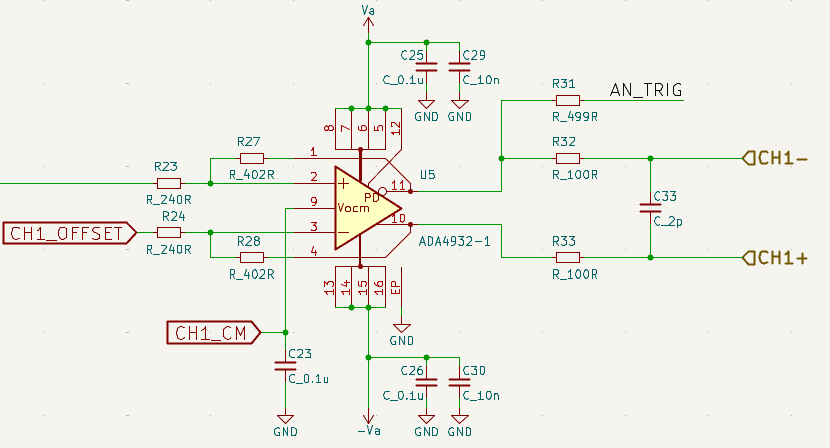

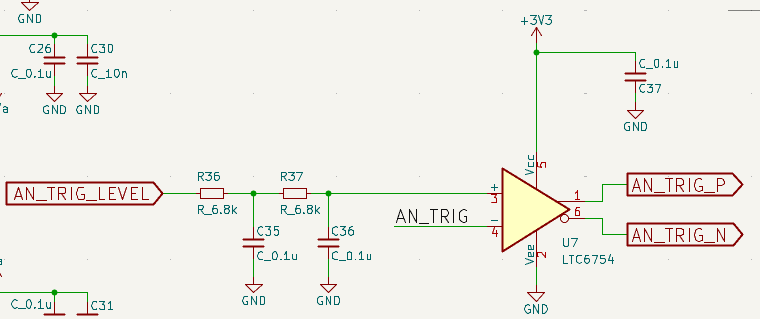

10.触发电路

这部分就是一个比较器,当AN_TRIG低于TRIG_LEVEL时,电路输出为高电平,否则为0,这个后续会接入到FPGA中进行TRIG控制。而AN_TRIG_LEVEL来自于一个DAC,可以实现灵活的电平触发控制。

至此,模拟前端的全部内容就已经完成了。模拟前端的第二部分主要实现了信号的低噪声放大(适应不同的量程档位,实现细调),偏置调节(让信号上下移动),差分转换以及模拟触发。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)