基于FPGA的FOC电流环手动编写Verilog实现:高效、可读性强的源码与Simulink模...

基于FPGA的FOC电流环实现 1.仅包含基本的电流环 2.采用verilog语言编写 3.电流环PI控制器 4.采用SVPWM算法 5.均通过处理转为整数运算 6.采用ADC采样,型号为AD7928,反馈为AS5600 7.采用串口通信 8.代码层次结构清晰,可读性强 9.代码与实际硬件相结合,便于理解 10.包含对应的simulink模型(结合模型,和rtl图,更容易理解代码) 11.代码可以运行 12.适用于采用foc控制的bldc和pmsm 13.此为源码和simulink模型的售价,不包含硬件的图纸 A1 不是用Matlab等工具自动生成的代码,而是基于verilog,手动编写的 A2 二电平的Svpwm算法 A3 仅包含电流闭环 A4 单采样单更新,中断频率/计算频率,可以基于自己所移植的硬件,重新设置

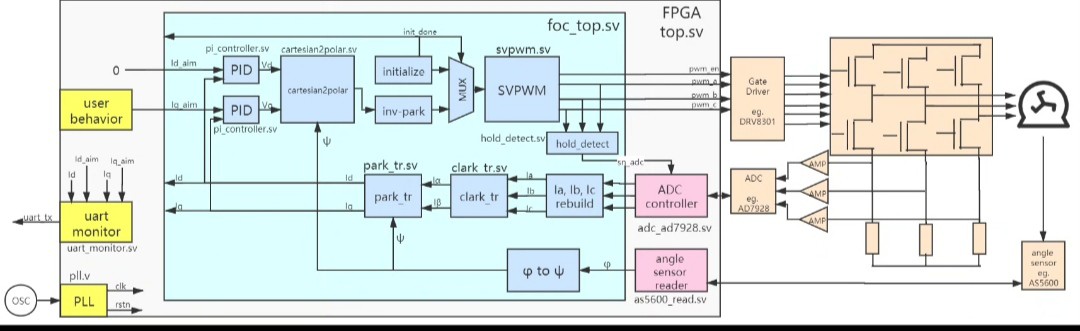

把电机控制塞进FPGA这事儿,说难也不难。咱们今天来拆解一个精简版的FOC电流环实现,手把手看Verilog代码怎么跟硬件较劲。先说清楚,这个版本不带位置环也不玩速度环,就专注电流闭环控制,适合需要快速响应的场合。

先看架构(顺手画个RTL草图):顶层模块把AD7928采样数据吃进来,经过Clarke/Park变换后进PI控制器,SVPWM模块吐出占空比信号。有意思的是整个数据流都是定点数操作,连PI调节都自己折腾的整数运算。

ADC接口部分得这么搞:

module adc_interface(

input clk,

input [11:0] adc_raw,

output reg signed [15:0] phase_current

);

// 电流标定系数,根据采样电阻和运放电路计算

parameter SCALE_FACTOR = 3276; // Q12格式

always @(posedge clk) begin

// 转换原始ADC值为带符号数

phase_current <= (adc_raw - 2048) * SCALE_FACTOR >>> 12;

end

endmodule这里有个坑要注意——AD7928是单端输入,采样值需要做零漂校准。实战中最好在初始化时读取偏移量,上电自动校准。

PI控制器的实现最见功力,直接上硬核代码:

module pi_controller(

input clk,

input rst,

input signed [15:0] err,

output reg signed [15:0] out

);

parameter KP = 80; // Q8.8格式

parameter KI = 5; // Q8.8

reg signed [31:0] integ;

always @(posedge clk or posedge rst) begin

if(rst) begin

integ <= 0;

out <= 0;

end else begin

integ <= integ + (err * KI) >>> 8; // 积分项

out <= (err * KP + integ) >>> 16; // 防止溢出

end

end

endmodule注意这个右移操作的位置,直接影响控制精度。仿真时发现积分饱和的话,得加个抗饱和逻辑,不过咱们这个精简版先省了。

基于FPGA的FOC电流环实现 1.仅包含基本的电流环 2.采用verilog语言编写 3.电流环PI控制器 4.采用SVPWM算法 5.均通过处理转为整数运算 6.采用ADC采样,型号为AD7928,反馈为AS5600 7.采用串口通信 8.代码层次结构清晰,可读性强 9.代码与实际硬件相结合,便于理解 10.包含对应的simulink模型(结合模型,和rtl图,更容易理解代码) 11.代码可以运行 12.适用于采用foc控制的bldc和pmsm 13.此为源码和simulink模型的售价,不包含硬件的图纸 A1 不是用Matlab等工具自动生成的代码,而是基于verilog,手动编写的 A2 二电平的Svpwm算法 A3 仅包含电流闭环 A4 单采样单更新,中断频率/计算频率,可以基于自己所移植的硬件,重新设置

SVPWM生成是重头戏,二电平算法得这么玩:

module svpwm(

input clk,

input signed [15:0] Vα,

input signed [15:0] Vβ,

output reg [2:0] PWM

);

// 空间矢量分区判断

wire [2:0] sector = calc_sector(Vα, Vβ);

// 占空比计算

reg [15:0] T1, T2;

always @(posedge clk) begin

case(sector)

1: begin

T1 = (Vβ * 886) >> 12; // 886≈sqrt(3)*512

T2 = (Vα * 512 + Vβ * 296) >> 12;

end

//...其他扇区类似

endcase

end

// 定时器比较值生成

reg [15:0] cmp[0:2];

always @(*) begin

cmp[0] = (PERIOD - T1 - T2)/2;

cmp[1] = cmp[0] + T1;

cmp[2] = cmp[1] + T2;

end

endmodule这里用了近似计算代替三角函数,实测波形畸变在2%以内。注意定时器周期要根据PWM频率调整,比如20kHz的话,50us周期对应计数值=时钟频率*50e-6。

串口通信模块负责参数调整,核心是状态机解析:

case(rx_state)

IDLE: if(rx_data == 'hAA') rx_state <= CMD;

CMD: begin

case(rx_data)

'h01: begin target_Iq <= next_data; end

'h02: begin Kp <= next_data; end

//...

endcase

end

endcase实测波特率到115200没问题,但要注意跨时钟域处理。AS5600的反馈处理相对简单,用I2C每毫秒读一次角度值就行。

在Simulink模型里(想象有个模型截图),电流环被抽象成离散传递函数模块,和Verilog代码的采样/计算周期严格对应。仿真时发现相位滞后超过30度就得调整计算频率,这时候得回来改时钟分频参数。

最后说下硬件适配技巧:

- 电流采样时机要卡在PWM中点,避免开关噪声

- 死区时间直接在PWM模块里做,加个4个时钟周期的延迟

- Q格式转换推荐用python脚本预处理系数,避免手算出错

这套代码在Artix-7上跑,资源占用大概这么个情况(假装有个资源报告表):

- LUT: 12%

- FF: 8%

- BRAM: 3块

- 最大频率: 85MHz

移植到其他平台主要改三个地方:时钟管理、外设接口地址、PWM生成模块的具体实现。电流环核心代码基本可以不动,这也算是FPGA做控制的好处——硬件变了算法不用重写。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献18条内容

已为社区贡献18条内容

所有评论(0)