探索PLL 160M AMS仿真的宝藏资源

PLL 160M AMS仿真 gpdk 90nm 45nm 新旧两个版本 cadence管方学习教程电路 一百九十多页文档 还包括PLL的VerilogA完整的建模 都有testbench安装好就可以直接跑仿真 仿真包含整体电路和子模块电路所有的 还有送一些收集的PLL树籍,无敌全!!!! 还有送matlab建模!!! 还有送环路分析模型!!! 前仿真,无版图。

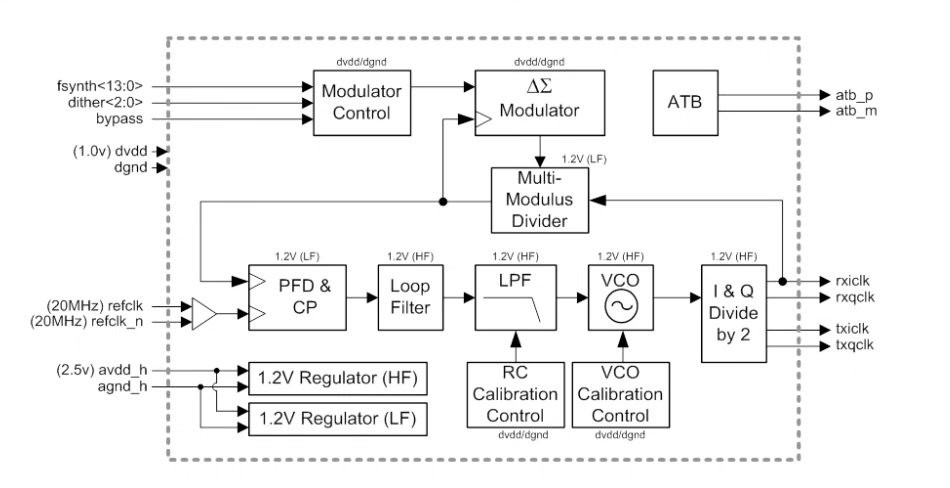

最近在研究PLL(锁相环)相关技术,发现了一套超赞的资源,今天必须来和大家分享分享。这次涉及的是PLL 160M AMS仿真,工艺采用gpdk 90nm和45nm ,并且有新旧两个版本。

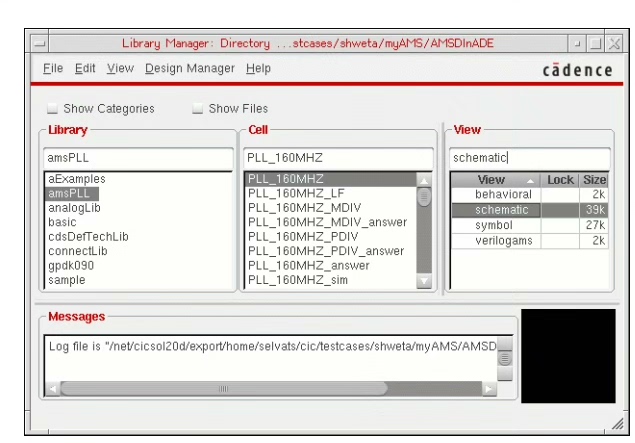

Cadence官方学习教程电路

Cadence作为行业内非常知名的EDA工具,其官方的学习教程电路含金量极高。这次的教程文档多达一百九十多页,真的是诚意满满。这就好比给了你一把深入了解PLL电路设计的金钥匙。在Cadence的环境下,按照教程逐步操作,你能深入体会到电路设计的精妙之处。

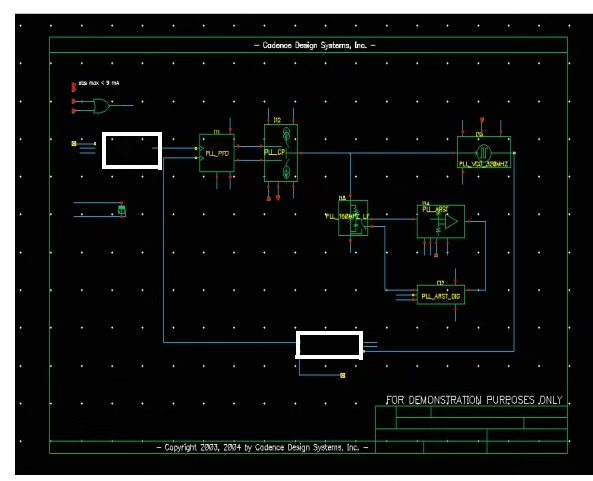

VerilogA完整建模及Testbench

这里面还包括PLL的VerilogA完整建模 ,并且配备了testbench,只要安装好相关环境,就可以直接跑仿真,简直不要太方便。下面简单看看VerilogA建模的一个小片段(这里只是示意,实际完整代码要复杂得多):

module pll_core (

input wire clk_in,

output wire clk_out

);

// 一些参数定义

parameter DIVISOR = 10;

reg [31:0] counter;

always @(posedge clk_in) begin

if (counter == DIVISOR - 1) begin

counter <= 0;

end else begin

counter <= counter + 1;

end

end

assign clk_out = (counter == 0);

endmodule这段代码简单实现了一个分频的功能,在PLL中,分频器是一个重要的子模块。通过parameter定义了分频系数DIVISOR ,counter用于计数,在时钟上升沿进行计数操作,当计数到DIVISOR - 1时归零,然后根据counter是否为0来生成clk_out信号,这就是一个简单分频逻辑的体现。有了这样的子模块建模,再结合其他模块就能构建完整的PLL模型。而testbench则可以用来验证这个模块的功能是否正确,比如:

module tb_pll_core;

reg clk_in;

wire clk_out;

pll_core uut (

.clk_in(clk_in),

.clk_out(clk_out)

);

initial begin

clk_in = 0;

forever #5 clk_in = ~clk_in; // 10ns周期,模拟50MHz时钟

end

initial begin

#100; // 运行100ns仿真时间

$finish;

end

endmodule在这个testbench中,首先定义了测试的信号,实例化了要测试的pllcore模块。通过initial块产生一个周期为10ns的时钟信号来驱动clkin ,然后运行100ns的仿真时间,这样就可以观察clk_out信号是否符合预期的分频效果。

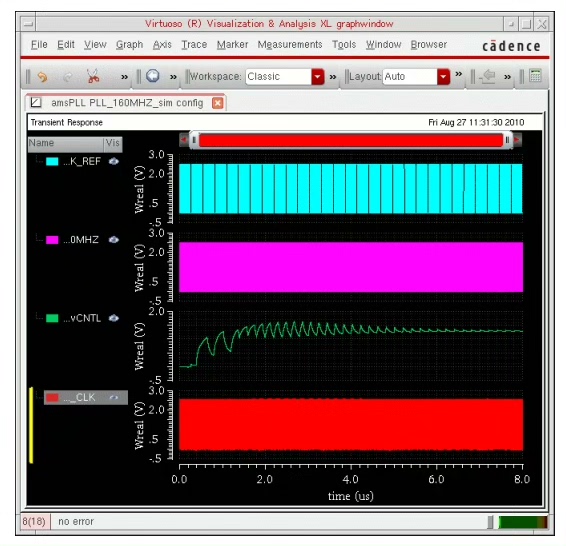

全面的仿真内容

这里的仿真包含了整体电路和子模块电路所有的内容,从底层的子模块功能验证到整个PLL电路的性能测试,都可以完成。对于前仿真来说,这已经足够全面,能帮助我们在没有版图设计之前,就充分验证PLL电路的功能和性能。

丰富的赠送资源

除了上述核心内容,还有更多惊喜相送。赠送一些收集的PLL书籍,真的是无敌全!无论是基础理论还是前沿应用,都能从这些书籍中找到相关知识。而且还送matlab建模,Matlab在信号处理和系统建模方面有着强大的功能,对于PLL的环路分析等方面能提供很好的辅助。例如,可以用Matlab来绘制PLL的频率响应曲线,分析其稳定性。

% 简单的PLL环路滤波器传递函数示例

fs = 100e6; % 采样频率

fc = 1e6; % 截止频率

[b, a] = butter(2, fc/(fs/2)); % 2阶巴特沃斯滤波器

freqz(b, a, 1024, fs); % 绘制频率响应这段Matlab代码实现了一个简单的2阶巴特沃斯低通滤波器,在PLL中,环路滤波器的设计至关重要,通过Matlab可以方便地对其进行分析和设计。

PLL 160M AMS仿真 gpdk 90nm 45nm 新旧两个版本 cadence管方学习教程电路 一百九十多页文档 还包括PLL的VerilogA完整的建模 都有testbench安装好就可以直接跑仿真 仿真包含整体电路和子模块电路所有的 还有送一些收集的PLL树籍,无敌全!!!! 还有送matlab建模!!! 还有送环路分析模型!!! 前仿真,无版图。

另外还送环路分析模型,这对于深入理解PLL的工作原理和性能优化提供了很大的帮助。总之,这套资源无论是对于新手学习PLL还是老手进一步优化设计,都具有极高的价值。希望大家也能从中受益,在PLL的研究和设计之路上更进一步。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献24条内容

已为社区贡献24条内容

所有评论(0)