SAR ADC逐次逼近型ADC全流程设计探秘

SAR ADC逐次逼近型ADC全流程设计 包括SAR ADC的理论分析,从基本的ADC结构到电路原理。 包括SAR ADC的Matlab建模,从基础的Matlab代码讲解到各种非理想因素的模型分析。 包括SAR ADC的电路设计,从各个子模块的电路设计到完整的ADC设计和性能仿真测试。

一、SAR ADC理论分析

1.1 基本ADC结构

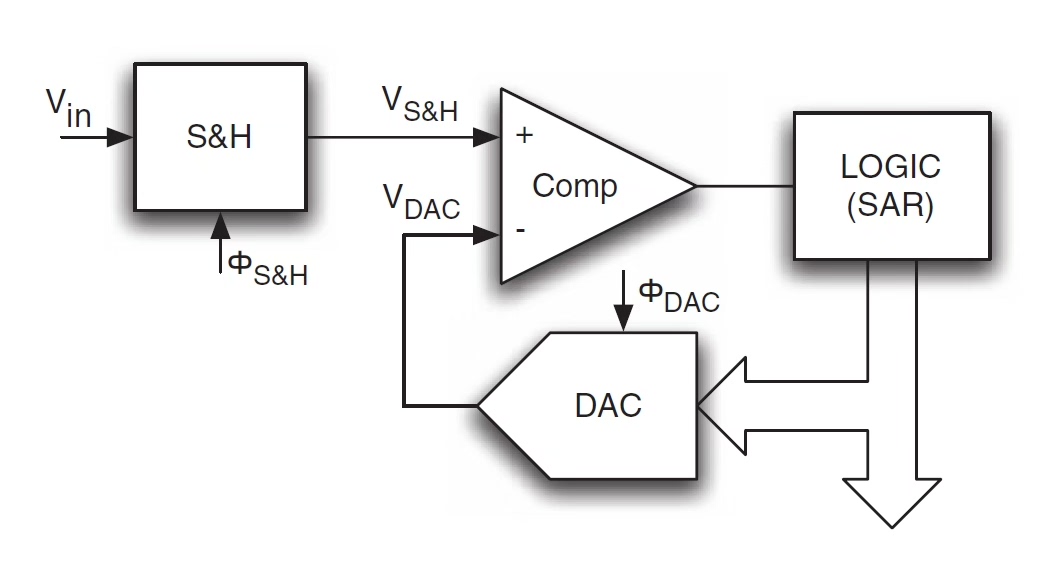

ADC,即模拟数字转换器,其核心功能是将连续的模拟信号转换为离散的数字信号。SAR ADC(逐次逼近型ADC)是众多ADC结构中较为经典的一种。

想象一下,我们有一个天平,一边放着未知重量的物体(模拟信号),另一边放着已知重量的砝码(数字信号对应的量化值)。SAR ADC就像是通过不断尝试不同砝码组合,来精准衡量物体重量。

它主要由比较器、SAR 逻辑电路、DAC(数模转换器)以及寄存器组成。模拟输入信号首先进入比较器,与DAC输出的参考电压进行比较。SAR逻辑电路会根据比较结果调整DAC输出,逐步逼近模拟输入信号的值,最终确定数字输出。

1.2 电路原理

从电路原理角度看,SAR ADC工作在一个逐次逼近的过程。比如8位的SAR ADC,它会从最高位(MSB)开始,依次确定每一位的数值。

SAR ADC逐次逼近型ADC全流程设计 包括SAR ADC的理论分析,从基本的ADC结构到电路原理。 包括SAR ADC的Matlab建模,从基础的Matlab代码讲解到各种非理想因素的模型分析。 包括SAR ADC的电路设计,从各个子模块的电路设计到完整的ADC设计和性能仿真测试。

假设参考电压 \(V{ref}\) 为 \(5V\),模拟输入信号 \(V{in}\) 为 \(3V\)。首先,SAR逻辑电路会设置DAC输出为 \(V{ref}/2 = 2.5V\),比较器比较 \(V{in}\) 和 \(2.5V\),因为 \(3V > 2.5V\),所以最高位(MSB)被置为1。

接着,SAR逻辑电路调整DAC输出为 \(2.5V + 2.5V/2 = 3.75V\),再次比较 \(V_{in}\) 和 \(3.75V\),由于 \(3V < 3.75V\),次高位被置为0。依此类推,直到确定所有8位的值。

二、SAR ADC的Matlab建模

2.1 基础Matlab代码讲解

我们可以通过Matlab代码来初步构建一个简单的SAR ADC模型。以下是一个基础示例:

% 定义参数

n = 8; % 分辨率为8位

Vref = 5; % 参考电压5V

Vin = 3; % 模拟输入电压3V

% 初始化数字输出

digital_output = zeros(1,n);

for i = n:-1:1

dac_output = Vref * sum(digital_output.* 2.^((n - 1):-1:0)) / (2^n - 1);

test_value = dac_output + Vref / 2^(i);

if Vin >= test_value

digital_output(i) = 1;

end

end

fprintf('数字输出为: %s\n', dec2bin(bin2dec(num2str(digital_output)),n));这段代码中,首先定义了分辨率 n、参考电压 Vref 和模拟输入电压 Vin。然后通过循环,从最高位开始,根据每次DAC输出与模拟输入的比较结果,确定数字输出的每一位。

2.2 非理想因素的模型分析

实际的SAR ADC存在许多非理想因素,比如比较器失调、DAC误差等。以比较器失调为例,我们可以在代码中加入失调电压的影响。

% 定义参数

n = 8; % 分辨率为8位

Vref = 5; % 参考电压5V

Vin = 3; % 模拟输入电压3V

offset = 0.1; % 比较器失调电压0.1V

% 初始化数字输出

digital_output = zeros(1,n);

for i = n:-1:1

dac_output = Vref * sum(digital_output.* 2.^((n - 1):-1:0)) / (2^n - 1);

test_value = dac_output + Vref / 2^(i);

if Vin + offset >= test_value

digital_output(i) = 1;

end

end

fprintf('考虑失调后的数字输出为: %s\n', dec2bin(bin2dec(num2str(digital_output)),n));在这个代码片段中,我们增加了一个 offset 变量来模拟比较器失调电压。可以看到,失调电压的存在会使比较结果发生变化,进而影响最终的数字输出。

三、SAR ADC的电路设计

3.1 各个子模块的电路设计

- 比较器:比较器是SAR ADC的关键模块之一。常见的比较器电路可以采用简单的运算放大器结构,将模拟输入信号和DAC输出信号作为运算放大器的两个输入,输出高低电平来表示比较结果。

module comparator (

input wire inp1,

input wire inp2,

output reg out

);

always @(*) begin

if (inp1 > inp2)

out = 1;

else

out = 0;

end

endmodule上述Verilog代码实现了一个简单的比较器,通过比较两个输入信号 inp1 和 inp2,输出比较结果 out。

- SAR逻辑电路:它负责控制DAC的输出以及根据比较器结果更新数字输出。可以用状态机来实现其逻辑。

module sar_logic (

input wire clk,

input wire rst,

input wire compare_out,

output reg [7:0] digital_out,

output reg [7:0] dac_control

);

reg [2:0] state;

parameter [2:0]

START = 3'b000,

COMPARE = 3'b001,

UPDATE = 3'b010;

always @(posedge clk or posedge rst) begin

if (rst) begin

state <= START;

digital_out <= 8'b00000000;

dac_control <= 8'b10000000;

end else begin

case (state)

START: begin

state <= COMPARE;

end

COMPARE: begin

if (compare_out)

digital_out <= digital_out | dac_control;

dac_control <= dac_control >> 1;

if (dac_control == 8'b00000001)

state <= UPDATE;

else

state <= COMPARE;

end

UPDATE: begin

state <= START;

end

endcase

end

end

endmodule这段代码实现了一个8位SAR逻辑电路的状态机。通过时钟信号 clk 和复位信号 rst 控制,根据比较器输出 compareout 更新数字输出 digitalout 和DAC控制信号 dac_control。

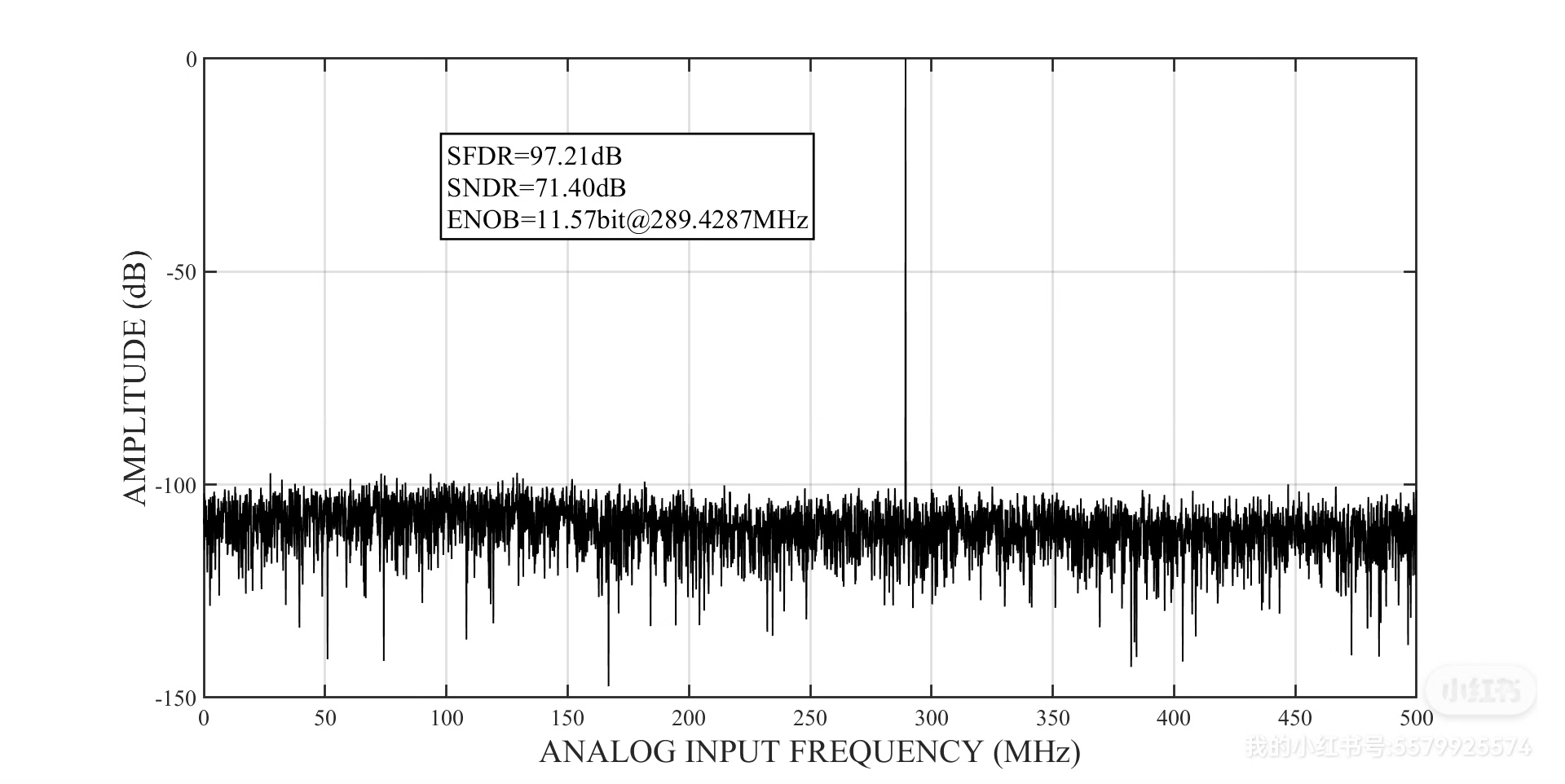

3.2 完整的ADC设计和性能仿真测试

将各个子模块组合起来,就构成了完整的SAR ADC电路。然后我们可以使用仿真工具,如Cadence的Spectre或者ModelSim,对其性能进行测试。

例如在ModelSim中,可以编写测试平台来验证SAR ADC的功能。

module tb_sar_adc;

reg clk;

reg rst;

reg [7:0] analog_in;

wire [7:0] digital_out;

sar_adc uut (

.clk(clk),

.rst(rst),

.analog_in(analog_in),

.digital_out(digital_out)

);

initial begin

clk = 0;

forever #5 clk = ~clk; // 10ns周期的时钟

end

initial begin

rst = 1;

analog_in = 8'd100;

#10;

rst = 0;

#100;

$stop;

end

endmodule在这个测试平台中,我们为SAR ADC提供时钟信号 clk、复位信号 rst 和模拟输入信号 analogin,观察数字输出 digitalout,以此来验证设计的正确性。通过这样一步步的设计、建模和仿真,我们就能完成SAR ADC的全流程设计,深入了解这种经典ADC结构的魅力与应用。

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献13条内容

已为社区贡献13条内容

所有评论(0)