基于微程序控制器的8位模型计算机设计

计算机组成原理课程设计——基于微程序控制器的 8 位模型计算机设计

一、选题背景

基于微程序控制器进行 8 位模型计算机的设计,主要有以下四个方面的任务:

1、根据所给出指令系统的要求对模板电路做进一步增删以形成最终的仿真电路;

2、在已给出的指令系统的基础上,可以根据需求对指令系统加以扩展,但指令系统的指令条数不小于等于 16 条;

3、设计微指令系统;

4、基于模型机指令系统的用户程序设计。

二、方案论证

2.1 CPU 机器指令设计

如下表 2.1-1 所示,指令格式定义如下:指令捏 OP 码为指令第一字节的高四位,即指令寄存器 IR 的 I7I6I5I4 位。而 RA 和 RB 是指由 I3I2 和 I1I0 定义的逻辑寄存器,RA 或 RB 都可以选择四个物理寄存器(R0~R3)中的任何一个。

表 2.1-1 微程序版 CPU 指令集(OP 码表)(已完善后的版本)

|

OP 码(I7I6I5I4) |

指令助记符 |

OP 码(I7I6I5I4) |

指令助记符 |

|

0000 |

NOP/HLT |

1000 |

LAD/POP |

|

0001 |

JMP/JMPR/Jx/JxR |

1001 |

STO/PUSH |

|

0010 |

SOP (INC/DEC/NOT/THR) |

1010 |

LYS |

|

0011 |

SET |

1011 |

XOR/XORI |

|

0100 |

IN |

1100 |

SUB/SUBI |

|

0101 |

OUT/OUTA |

1101 |

ADD/ADDI |

|

0110 |

LOOP(LPSTA/LPINC) |

1110 |

XX |

|

0111 |

EXCESS(%3) |

1111 |

OR/ORI |

上述指令的设计从任务出发完善,展开后包含 29 条机器指令,其中 OP 码为 1110 的指令多余,里不加定义,其他按功能分成如下 6 大类:

(部分缺失内容,待完善)

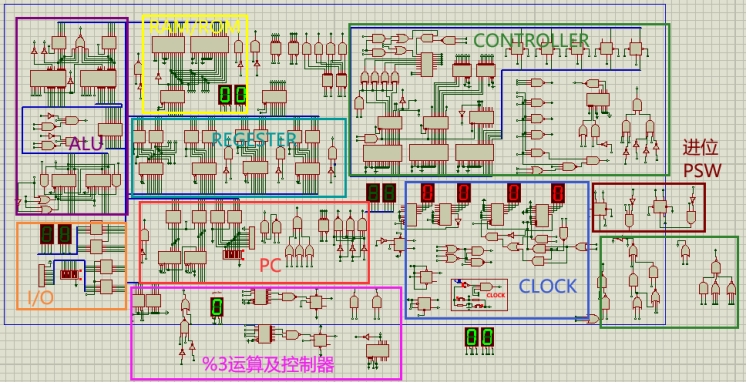

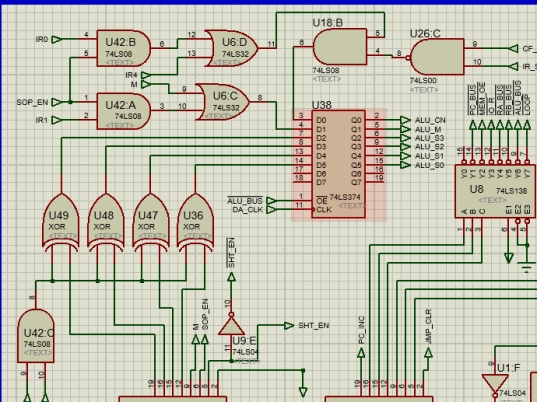

2.2 微程序版 CPU 架构

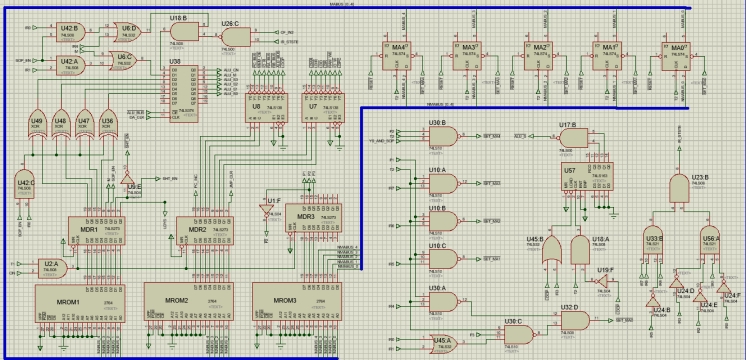

如下图 2.2-1 所示,本实验的微程序版 CPU 由微程序控制器通路(CONTROLLER)、时序电路(CLOCK)及数据通路组成。数据通路包括:程序存储器 ROM、数据存储器 RAM 及通用寄存器 R0~R3;IO 接口;算术逻辑运算器(74LS181)及附带的移位寄存器(74LS194);程序计数器(PC)、ALU 运算结果进位标志位寄存器(PSW)以及对 3 取余操作的运算和控制的逻辑组合电路。数据通路的所有部件都共同挂在一条 8 位系统总线 BUS 上。

图 2.2-1 微程序版 CPU 电路图

上图 2.2-1 中的微程序版 CPU 架构如下图 3-2 所示

图 2.2-2 微程序版 CPU 架构示意图

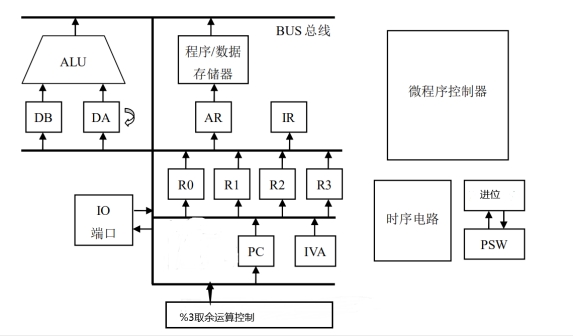

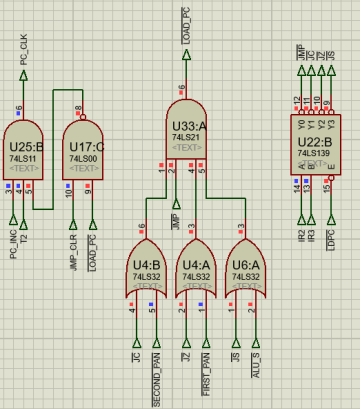

2.3 时序电路

图 2.3-1 时序电路图

微程序版 CPU 的时序电路如上图 3-3 所示:用红色边框围起来的 CLOCK 电路是 CPU 的基准时钟电路,系统时钟 CLK 可以由方波信号源 AUTO-CLK 提供(双击信号源可以自行选择方波信号频率)或者通过开关 MANUA 手动步进。当初始化信号 ON=0 或停机指令信号-HLT =0,时钟 CLK 阻塞(强制 CLK=0),CPU 停机。

CLOCK 电路右侧是一个 JK 触发器 74LS73 实现的微指令状态机。由于微程序控制器和数据通路相互独立,两者操作可以并行执行,如下表所示。所以,微程序版 CPU 的微指令周期只需要 T1 和 T2 两个状态,时钟信号 CLK 驱动微指令状态机循环输出节拍序列{T1,T2},使状态顺序转移:T1,T2,T1……

表 2.3-1 微程序版 CPU 的微指令状态机

|

状态 |

微程序控制器通路 |

数据通路 |

|

T1 |

使能当前微指令的微操作信号有效 |

信息从源部件输出到总线 BUS |

|

T2 |

微指令下址取址根据 OP 码决定微指令下址[0I7I6I5I4](取指微指令) |

信息从总线 BUS 打入目的部件;程序计数器 PC+1(取指微指令) |

CLOCK 电路左侧是初始化电路,手动按钮令复位信号-RESET 上升沿跳变,可以使信号 ON=1。CPU 启动仿真后,初始化过程十分简单,如下所述:

1) 启动仿真后,时钟 CLK 选择从手动按钮 MANUA 输入信号;

2) 手动按钮使信号-RESET 跳变“1,0,1”,令信号 ON=1,CLK 允许输出,过程结束。

CLOCK 电路上方是 NOP/HLT 指令电路:当指令寄存器 IR 的 OP 码 I7I6I5I4=0000 的时候,空指令信号 NOP=1,送往微指令计数器 OP 码 I7I6I5I4=0000 且 I0=1 的时候,指令信号 HLT=1,时钟 CLK 阻塞,CPU 停机(陷入“断点”)。跳出 HLT 指令“断点”的复位过程与上述初始化过程完全相同,区别在于初始化过程结束后,CPU 进入第一条指令的取指周期 T1 节拍;而复位过程结束后,CPU 进入 HLT 指令后续下一条指令的取指周期 T1 节拍。

为了便于观测程序和微程序的运行,时序电路提供了双位的指令计 数器 I 显示当前运行第几条机器指令,以及单位的微指令计数器 MICRO 显示当前运行指令计数器 I 所示指令中的第几条微指令。微指令计数器 MICRO 由十进制计数器 74LS160 构成,基于信号 ON(初始化过程)或 T1 节拍上升沿驱动递增,在指令周期末尾使能加载信号 ML=1,在下一个指令周期开始时刻,重置 MICRO 的计数值为“1”,重新计数。当以下条件之一成立时,表示当前微指令是指令周期最后一条微指令,令 M=1。

1)当前执行微指令中的判断位 P2=1;

2)空指令信号 NOP=1 且判断位 P1=1(特殊情况:NOP 指令末尾)

3)停机信号 HLT =1;( 特殊情况:HLT 指令末尾)

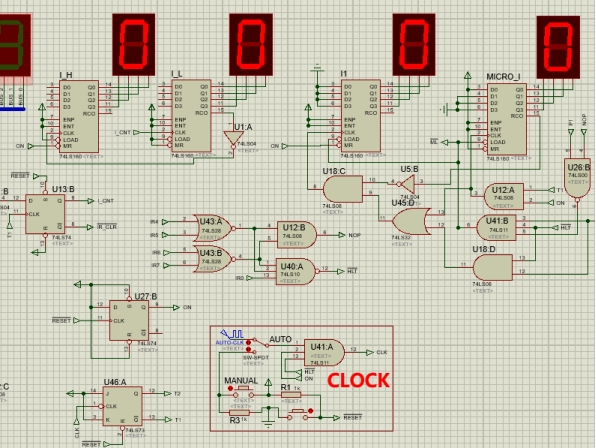

2.4 微程序控制器

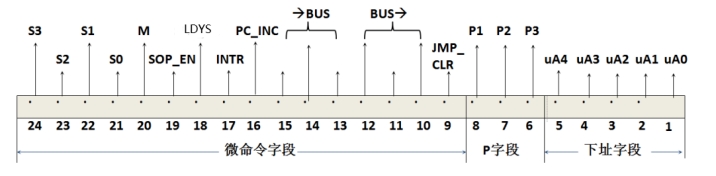

微程序版 CPU 的微指令结构图如下图所示,微指令字长 24 位,其中微指令的 1-5 位是下一条微指令地址,即下址字段[uA4, uA0];微指令的 6-8 位是判断字段 P1~P3;微指令的 9-24 位则是微命令字段,对应数据通路的所有微操作信号:其中置“1”的位表示执行相应的微操作;反之,置“0”的位则是不执行相应的微操作。

图 2.4-1 微程序版 CPU 的微指令结构图

此外,微指令的 15-13 位和 12-10 位采用字段编译法(3-8 译码),分别对应源部件输出到总线 BUS 和总线 BUS 打入目标部件的微操作信号,如下表所示:

表 2.4-1 微指令字段编译列表

|

“->BUS”字段 |

“BUS->”字段 |

||||||

|

15 |

14 |

13 |

微命令 |

12 |

11 |

10 |

微命令 |

|

0 |

0 |

0 |

\ |

0 |

0 |

0 |

\ |

|

1 |

0 |

0 |

PC_BUS |

1 |

0 |

0 |

LDAR |

|

0 |

1 |

0 |

MEM_OE |

0 |

1 |

0 |

LDIR |

|

1 |

1 |

0 |

IO_R |

1 |

1 |

0 |

LDD |

|

0 |

0 |

1 |

RA_BUS |

0 |

0 |

1 |

LDR |

|

1 |

0 |

1 |

RB_BUS |

1 |

0 |

1 |

RAM_WE |

|

0 |

1 |

1 |

ALU_BUS |

0 |

1 |

1 |

IO_W |

|

1 |

1 |

1 |

LOOP |

1 |

1 |

1 |

LDPC |

基于上述微指令结构,本实验设计了如下图所示的微程序控制器通路,包括三个 8 位 ROM 存储器 2764 组成的微指令存储器 MROM1~3,三个寄存器 74LS273 组成的微指令寄存器 MDR1~3,微指令译码电路,五位微地址寄存器 MA0~MA4 及微地址转移电路。

24 位微指令存储器 MROM1~3 共存放了 32 条微指令,所以微地址是 MABUS_4~0。当信号 ON 或 T1 节拍上升沿,微地址下址指定的微指令的微命令字段和 P 字段锁存到微指令寄存器 MDR1~3,输出微操作信号;而下址字段则送往微地址寄存器。

图 2.4-2 微程序控制器通路

本实验的微地址转移电路如上图所示,微地址寄存器五位(MA4-MA0),由触发器 74LS74 组成。T2 时刻,当前微指令 1-5 位的下一条微指令地址[uA4, uA0]打入微地址寄存器;此刻,若当前执行的微指令中的判断位 P1~P3 置位,则地址转移逻辑电路将根据判断位 P1~P3 置位微地址寄存器 MA4-MA0:P2 位生成信号

![]()

,P1 生成信号

![]()

,P1 和 P3 位共同生成信号

![]()

。判断位 P1~P3 的地址跳转。逻辑如下所示(可以对照后面具体指令流程图中“菱形框”的条件判断分支过程):

P1 逻辑:若当前微指令是机器指令取指周期的最后一条微指令,则判断位 P1=1,从而根据指令寄存器 IR 的 I7I6I5I4 位强制置位微地址寄存器的 MA3-MA0,修改微地址[uA3, uA0]位,转向该机器指令的执行周期序列的第一条微指令地址[0I7I6I5 I4]。

P2 逻辑:若当前微指令是机器指令执行周期的最后一条微指令,则判断位 P2=1,若此时为对 3 取余阶段且没有结束, 则强制置位微地址寄存器的 MA4,转向微指令地址[10000]继续;否则返回取指周期第一条微指令地址[00000];

P3 逻辑:在 CPU 指令集中部分单字节指令和双字节指令(LAD/POP、STO/PUSH、ALU 系列和 JMP 系列指令)共用 OP 码,其执行周期的微指令序列共用第一条微指令(判断位 P3=1),从第二条微指令开始分支,根据指令寄存器 IR 的 I1I0 位来决定不同微指令的分支走向:若 I1I0=00,微指令下址的 MA0=0,操作数分别来自寄存器和存储器(双字节指令);若 I1I0≠00,则微指令下址的 MA0=1,操作数全部来自寄存器(单字节指令)。

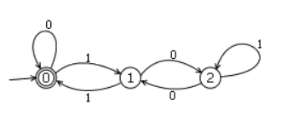

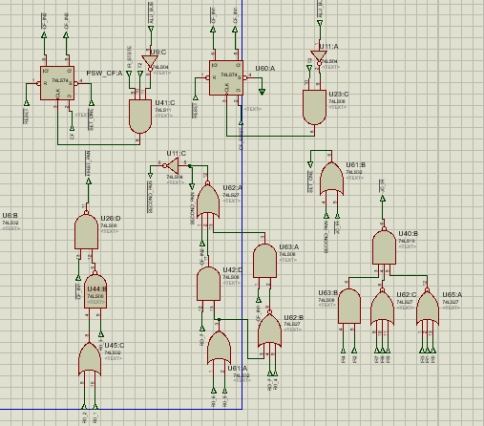

2.5 对 3 取余实现硬件电路

如下为对 3 取余的逻辑原理图,这个正则表达式的求法可以说是相当暴力的,但用于这次实验中却可以实现高效操作。注意到,一个二进制数后面加一个“0”相当于该数乘以 2,一个二进制数后面加一个“1”相当于该数乘 2 加 1。设定三个状态,分别叫做 0、1 和 2,它们表示当前的数除以 3 所得的余数。如果对于某个 i 和 j,有 i2≡j (mod 3),就加一条路径 i→j,路径上标一个字符“0”;如果 i2+1≡j (mod 3),则在路径 i→j 上标记“1”。状态 0 既是我们的初始状态,也是我们的最终状态。我们的自动机就做好了。现在,假如二进制数 10010 走进来了。从状态 0 出发,机器首先读到一个“1”,于是当前位置挪到状态 1,表明目前该数模 3 余 1;然后,系统读了一个“0”,我们紧跟着走到状态 2,表明二进制数“10”被 3 除余 2;下一步,我们回到状态 1,表明“100”除以 3 余 1;再往后,我们得知“1001”能被 3 整除。最后呢,我们读到一个 0,“1001”的两倍当然还是能被 3 整除,我们依旧停留在原位。我们得到结论:二进制数 10010 能被 3 整除。

图 2.5-1 对 3 取余的逻辑原理图

为了实现高效率取余操作,这里利用一个微控制信号 LDYS 启动取余,然后根据上述原理配合如下硬件逻辑电路实现取余,如下图,中间两个 74LS138 根据逻辑功能实现从一个状态到另一个状态的转换,结果保留与触发器中,因为实验要求为对输入值取余,只有 8 位,通过移位分别去取出这 8 个数值并同时改变当前余数状态,循环 8 次;由如下右边电路实现计数和判断退出操作,左边电路实现将取余结果 YS 传递到数据总线中。

图 2.5-2 对 3 取余的逻辑电路图

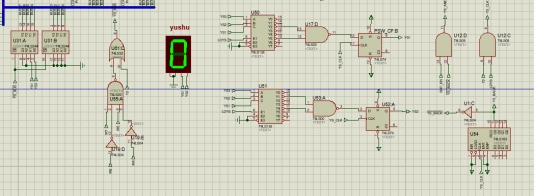

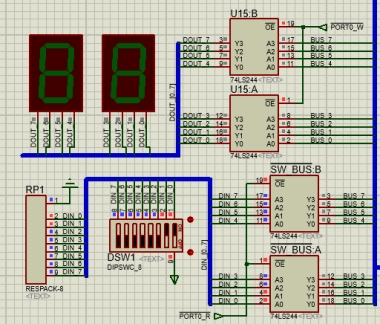

2.6 存储器设计

存储器地址总线 8 位,地址空间 256 字节(00HFFH)。分配其中低半区(00H7FH)为 ROM 存储区(128 字节),高半区(80H~FFH)为 RAM 存储区(128 字节),如下图所示,存储器 ROM 和 RAM 共用一个地址寄存器 AR,两个存储器共用

![]()

信号作为存储器读信号,由地址最高位 A7 来作为两个存储器的片选信号。RAM 存储器是可读写存储器,存放临时的数据。而 ROM 是只读存储器,存放程序和常量(采用堆栈操作指令访问)。因此,CPU 程序和常量的存储容量最大是 128 字节,若程序和常量的代码量超过了 128 字节,则会越界出错。同样的,因为只有存储器 RAM 允许写入,所以当存储器写信号

![]()

=0 的时候,只有地址范围[80H,FFH]是允许写入操作的;对地址范围[00H,7FH]的存储器单元进行写入操作是非法的。

图 2.6-1 存储器(ROM/RAM)及指令寄存器 IR 电路

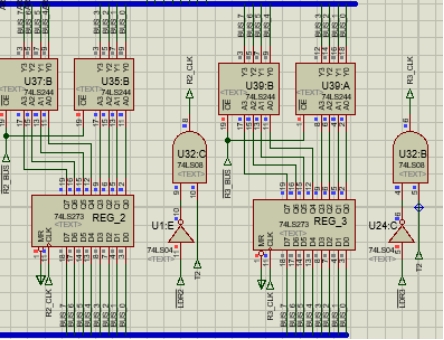

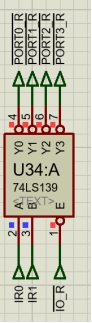

2.7 寄存器和 IO 端硬件设计

CPU 共有四个并列的通用寄存器 R0~R3,因为在 CPU 指令中,指令执行的操作数来源可能是逻辑寄存器 RA 或 RB 的输出,但是指令执行的结果只能是打入寄存器 RA。所以,在下图中,微操作信号

![]()

和

![]()

分别根据指令的 I3I2 位和 I1I0 位选择通用寄存器(R0~ R3)之一输出操作数(注:微操作信号

![]()

和

![]()

不允许出现在同一个微指令中,避免出现冲突);而微操作信号

![]()

直接根据指令的 I3I2 位指定打入的通用寄存器。

图 2.7-1 通用寄存器及寄存器选择电路图

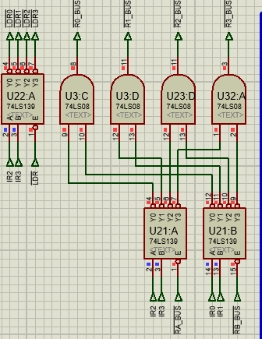

下图所示是 CPU 的 IO 接口外挂设备,采用拨码开关 DSW1 模拟输入设备,数码显示管模拟输出设备。若当前运行 IN 指令,则信号

![]()

=0, 外围设备输入数据到 BUS 总线。在下图右中,根据 IN 指令的 I1I0 位产生 IO 输入使能信号

![]()

,可以指定 4 个输入设备,同样的,若当前运行 OUT/OUTA 指令,则信号

![]()

=0, BUS 总线输出数据到 IO 接口外围设备,根据指令的 I0 位产生 IO 输出使能信号

![]()

,可以指定 2 个输出设备,而指令的 I1 位作为地址锁存信号 ALE。若 ALE=1,则输出地址(OUTA 指令);若 ALE=0,则输出数据(OUT 指令),如下图右所示。注意:

![]()

信号是打入目标部件的使能信号,时序须与其它打入信号保持一致,仅在 T2 周期有效。

图 2.7-2 外围设备及 IO 接口电路图

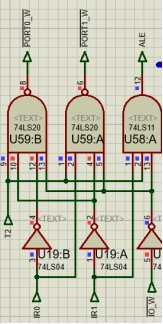

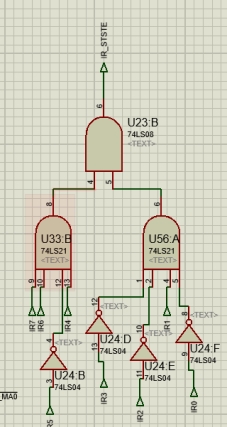

2.8 跳转逻辑电路硬件设计

下图所示,跳转指令“0001”执行的时候,微操作信号

![]()

首先根据指令的 I3I2 位译码,判断是执行无条件跳转指令(微操作信号

![]()

=0)还是有条件跳转指令 JC、JZ 和 JS(对应的微操作信号 Jx=0)。值得注意的是,在有条件跳转指令 JCR、JZR、JSR 的执行周期最后一条微指令[11111]处,倘若最后不跳转,则因为 JxR 是单字节指令。所以,此处不但需要不打入 PC,而且还必须禁止 PC+1。因此,只有在地址[11111]的微指令执行的时候,使用微操作信号 JMP_CLR 和

![]()

的逻辑“与”来决定是否运行 PC_CLK=1(即 PC+1 操作)。

图 2.8-1 跳转选择电路及 JS 跳转条件判断图

如上右图中为循环计数器,当计数到 6 时,此时

![]()

=0,表明 JS 需要跳转,即退出循环。

如下图为进位保存及跳转条件判断逻辑电路图,上边的进位保存主要用于 BCD 码运算时保存,由 IR 指令为其中一个条件控制,

![]()

主要是用于保存运算过后的进位不变,直到下一次运算,将进位传递。下边是 JZ,JC 的跳转判断条件,主要是 BCD 码运算后的结果是否需要调整的判断跳转,当低四位进行 BCD 码运算,如果结果小于 10 且没有进位,则不需要 +6 调整,

![]()

=0,表明需要跳转,高四位同上。

图 2.8-2 JZ/JC 跳转条件判断图

2.9 算术逻辑运算控制电路设计

图 2.9-1 算术逻辑运算控制电路图

上图为算术逻辑运算逻辑控制电路图,其中 ALU_CN 端中与运算右边为 BCD 码运算时进位输出入端,其他左边实现共用微指令,微指令寄存器 MDR1 的输出译码电路采用了硬连线逻辑来实现以下单操作数指 令:递增(INC)递减(DEC)、取反(NOT)和直通(THR),以及决定算术运算指令所需的 CN 操作信号(最低进位,用于补码运算的“求补 +1”操作)。当执行指令 SOP 时,运算器 74LS181 控制端[S3,S2,S1,S0,M,CN]=[0,0,0,0,0,0]。因为 SOP_EN=1,所以 I1 位修改 M ,I0 位修改 S3~S0 和 CN(I4=0,不影响 CN),如下表所示:

|

CPU 指令 |

OP 码(I7I6I5I4) |

S3S2S1S0 |

M |

CN |

I4 |

I1 |

I0 |

|

|

SOP |

INC |

0010 |

0000 |

0 |

0 |

0 |

0 |

0 |

|

DEC |

1111 |

0 |

1 |

0 |

0 |

1 |

||

|

NOT |

0000 |

1 |

X |

0 |

1 |

0 |

||

|

THR |

1111 |

1 |

X |

0 |

1 |

1 |

OP 码的 I4 则用来指定双操作数运算指令 ADD 和 SUB 的 CN 操作信号,如下表所示:

|

CPU 指令 |

OP 码(I7I6I5I4) |

S3S2S1S0 |

M |

CN |

I4 |

|

ADD/ADDI |

1101 |

1001 |

0 |

1 |

1 |

|

SUB/SUBI |

1100 |

0110 |

0 |

0 |

0 |

三、详细设计

3.1 模型机指令系统设计

表 3.1-1 完善后的指令系统

|

助记符 |

功能 |

格式 |

||

|

NOP; |

空指令/延时 4 个 T |

0000 |

XX |

XX |

|

HLT; |

停机 |

0000 |

00 |

01 |

|

LYS,RA |

00YS1YS2 0000->RA |

1010 |

RA |

00 |

|

LAD RA, [ADDR]; |

[ADDR]->RA |

1000 |

RA |

00 |

|

ADDR |

||||

|

POP RA, [RB]; |

[RB]->RA |

1000 |

RA |

RB |

|

STO RA, [ADDR]; |

RA->[ADDR] |

1001 |

RA |

00 |

|

ADDR |

||||

|

PUSH RA, [RB]; |

RA->[RB] |

1001 |

RA |

RB |

|

ADD RA, RB; |

(RA)+(RB)->RA |

1101 |

RA |

RB |

|

ADDI RA, IMM; |

(RA)+IMM->RA |

1101 |

RA |

00 |

|

IMM |

||||

|

SUB RA, RB; |

(RA)-(RB)->RA |

1100 |

RA |

RB |

|

SUBI RA, IMM; |

(RA)- IMM ->RA |

1100 |

RA |

00 |

|

IMM |

||||

|

XOR RA, RB; |

(RA) ⊕(RB)->RA |

1011 |

RA |

RB |

|

XORI RA, IMM; |

(RA) ⊕IMM->RA |

1011 |

RA |

00 |

|

IMM |

||||

|

OR RA, RB; |

(RA)∨(RB)->RA |

1111 |

RA |

RB |

|

ORI RA, IMM; |

(RA)∨IMM->RA |

1111 |

RA |

00 |

|

IMM |

||||

|

JMPR [RB]; |

[RB] ->PC |

0001 |

00 |

RB |

|

JMP ADDR; |

ADDR->PC |

0001 |

00 |

00 |

|

ADDR |

||||

|

JZR [RB]; |

IF ZF=1, [RB] ->PC |

0001 |

10 |

RB |

|

JZ ADDR; |

IF FIRST-PAN=1, ADDR->PC |

0001 |

10 |

00 |

|

ADDR |

||||

|

JCR [RB]; |

IF CF=1, [RB] ->PC |

0001 |

01 |

RB |

|

JC ADDR; |

IF SECOND_PAN=1 ADDR->PC |

0001 |

01 |

00 |

|

ADDR |

||||

|

JSR [RB]; |

IF SF=1, [RB] ->PC |

0001 |

11 |

RB |

|

JS ADDR |

IF ALU_S=1,ADDR->PC |

0001 |

11 |

00 |

|

ADDR |

||||

|

SET RA, DATA; |

DATA->RA |

0011 |

RA |

XX |

|

DATA |

||||

|

INC RA; |

(RA)+1->RA |

0010 |

RA |

00 |

|

DEC RA; |

(RA)-1->RA |

0010 |

RA |

01 |

|

NOT RA; |

#(RA) ->RA |

0010 |

RA |

10 |

|

THR RA; |

(RA)->RA |

0010 |

RA |

11 |

|

IN RA, Px; |

(PORTx)->RA |

0100 |

RA |

PORTx |

|

OUT RA, Px; |

RA->(PORTx) |

0101 |

RA |

0/PORTx |

|

OUTA RA, Px; |

RA->(PORTx) |

0101 |

RA |

1/PORTx |

|

LPSTA 6 |

Looptimes=0;strat loop,6 次 |

0110 |

00 |

00 |

|

LPINC |

Looptimes++ |

0110 |

10 |

00 |

|

EXCESS%3 RA; |

RA%3->YS1,YS2 |

0111 |

RA |

xx |

说明(具体思路参照方案论证中的指令格式设计):

xx 表示任意;

ADDR 表示地址;

DATA 表示数据;

低四位进行 BCD 码运算和(R0 低四位)<10,同时没有进位,说明不需要调整,FIRST_PAN=1;

高四位进行 BCD 码运算和(R0 高四位)<10,同时没有进位,说明不需要调整,SECOND_PAN=1;

ALU_S 为循环次数到 6 的判断,当此时 looptimes=6,ALU_S=1;

对 3 取余指令的结合使用,EXCESS%3 Rx,LYS,Ry;两个指令结合实现功能为 RX%3->RY

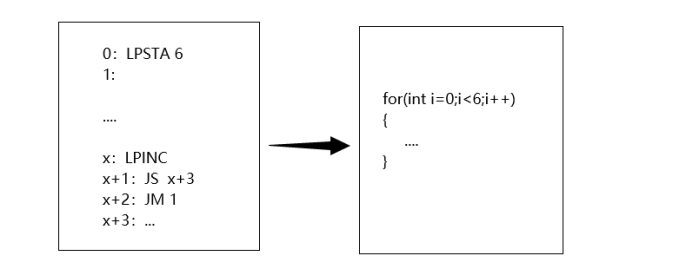

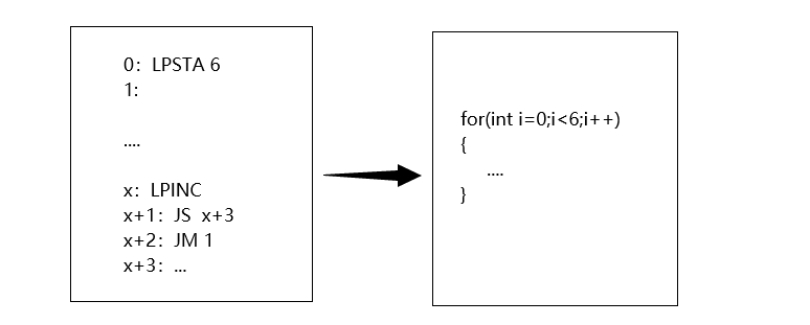

循环指令的结合使用,如下说明:

3.2 微指令系统设计

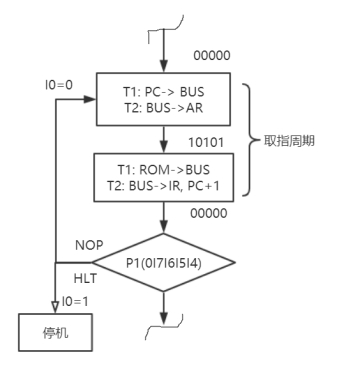

(1)取指及系统微指令

除了空指令(NOP)和停机指令(HLT)以外,所有的 CPU 指令都包括了取指周期和执行周期。因为 NOP 指令 OP 码为“0000”,所以取指周期末尾 P1(0I7I6I5I4)译码的时候,直接返回取指周期(取下一条指令),没有执行周期。而 HLT 指令与 NOP 指令完全相同,唯一不同是在取指周期后 CPU 硬件停机,需要手动 RESET“重启”才能跳出停机状态,进入下一条指令。

图 3.2-1 取指周期及系统指令的微程序流程图

其中每个方框在时间上表示一个微指令周期,包括 T1 和 T2 两个节拍;在空间上表示数据从某个源部件经过总线 BUS 到达另一个目标部件的路径。每个方框的右上方是该微指令在控制存储器中的地址,右下方则是下一条微指令的地址。下表则列出了上图所对应的取指周期(即 NOP/HLT 指令)的微指令代码:

表 3.2-1 微指令代码表(取指周期)

|

Addr |

S3-S0 |

M |

SOP_EN |

SHT_EN |

LDYS |

PC_INC |

->BUS |

BUS-> |

JMP_CLR |

P1-P3 |

uA4-uA0 |

|

00000 |

0000 |

0 |

0 |

0 |

0 |

0 |

100 |

100 |

0 |

000 |

10101 |

|

10101 |

0000 |

0 |

0 |

0 |

0 |

1 |

010 |

010 |

0 |

100 |

00000 |

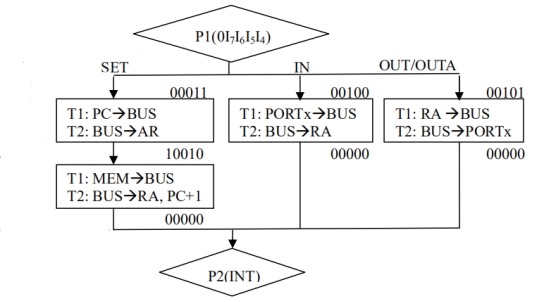

(2)寄存器及 I/O 操作微程序

下图是 SET 指令和 IN、OUT/OUTA 指令的微程序流程图,其中(P1 判断前)取指周期和若有中断触发的(P2 判断后)中断处理周期参见上图 3.2-1。此外,OUT 和 OUTA 指令的微指令序列完全相同,由硬件逻辑区分。

图 3.2-2 寄存器及 I/O 操作指令的微程序流程图

下表列出了上图对应的寄存器操作指令 SET 及 I/O 操作指令 IN、OUT/OUTA 的微指令代码。

表 3.2-2 微指令代码表(SET/IN/OUT 指令)

|

Addr |

S3-S0 |

M |

SOP_EN |

SHT_EN |

LDYS |

PC_INC |

->BUS |

BUS-> |

JMP_CLR |

P1-P3 |

uA4-uA0 |

|

00011 |

0000 |

0 |

0 |

0 |

0 |

0 |

100 |

100 |

0 |

000 |

10010 |

|

10010 |

0000 |

0 |

0 |

0 |

0 |

1 |

010 |

001 |

0 |

010 |

00000 |

|

00100 |

0000 |

0 |

0 |

0 |

0 |

0 |

110 |

001 |

0 |

010 |

00000 |

|

00101 |

0000 |

0 |

0 |

0 |

0 |

0 |

001 |

011 |

0 |

010 |

00000 |

(3)存储器及堆栈操作微指令

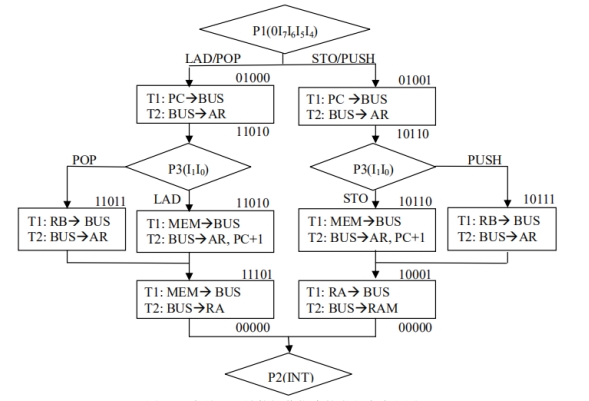

下图是存储器操作指令 LAD、STO 和堆栈操作指令 POP、PUSH 的微程序流程图。从图中可以看出,POP 指令只需要[11011]和[11101]两条微指令就够了,但是为了节省 OP 码,POP 和 LAD 指令共用 OP 码“1000”,即共用第一条微指令[01000](即使 POP 指令其实并不需要微指令[01000])。从而可以在第一条微指令的末尾采用 P3(I1I0)判断 LAD 和 POP 指令的不同路径:若 I1I0=00,执行直接根据第二字节目标地址 ADDR 从存储器取数的双字节 LAD 指令;若 I1I0≠00,则执行根据逻辑寄存器 RB(R1~R3)内容指定的目标地址从存储器取数的单字节 POP 指令。STO 和 PUSH 指令的关系类似 LAD 和 POP 指令。

图 3.2-3 存储器及堆栈操作指令的微程序流程图

下表列出的存储器指令 LAD/STO 和堆栈指令 POP/PUSH 的微指令代码:

表 3.2-3 微指令代码表(LAD/POP/STO/PUSH 指令)

|

Addr |

S3-S0 |

M |

SOP_EN |

SHT_EN |

LDYS |

PC_INC |

->BUS |

BUS-> |

JMP_CLR |

P1-P3 |

uA4-uA0 |

|

01000 |

0000 |

0 |

0 |

0 |

0 |

0 |

100 |

100 |

0 |

001 |

11010 |

|

11010 |

0000 |

0 |

0 |

0 |

0 |

1 |

010 |

100 |

0 |

000 |

11101 |

|

11011 |

0000 |

0 |

0 |

0 |

0 |

0 |

101 |

100 |

0 |

000 |

11101 |

|

11101 |

0000 |

0 |

0 |

0 |

0 |

0 |

010 |

001 |

0 |

010 |

00000 |

|

01001 |

0000 |

0 |

0 |

0 |

0 |

0 |

100 |

100 |

0 |

001 |

10110 |

|

10110 |

0000 |

0 |

0 |

0 |

0 |

1 |

010 |

100 |

0 |

000 |

10001 |

|

10111 |

0000 |

0 |

0 |

0 |

0 |

0 |

101 |

100 |

0 |

000 |

10001 |

|

10001 |

0000 |

0 |

0 |

0 |

0 |

0 |

001 |

101 |

0 |

010 |

00000 |

(4)跳转系列微指令

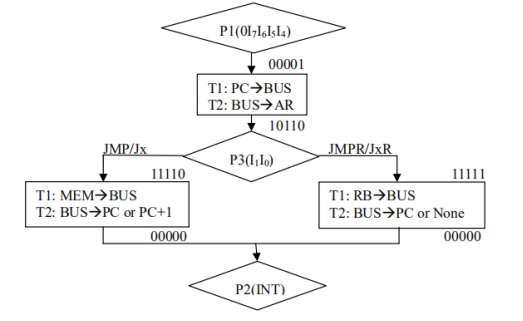

下图是 JMPR/JxR 指令和 JMP/Jx 指令的微程序流程图。从图中可以看出,JMPR/JxR 指令只需要[11111]微指令就够了,但是为了节省 OP 码,两条跳转指令共用 OP 码“0001”,即共用第一条微指令[00001](即使 JMPR/JxR 指令其实并不需要 [00001] 微指令)。从而可以在第一条微指令的末尾采用 P3(I1I0)区分两种跳转指令的不同路径:若 I1I0=00,执行直接根据第二字节目标地址 ADDR 跳转的双字节 JMP/Jx 指令;若 I1I0≠00,则执行根据逻辑寄存器 RB(R1~R3)内容指定的目标地址跳转的单字节 JMPR/JxR 指令。

图 3.2-4 跳转系列指令的微程序流程图

表 3.2-4 微指令代码表(JMP/JMPR/Jx/JxR 指令)

|

Addr |

S3-S0 |

M |

SOP_EN |

SHT_EN |

LDYS |

PC_INC |

->BUS |

BUS-> |

JMP_CLR |

P1-P3 |

uA4-uA0 |

|

00001 |

0000 |

0 |

0 |

0 |

0 |

0 |

100 |

100 |

0 |

001 |

11110 |

|

11110 |

0000 |

0 |

0 |

0 |

0 |

1 |

010 |

111 |

0 |

010 |

00000 |

|

11111 |

0000 |

0 |

0 |

0 |

0 |

1 |

101 |

111 |

1 |

010 |

00000 |

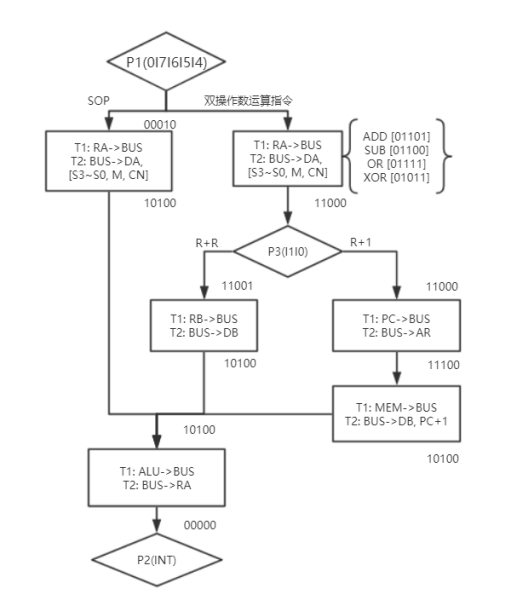

(5)算术逻辑运算系列微指令

其微程序流程图如下图所示。为了节省微指令,所有的运算指令都在第一条微指令期间锁存 74181 运算器的控制端逻辑[S3,S2,S1,S0,M,CN]。此外,四种双操作数的运算指令都采取在第一条微指令的末尾采用 P3(I1I0)判断双字节和单字节指令的不同路径:若 I1I0=00,执行操作数分别来自逻辑寄存器 RA 和指令第二字节(立即数 IMM)的双字节指令;若 I1I0≠00,则执行操作数全部来自寄存器的单字节指令。

图 3.2-5 算术逻辑运算系列指令的微程序流程图

表 3.2-5 微指令代码表(SOP 及双操作数运算指令)

|

Addr |

S3-S0 |

M |

SOP_EN |

SHT_EN |

LDYS |

PC_INC |

->BUS |

BUS-> |

JMP_CLR |

P1-P3 |

uA4-uA0 |

|

00010 |

0000 |

0 |

1 |

0 |

0 |

0 |

001 |

110 |

0 |

000 |

10100 |

|

01101 |

1001 |

0 |

0 |

0 |

0 |

0 |

001 |

110 |

0 |

001 |

11000 |

|

01100 |

0110 |

0 |

0 |

0 |

0 |

0 |

001 |

110 |

0 |

001 |

11000 |

|

01110 |

1011 |

1 |

0 |

0 |

0 |

0 |

001 |

110 |

0 |

001 |

11000 |

|

01111 |

1110 |

1 |

0 |

0 |

0 |

0 |

001 |

110 |

0 |

001 |

11000 |

|

01011 |

0110 |

1 |

0 |

0 |

0 |

0 |

001 |

110 |

0 |

001 |

11000 |

|

11000 |

0000 |

0 |

0 |

0 |

0 |

0 |

100 |

100 |

0 |

000 |

11100 |

|

11100 |

0000 |

0 |

0 |

0 |

0 |

1 |

010 |

110 |

0 |

000 |

10100 |

|

11001 |

0000 |

0 |

0 |

0 |

0 |

0 |

101 |

110 |

0 |

000 |

10100 |

|

10100 |

0000 |

0 |

0 |

0 |

0 |

0 |

011 |

001 |

0 |

010 |

00000 |

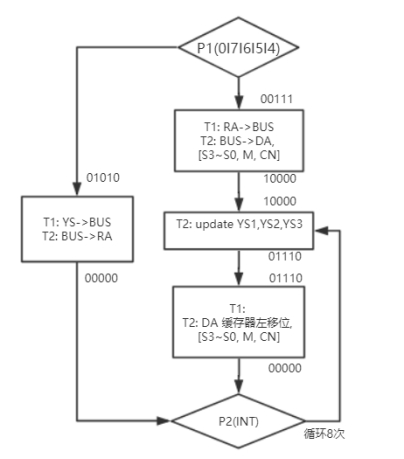

(6)对 3 取余微指令

其微程序流程图如下图所示,有三段微指令构成取余,一是将寄存器的数放置到移位寄存器中,而是对其中一个数值一步取余,三是移位并判断是否运行了 8 次,处理完输入的 8 个二进制,在配合硬件逻辑计数退出。

图 3.2-6 对 3 取余系列指令的微程序流程图

表 3.2-6 微指令代码表(EXCESS3 及 LYS 运算指令)

|

Addr |

S3-S0 |

M |

SOP_EN |

SHT_EN |

LDYS |

PC_INC |

->BUS |

BUS-> |

JMP_CLR |

P1-P3 |

uA4-uA0 |

|

00111 |

0000 |

0 |

0 |

0 |

0 |

0 |

001 |

110 |

0 |

000 |

10000 |

|

10000 |

0000 |

0 |

0 |

0 |

1 |

0 |

000 |

000 |

0 |

000 |

01110 |

|

01110 |

0000 |

0 |

0 |

1 |

0 |

0 |

000 |

110 |

0 |

010 |

00000 |

|

01010 |

0000 |

0 |

0 |

0 |

0 |

0 |

000 |

001 |

0 |

010 |

00000 |

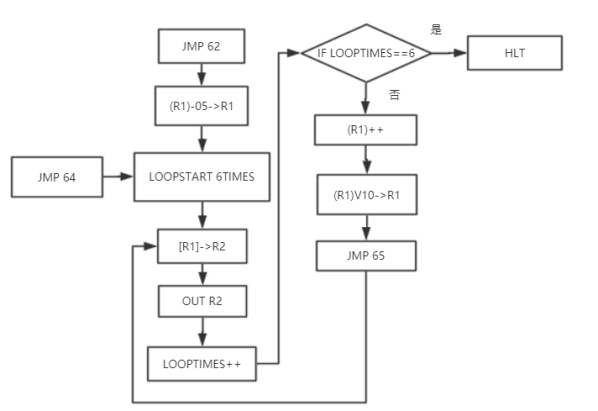

(7)循环系列微指令

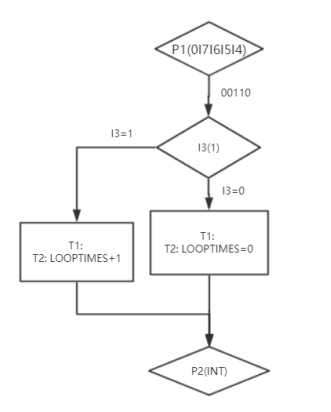

其微程序流程图如下图所示,为了节省微指令,LPSTA 与 LPINC 共用一条微指令,以 I3 的值区分,主要通过硬件实现。当 LOOP=1 时,处于循环状态,如果 I3=0,则清空循环计数;当 I3=1 时,则循环计数加 1。

图 3.2-7 循环系列指令的微程序流程图

表 3.2-7 微指令代码表(LPSTA/LPINC 运算指令)

|

Addr |

S3-S0 |

M |

SOP_EN |

SHT_EN |

LDYS |

PC_INC |

->BUS |

BUS-> |

JMP_CLR |

P1-P3 |

uA4-uA0 |

|

00110 |

0000 |

0 |

0 |

0 |

0 |

0 |

111 |

000 |

0 |

010 |

00000 |

四、基于模型机指令系统的应用程序设计

任务:将“自己的学号(12 位)”和 “自己的身份证号码后 12 位(最后 1 位为 X 的以 0 替换)”以压缩 BCD 格式(4 位二进制表示 1 位十进制数)共 12 个字节保存在程序存储器 ROM 中,程序启动后,根据拨码开关 DSW1 输入值执行下面操作:

DSW1 输入值 % 3 = 0 将保存到程序存储器中的“自己的学号”写入数据存储器 RAM 中,写入 RAM 的相对偏移地址由拨码开关 DSW1 输入值(HEX)决定。

DSW1 输入值 % 3 = 1 将保存到程序存储器中的“自己的身份证号”写入数据存储器 RAM 中,写入 RAM 的相对偏移地址由拨码开关 DSW1 输入值(HEX)决定。

DSW1 输入值 % 3 = 2 将保存到程序存储器中的“自己的学号”和 “自己的身份证号”进行 BCD 码算术相加,然后将结果(6 个字节的 BCD 码)写入数据存储器 RAM 中,写入 RAM 的相对偏移地址由拨码开关 DSW1 输入值(HEX)决定。

之后从 RAM 中读取该结果,送到 DOUT 显示,每个字节的显示时间不超过 0.5 秒。

两数算术相加时要考虑到低位向高位的进位,如:

(学号)201830013463 + (身份证号)199809293216 = 401639306679

程序设计主要分为三步:

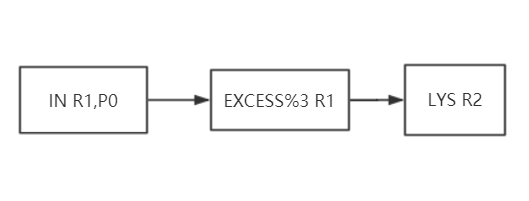

(1)从输入端取出数据到 R1,对 R1 数据进行对 3 取余操作,将结果打入 R2 中。

图 4-1 程序流程图 1

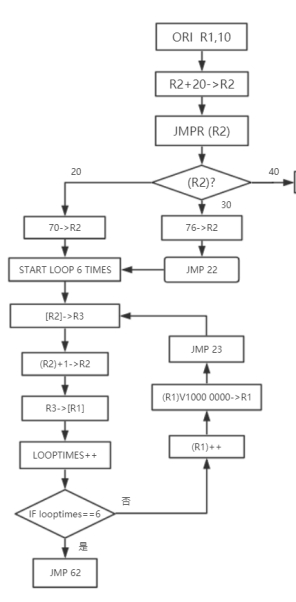

(2) 首先对输入的值(R1)进行预处理,作为 RAM 输入值的地址,将其与 10(十六进制)做或运算,保证地址范围合理;对取余的结果即 R2 中的值(余数为 0,值为 00;余数为 1,值为 10,余数为 2,值为 20)加 20(十六进制),然后利用跳转指令跳转到 R2 值代表的地址中,思路就是将这三种处理方式分别分开放置到不同地址中,如下为将学号或者身份证号或者两者运算后的结果存储到 RAM 操作流程图:

图 4-2 程序流程图 2

如上流程图,是将学号和身份证号放置到 RAM 中的操作,首先就是根据余数选择,将学号或者身份证号地址放置到 R2 中,然后循环以 R2 为地址从存储器中取出值放置到 R1 地址的存储器中,然后地址减一,直到全部存储到 RAM 中跳转到下一步结束。

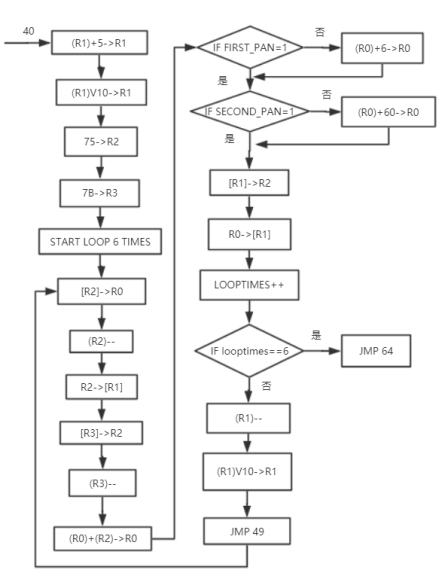

图 4-3 程序流程图 3

如上流程图是将学号和身份证做

运算后将结果存储到 RAM 中,简单思路就是先直接做加法运算,然后再根据进位做跳转判断去调整,由于寄存器不够,这里先取完学号数据后再将学号地址存放到 RAM 中,然后运算完后再将学号地址取出来返回 R2 中,如下:

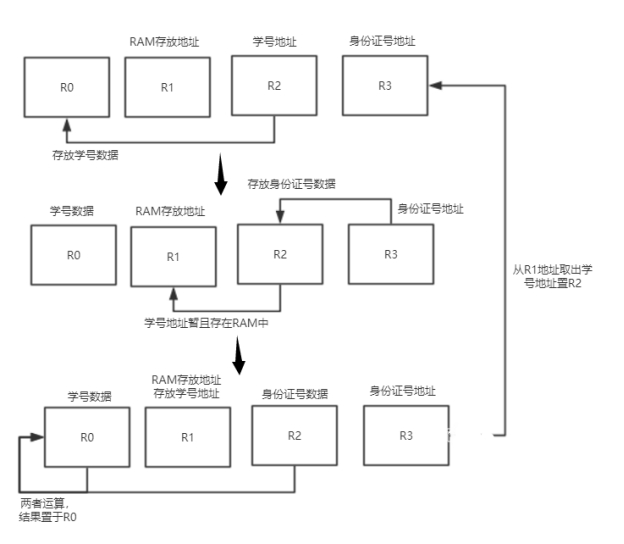

图 4-4 寄存器中的数据地址说明图

(3) 第三步就是将存放在 RAM 地址中的数据逐个按顺序取出并在晶体管显示出来,如下操作流程图:

图 4-5 程序流程图 4

(具体程序代码实现参照附件)

学号和身份证号在 ROM 的存储首地址是 70 和 76。

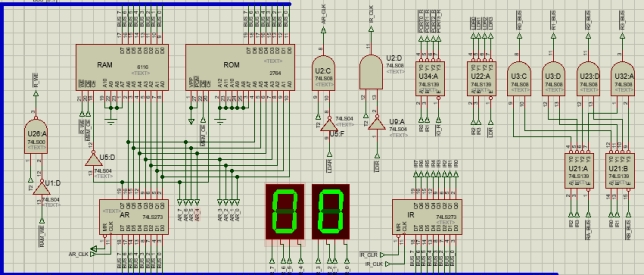

五、本课程设计的验收方法

任务:

在 preteus8 中运行设计的仿真电路

相关数据:学号:20183018xxxx 身份证号后 12 位:200000128xxxx

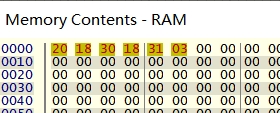

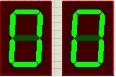

(1)将输入值置 0(对 3 取余为 0 的值都可)验证 DSW1 输入值 % 3 = 0 时的运行结果:如下图 5-1 是晶体管按顺序显示学号的结果,图 5-2 是 RAM 中存储的结果:

图 5-1 取余为 0 的显示图

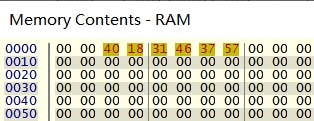

图 5-2 RAM 中存储数据图

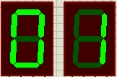

(2)将输入值置 1(对 3 取余为 1 的值都可)验证 DSW1 输入值 % 3 = 1 时的运行结果:如下图 5-3 是晶体管按顺序显示学号的结果,图 5-4 是 RAM 中存储的结果:

图 5-3 取余为 1 的显示图

图 5-4 RAM 中存储数据图

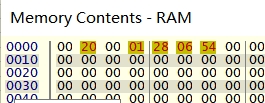

(3)将输入值置 2(对 3 取余为 2 的值都可)验证 DSW1 输入值 % 3 = 2 时的运行结果:

201830183103+200001280654=4018 3146 3757

如下图 5-5 是晶体管按顺序显示学号的结果,图 5-6 是 RAM 中存储的结果:

图 5-5 取余为 2 的显示图

图 5-6 RAM 中存储数据图

六、完善后的指令系统

|

助记符 |

功能 |

格式 |

||

|

NOP; |

空指令/延时 4 个 T |

0000 |

XX |

XX |

|

HLT; |

停机 |

0000 |

00 |

01 |

|

LYS,RA |

00YS1YS2 0000->RA |

1010 |

RA |

00 |

|

LAD RA, [ADDR]; |

[ADDR]->RA |

1000 |

RA |

00 |

|

ADDR |

||||

|

POP RA, [RB]; |

[RB]->RA |

1000 |

RA |

RB |

|

STO RA, [ADDR]; |

RA->[ADDR] |

1001 |

RA |

00 |

|

ADDR |

||||

|

PUSH RA, [RB]; |

RA->[RB] |

1001 |

RA |

RB |

|

ADD RA, RB; |

(RA)+(RB)->RA |

1101 |

RA |

RB |

|

ADDI RA, IMM; |

(RA)+IMM->RA |

1101 |

RA |

00 |

|

IMM |

||||

|

SUB RA, RB; |

(RA)-(RB)->RA |

1100 |

RA |

RB |

|

SUBI RA, IMM; |

(RA)- IMM ->RA |

1100 |

RA |

00 |

|

IMM |

||||

|

XOR RA, RB; |

(RA) ⊕(RB)->RA |

1011 |

RA |

RB |

|

XORI RA, IMM; |

(RA) ⊕IMM->RA |

1011 |

RA |

00 |

|

IMM |

||||

|

OR RA, RB; |

(RA)∨(RB)->RA |

1111 |

RA |

RB |

|

ORI RA, IMM; |

(RA)∨IMM->RA |

1111 |

RA |

00 |

|

IMM |

||||

|

JMPR [RB]; |

[RB] ->PC |

0001 |

00 |

RB |

|

JMP ADDR; |

ADDR->PC |

0001 |

00 |

00 |

|

ADDR |

||||

|

JZR [RB]; |

IF ZF=1, [RB] ->PC |

0001 |

10 |

RB |

|

JZ ADDR; |

IF FIRST-PAN=1, ADDR->PC |

0001 |

10 |

00 |

|

ADDR |

||||

|

JCR [RB]; |

IF CF=1, [RB] ->PC |

0001 |

01 |

RB |

|

JC ADDR; |

IF SECOND_PAN=1 ADDR->PC |

0001 |

01 |

00 |

|

ADDR |

||||

|

JSR [RB]; |

IF SF=1, [RB] ->PC |

0001 |

11 |

RB |

|

JS ADDR |

IF ALU_S=1,ADDR->PC |

0001 |

11 |

00 |

|

ADDR |

||||

|

SET RA, DATA; |

DATA->RA |

0011 |

RA |

XX |

|

DATA |

||||

|

INC RA; |

(RA)+1->RA |

0010 |

RA |

00 |

|

DEC RA; |

(RA)-1->RA |

0010 |

RA |

01 |

|

NOT RA; |

#(RA) ->RA |

0010 |

RA |

10 |

|

THR RA; |

(RA)->RA |

0010 |

RA |

11 |

|

IN RA, Px; |

(PORTx)->RA |

0100 |

RA |

PORTx |

|

OUT RA, Px; |

RA->(PORTx) |

0101 |

RA |

0/PORTx |

|

OUTA RA, Px; |

RA->(PORTx) |

0101 |

RA |

1/PORTx |

|

LPSTA 6 |

Looptimes=0;strat loop,6 次 |

0110 |

00 |

00 |

|

LPINC |

Looptimes++ |

0110 |

10 |

00 |

|

EXCESS%3 RA; |

RA%3->YS1,YS2 |

0111 |

RA |

xx |

说明(具体思路参照方案论证中的指令格式设计):

xx 表示任意;

ADDR 表示地址;

DATA 表示数据;

低四位进行 BCD 码运算和(R0 低四位)<10,同时没有进位,说明不需要调整,FIRST_PAN=1;

高四位进行 BCD 码运算和(R0 高四位)<10,同时没有进位,说明不需要调整,SECOND_PAN=1;

ALU_S 为循环次数到 6 的判断,当此时 looptimes=6,ALU_S=1;

对 3 取余指令的结合使用,EXCESS%3 Rx,LYS,Ry;两个指令结合实现功能为 RX%3->RY

循环指令的结合使用,如下说明:

七、课程设计总结

声明:本次课设在已提供的模板基础上加入自己的设计完善。

八、参考文献

[1]白中英,戴志涛.计算机组成原理(第五版 立体化教材). 科学出版出版社.

♻️ 资源

大小: 3.12MB

➡️ 资源下载:https://download.csdn.net/download/s1t16/87415790

注:更多内容可关注微信公众号【神仙别闹】,如当前文章或代码侵犯了您的权益,请私信作者删除!

AtomGit 是由开放原子开源基金会联合 CSDN 等生态伙伴共同推出的新一代开源与人工智能协作平台。平台坚持“开放、中立、公益”的理念,把代码托管、模型共享、数据集托管、智能体开发体验和算力服务整合在一起,为开发者提供从开发、训练到部署的一站式体验。

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)