小刘同学的 virtuoso IC 618 版图初学

版图初体验

一键AI生成摘要,助你高效阅读

问答

·

前言

这个是我初步学习版图的一个记录帖。

目录

快捷键

| 按键 | 功能 |

|---|---|

| Q | 修改元件参数 |

| E | 显示设置(设置最小移动步长) |

| R | 画矩形 |

| O | 画过孔 |

| P | 画path |

| K | 画尺子(shift+K 取消layout上所有尺子) |

| M | 移动器件 |

| S | 伸缩,调整器件长度 |

| L | 加标签(标记vdd gnd vin vout等) |

| shift+F | 显示元件内部图(ctrl+F 显示元件上层图) |

(有别的有用的后再添加了)

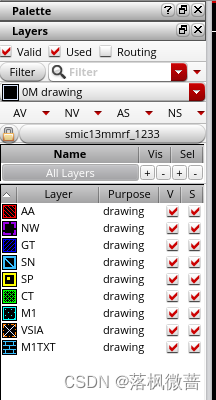

图层

我使用的是smic 0.18μm工艺

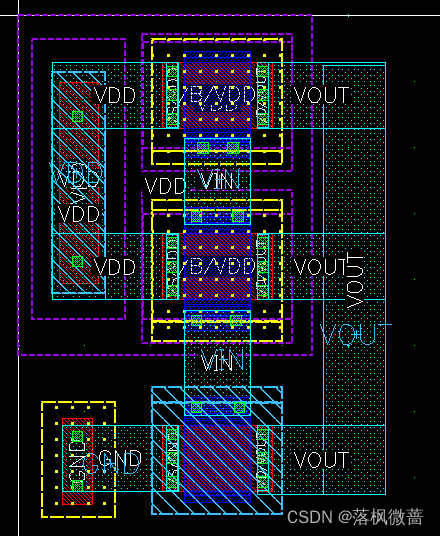

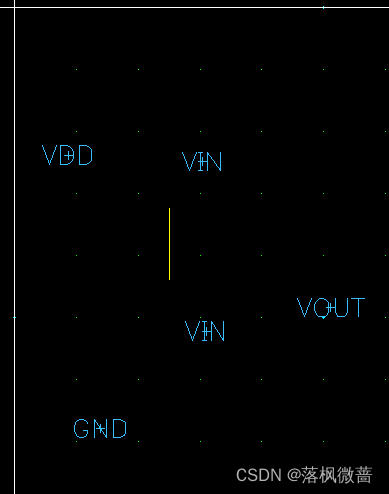

先给大家看一下我画的简单版图吧。

至于一些画图,DRC与LVS的操作别的地方太多了,我就不写了,我就写一些别人不太会介绍的玩意吧,感觉这才是阻碍我之前对版图探索的东西。

这个版图结构出自(这个帖里面也有DRC,LVS的介绍):

Cadence Virtuoso IC617从原理图建立器件和生成版图

我的模仿图:

这个是画这个版图用到的图层:

下面来一一介绍:

| 图层 | 内容 |

|---|---|

| 1、NW | nwell n阱 |

| 2、AA(OD) | 有源区,用来画源,漏或者bulk区 |

| 3、GT | 用来画栅 |

| 4、SN | N注入区 |

| 5、SP | P注入区 |

| 6、CT | 画接触孔 |

| 7、M1(Mn) | 画金属连线 |

| 8、M1TXT(MnTXT) | 放金属层的标签 |

下面给大家一个图层一个图层的看画了的内容,就知道什么意思了:

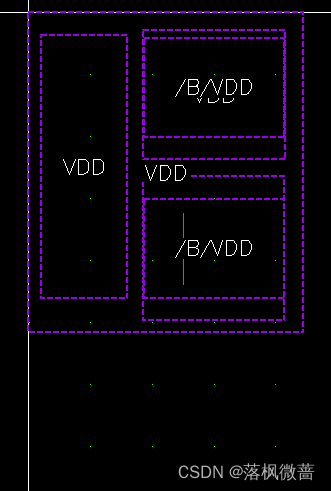

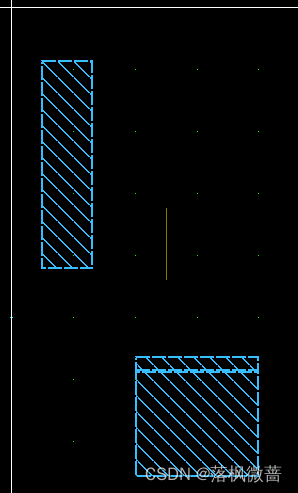

1、NW(nwell n阱,PMOS需要):

其实这个只看最外层就行了,里面的所有器件都需要NWELL,只不过因为PMOS的版图是导入的模型不是自己画的,它的内部我改不了。最后一个大的直接覆盖内部小的。

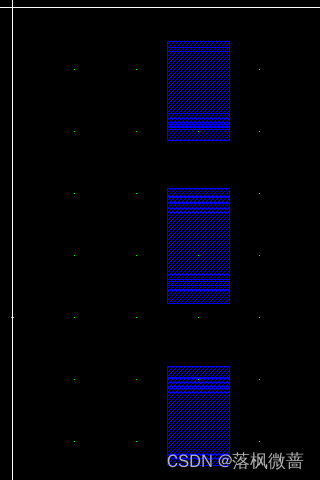

2、AA(有源区):

3、GT(栅):

4、SN(N注入区):

5、SP(P注入区):

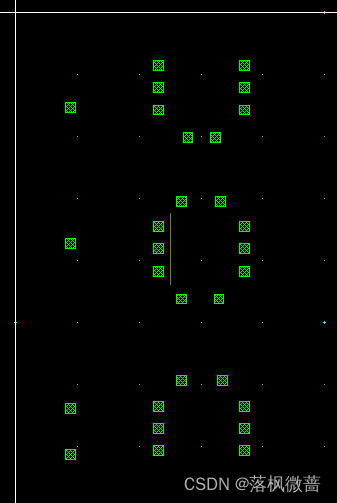

6、CT(接触孔):

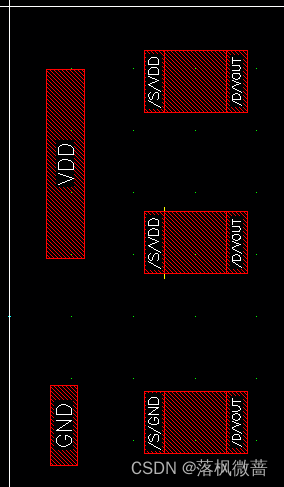

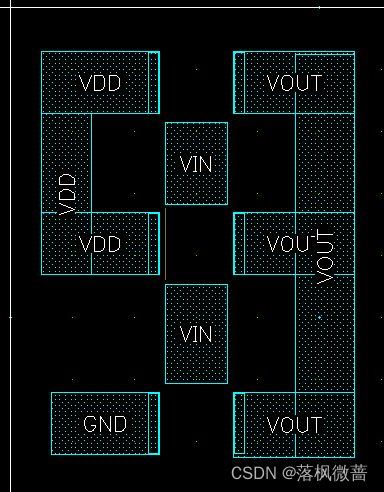

7、M1(金属连线):

8、M1TXT(M1金属层标签):

PS:

1、VSIA层不知道干嘛用的,我也没用到,应该是导入MOS管时的层次,我也不知道有什么用。

2、可以从版图上看到,就算一个区域画的面积不够了,可以再补,可以不用stretch拉长到自己想要的大小。因为是层次结构,最后光刻板看的是那一层图形最大的那个面积,不会出现交叠现象。

3、不同的工艺对以上层次的命名不同,比如AA叫OD,GT叫PO,CT叫CO,等等等等。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)