【Cadence Virtuoso】番外:如何根据仿真获取不同工艺库的MOS参数

为了后续各种电路的分析与计算,我们需要知道自己使用的工艺库基础MOS器件的相关参数,如VTH、μCox、λ等,本篇记录了如何通过在IC617中仿真并计算获取这些参数,工艺库使用的是TSMC 65nm工艺库。

前言

本博文为个人在学习Cadence Virtuoso时的记录,巩固自己学习的同时,也给其他初学者一些参考,学习过程中使用到的软件为Cadence IC617运行在CentOS7系统下,参考的书籍为Razavi的《模拟CMOS集成电路设计》。

为了后续各种电路的分析与计算,我们需要知道自己使用的工艺库基础MOS器件的相关参数,如

V

T

H

V_{TH}

VTH、

μ

C

o

x

\mu C_{ox}

μCox、

λ

\lambda

λ等,本篇记录了如何通过在IC617中仿真并计算获取这些参数,工艺库使用的是TSMC 65nm工艺库。

一、NMOS参数仿真

(1)绘制原理图

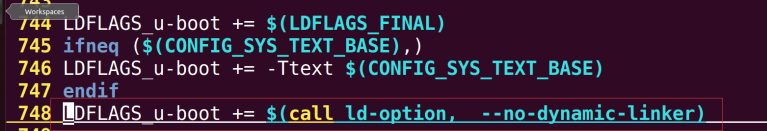

在我的第一篇学习记录中有提到详细的原理图绘制,继续沿用上一次的工程。原理图如下,使用的NMOS,W=200nm,L=60nm:

(2)开始仿真

将vgs作为parameter扫描,范围设置为0.7-1.2V,扫描5个点,vds作为自变量,扫描范围为0-2.5V,因变量为漏端电流。

在菜单栏Marker -> Create Marker中可以设置游标。

在图中添加两组垂直的游标,交点会自动显示数据,这里为了更精确,我选择了靠近饱和区中间的两组(1.3V、1.8V)。

(3)开始计算

根据仿真测得数据,选取两组,如下表。

| - | Vds=1.3V | Vds=1.8V |

|---|---|---|

| Vgs=1.2V | 123.139 μ \mu μA | 133.626 μ \mu μA |

| Vgs=0.95V | 72.081 μ \mu μA | 80.440 μ \mu μA |

NMOS特性方程(考虑沟道调制效应)如下:

I

D

=

1

2

μ

n

C

o

x

W

L

(

V

G

S

−

V

T

H

)

2

(

1

+

λ

V

D

S

)

I_D=\frac{1}{2}\mu _nC_{ox}\frac{W}{L}\left ( V_{GS}-V_{TH} \right ) ^{2}\left ( 1+\lambda V_{DS} \right )

ID=21μnCoxLW(VGS−VTH)2(1+λVDS)

先将第一行数据代入,如下:

123.139

μ

A

=

1

2

μ

n

C

o

x

W

L

(

1.2

−

V

T

H

)

2

(

1

+

1.3

λ

)

123.139\mu A=\frac{1}{2}\mu _nC_{ox}\frac{W}{L}\left ( 1.2-V_{TH} \right ) ^{2}\left ( 1+1.3\lambda \right )

123.139μA=21μnCoxLW(1.2−VTH)2(1+1.3λ)

133.626

μ

A

=

1

2

μ

n

C

o

x

W

L

(

1.2

−

V

T

H

)

2

(

1

+

1.8

λ

)

133.626\mu A=\frac{1}{2}\mu _nC_{ox}\frac{W}{L}\left ( 1.2-V_{TH} \right ) ^{2}\left ( 1+1.8\lambda \right )

133.626μA=21μnCoxLW(1.2−VTH)2(1+1.8λ)

上下两式相比,得

λ

=

0.21

\lambda =0.21

λ=0.21.

再将第一列数据代入,如下:

123.139

μ

A

=

1

2

μ

n

C

o

x

W

L

(

1.2

−

V

T

H

)

2

(

1

+

1.3

λ

)

123.139\mu A=\frac{1}{2}\mu _nC_{ox}\frac{W}{L}\left ( 1.2-V_{TH} \right ) ^{2}\left ( 1+1.3\lambda \right )

123.139μA=21μnCoxLW(1.2−VTH)2(1+1.3λ)

72.081

μ

A

=

1

2

μ

n

C

o

x

W

L

(

0.95

−

V

T

H

)

2

(

1

+

1.3

λ

)

72.081\mu A=\frac{1}{2}\mu _nC_{ox}\frac{W}{L}\left ( 0.95-V_{TH} \right ) ^{2}\left ( 1+1.3\lambda \right )

72.081μA=21μnCoxLW(0.95−VTH)2(1+1.3λ)

上下两式相比,得

V

T

H

=

0.136

V

V_{TH} =0.136V

VTH=0.136V.

最后将计算得出的

λ

、

V

T

H

\lambda 、V_{TH}

λ、VTH 代入任意一个式子,解出

K

n

=

μ

n

C

o

x

=

51.27

μ

A

/

V

2

K_n = \mu _nC_{ox} =51.27\mu A/V^2

Kn=μnCox=51.27μA/V2

二、PMOS参数仿真

(1)绘制原理图

和NMOS差不多,源端接最高电压3V,原理图如下:

(2)开始仿真

由于PMOS和NMOS相反,所以vg要从大往小仿真,vg仿真范围我设置的是1.8V-2.2V,vd设置的是1V-3V,输出信号是D端电压和电流。

marker尽量选择靠近饱和区中间的,我选的1.5V、2.0V.

(3)开始计算

根据仿真测得数据,选取两组,注意这里:在原理图中我设置的是Vg和Vd,在这要换算成Vsg和Vsd方便计算,如下表。

| - | Vsd=1.5V | Vsd=1V |

|---|---|---|

| Vsg=1.2V | -77.966 μ \mu μA | -67.051 μ \mu μA |

| Vsg=1V | -51.315 μ \mu μA | -43.066 μ \mu μA |

PMOS特性方程(考虑沟道调制效应)如下:

I

D

=

−

1

2

μ

p

C

o

x

W

L

(

∣

V

G

S

∣

−

∣

V

T

H

∣

)

2

(

1

+

λ

∣

V

D

S

∣

)

I_D=-\frac{1}{2}\mu _pC_{ox}\frac{W}{L}\left ( |V_{GS}|-|V_{TH}| \right ) ^{2}\left ( 1+\lambda |V_{DS}| \right )

ID=−21μpCoxLW(∣VGS∣−∣VTH∣)2(1+λ∣VDS∣)

先将第一行数据代入,如下:

77.966

μ

A

=

1

2

μ

p

C

o

x

W

L

(

1.2

−

∣

V

T

H

∣

)

2

(

1

+

1.5

λ

)

77.966\mu A=\frac{1}{2}\mu _pC_{ox}\frac{W}{L}\left ( 1.2-|V_{TH}| \right ) ^{2}\left ( 1+1.5\lambda \right )

77.966μA=21μpCoxLW(1.2−∣VTH∣)2(1+1.5λ)

67.051

μ

A

=

1

2

μ

p

C

o

x

W

L

(

1.2

−

∣

V

T

H

∣

)

2

(

1

+

λ

)

67.051\mu A=\frac{1}{2}\mu _pC_{ox}\frac{W}{L}\left ( 1.2-|V_{TH}| \right ) ^{2}\left ( 1+\lambda \right )

67.051μA=21μpCoxLW(1.2−∣VTH∣)2(1+λ)

上下两式相比,得

λ

=

0.48

\lambda =0.48

λ=0.48.

再将第一列数据代入,如下:

77.966

μ

A

=

1

2

μ

p

C

o

x

W

L

(

1.2

−

∣

V

T

H

∣

)

2

(

1

+

1.5

λ

)

77.966\mu A=\frac{1}{2}\mu _pC_{ox}\frac{W}{L}\left ( 1.2-|V_{TH}| \right ) ^{2}\left ( 1+1.5\lambda \right )

77.966μA=21μpCoxLW(1.2−∣VTH∣)2(1+1.5λ)

51.315

μ

A

=

1

2

μ

p

C

o

x

W

L

(

1

−

∣

V

T

H

∣

)

2

(

1

+

1.5

λ

)

51.315\mu A=\frac{1}{2}\mu _pC_{ox}\frac{W}{L}\left ( 1-|V_{TH}| \right ) ^{2}\left ( 1+1.5\lambda \right )

51.315μA=21μpCoxLW(1−∣VTH∣)2(1+1.5λ)

上下两式相比,得

V

T

H

=

0.140

V

V_{TH} =0.140V

VTH=0.140V.

最后将计算得出的

λ

、

V

T

H

\lambda 、V_{TH}

λ、VTH 代入任意一个式子,解出

K

p

=

μ

p

C

o

x

=

24.20

μ

A

/

V

2

K_p = \mu _pC_{ox} =24.20\mu A/V^2

Kp=μpCox=24.20μA/V2

小结

至此,工艺库MOS的参数仿真就结束了,很多设计规则下,会给定W、L不变,这样就能保证所有设计下的MOS的特征参数一样了。

下表是最终计算的综合结果,若上面的计算方法有错误,恳请各位大佬指出!

| - | V T H V_{TH} VTH | λ \lambda λ | K K K |

|---|---|---|---|

| NMOS | 0.136V | 0.21 | 51.27 μ A / V 2 \mu A/V^2 μA/V2 |

| PMOS | 0.140V | 0.48 | 24.20 μ A / V 2 \mu A/V^2 μA/V2 |

补:实际上这些参数可以在软件中看到,与实际计算有蛮大的差距,我暂时也不知道是为什么,希望有大佬能帮忙解答。。。

可以看到很多信息,例如vth=0.504V,region=2

region是管子工作区间,0代表截止区,1代表线性区,2代表饱和区,3代表亚阈值区。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)