常见的接口汇总

目录

1. 串口

1.1 串口概述

串行接口简称串口,也叫串行通信接口,一般也叫COM口,这是一个统称。采用串行通信的接口都叫作串口,串口是一个硬件接口。

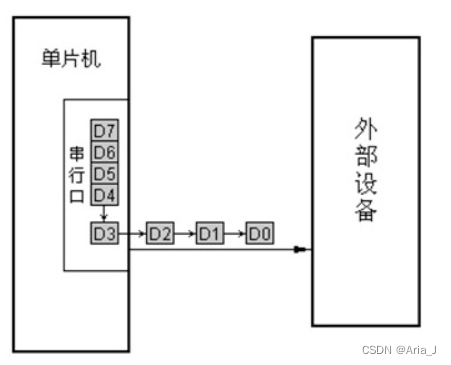

1.2 串行和并行

串行:计算机总线或其他数据通道上,每次传输一个元数据,并连续进行以上单次过程的通信方式。

并行:在并行端口上通过一次同时传输若干位元数据的方式进行通信,所以并行的速度比串行快。

2. UART

2.1 UART概述

UART是Universal Asynchronous Receiver/Transmitter的简称,也就是通用异步收发传输器。UART可以连接TTL电平也可以连接RS-232,UART接TTL电平就是普通的串口,+5V等价于逻辑"1",0V等价于逻辑"0";而UART如果接了RS232/RS485的转换芯片,那么后面的总线上就是按照RS232/RS485规则来传输数据。UART是一种串行、异步、全双工的通信协议,工作原理是将传输数据的每个二进制位串行传输。在UART通信协议中信号线上的状态为高电平时代表“1”,信号线上的状态为低电平时代表“0”。

2.2 UART数据格式

一个字符为10位(1个起始位,7个数据位,1个校验位,1个结束位),数据通信格式为下图。

空闲位:

UART协议规定,当总线处于空闲状态时信号线的状态位'1'即高电平,表示当前线路上没有数据传输。

起始位:

每开始一次通信时发送方先发出一个逻辑'0'的信号(低电平),表示传输字符的开始。因为总线空闲时为高电平所以开始一次通信时先发送一个明显区别于空闲状态的信号即低电平。

数据位:

起始位之后就是我们要传输的数据,数据位可以是5、6、7、8、9位等,构成一个字符(一般是7位),如ASCII码(7位),扩展BCD码(8位)。先发送最低位,最后发送最高位。

奇偶校验位:

数据位加上这一位(奇偶校验位)后,使得'1'的位数应为偶数(偶校验)或奇数(奇校验),以此来校验数据传送的正确性。校验位其实是调整个数,

- 奇校验(odd parity):如果数据位中“1”的数目是偶数,则校验位为“1”,如果“1”的数目是奇数,校验位为“0”。

- 偶校验(even parity):如果数据为中“1”的数目是偶数,则校验位为“0”,如果为奇数,校验位为“1”。

停止位:

它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。由于数据是在传输线上定时的,并且每一个设备有其自己的时钟,很可能在通信中的两台设备之间出现了不同步。因此停止位不仅仅是表示传输的结束,并且提供计算机校正时钟的机会。停止

位个数越多,数据传输越稳定,但是数据传输速度也越慢。

3. TTL电平

3.1 TTL电平概述

TTL是Transistor-Transistor Logic的简写,是一种电平逻辑,晶体管-晶体管逻辑。

3.2 标准TTL电平逻辑

逻辑1:高电平,VCC(3.3V/5V)

逻辑0:低电平,GND(0V)

对TTL电平的器件来说,当输入电压高于2V时,才会被识别为逻辑1,输入的低电平低于1.2V时,才会被识别为0。输出高电平,输出低电平

,输入高电平

,输入低电平

。

3.3 USB转TTL

玩过51单片机的小伙伴应该都用过CH340G模块,用来下载HEX文件,这个模块的作用就是将USB转成TTL电平。一般单片机的电平都是TTL电平,模块的内部芯片是CH340T,图(USB转TTL模块)

使用CH340T芯片,USB转TTL电平的电路原理图。

注意:CH340G和CH340T都是USB转TTL电平的芯片,只是封装不同,管脚不同。

3.4 TTL与单片机连接

TTL电平的器件之间通信,只需要三根信号线:TXD、RXD和GND,和单片机接法很简单,3.3V的单片机就接3.3V,5V的单片机就接5V,如果单片机有单独的供电,3.3V和5V都不接。

4. USB

USB是Universal Serial Bus(通用串行总线)的缩写,是一个外部总线标准,用于规范电脑和外部设备的连接和通讯,是应用在PC领域的接口技术,特点是传输速度快,支持热插拔,可连接多个设备。常见的USB接口有:

其中最常见的Type-A的USB的接口定义为

5. RS-232

5.1 RS-232概述及电平逻辑

RS232不同于TTL的电平逻辑,为负逻辑。负12V代表高电平逻辑1,正12V代表低电平逻辑0,电压也有标准范围。

高电平:逻辑1,-15V到-3V;

低电平:逻辑0,+3V到+15V

5.2 DB9接口定义

RS232串口线最常见的就是DB9针,一般用到最多的是RXD、TXD、GND三个信号。下面是RS232串口引脚的定义:

| 母头引脚 | 引脚作用+名称 | 公头引脚 | 引脚作用+名称 | ||

| 1 | 数据载波检测 | DCD | 1 | 数据载波检测 | DCD |

| 2 | 数据发送 | TXD | 2 | 数据接收 | RXD |

| 3 | 数据接收 | RXD | 3 | 数据发送 | TXD |

| 4 | 数据设备准备 | DSR | 4 | 数据终端准备 | DTR |

| 5 | 地 | GND | 5 | 地 | GND |

| 6 | 数据终端准备 | DTR | 6 | 数据设备准备 | DSR |

| 7 | 清除发送 | CTS | 7 | 请求发送 | RTS |

| 8 | 请求发送 | RTS | 8 | 清除发送 | CTS |

| 9 | 振铃指示 | RI | 9 | 振铃指示 | RI |

5.3 USB转RS-232

USB转RS-232可以先将USB转换为TTL,再将TTL转换为RS232。目前有很多USB直接转RS232的线材,线材内部集成转换电路。常用的USB转RS-232用的两个芯片是FT232和SP213。

5.4 TTL和RS-232互转

单片机接口一般是TTL电平,如果接232电平的外设,就需要加TTL转RS-232的模块,转换方向是双向的。

TTL和RS-232电平互相转换最常用的芯片是MAX232和SP232。

6. RS-485

6.1 RS-485 概述

RS-485和RS232一样,都是串行通信标准,现在的标准名称是TIA/EIA-485-A。RS-485弥补了RS-232通信距离短,速率低的缺点。RS-485的速率可达10Mbit/s,理论通信距离可达1200m。

6.2 RS-485电平逻辑

RS-485是差分传输,如果用单片机控制RS-485接口的设备,需要用到收发器,这一点和CAN总线类似,实例如下图。

一般收发器内部是一个发送器加一个接收器组成。收发器典型的功能框图如下,其中使能信号字母上面加一横是低电平有效,不加的是高电平有效。

其中,A和B是总线;R是接收器的输出;RE是接收器的使能信号;DE是发送器的使能信号;D是发送器的输入。

对于发送器,当发送器使能引脚DE为逻辑高时,差分输出A和B遵循数据输入D处的逻辑状态。D处的逻辑高导致A转为高,B转为低。在这种情况下,定义为的差分输出电压为正。当D为低时,输出状态反转,B变高,A变低,

为负。当DE为低时,两个输出都变成高阻抗,在这种情况下,与D处的逻辑状态是不相关的。

发送器真值表

| input | enable | output | output | description |

| D | DE | A | B | |

| H | H | H | L | Actively drive bus high |

| L | H | L | H | Actively drive bus low |

| X | L | Z | Z | Drive disabled |

| X | OPEN | Z | Z | Driver disabled by default |

| OPEN | H | H | L | Actively drive bus high by default |

对于接收器,当接收器使能引脚RE逻辑低时,接收器使能。当定义为的差分输入电压为正且高于正输入阈值

时,接收器输出R变高。当

为负且低于负输入阈值

,接收器输出R变低。如果VID在VIT+和VIT-之间,则输出不确定。当RE为逻辑高或悬空时,接收器输出为高阻抗,VID的大小和极性无关。

| Differential input | enable | output | description |

| VID=VA-VB | RE | R | |

| VIT+<VID | L | H | Receive valid bus high |

| VIT-<VID<VIT+ | L | ? | Indeterminate bus state |

| VID<VIT- | L | L | Receive valid bus low |

| X | H | Z | Receiver disabled |

| X | OPEN | Z | Receiver disabled by default |

| Open-circuit bus | L | H | Fail-safe high output |

| Short-circuit bus | L | H | Fail-safe high output |

| Idle (terminated) bus | L | H | Fail-safe high output |

5.3 TTL和RS-485转换

TTL转成RS-485很常见,收发器芯片很多,比如MAX485,用起来也很简单,一般左接MCU的GPIO,用来控制。

5.4 RS-232和RS-485转换

RS-232和RS-485之间可以转换,一个方法是RS-232转换成TTL,再由TTL转换为RS-485,当然也有芯片支持将RS-232支持转换成RS-485,双向转换。

7. SPI

7.1 SPI概述

SPI是串口外设接口(Serial Peripheral Interface)的缩写,是一种高速的全双工的同步的通信总线,SPI的速率比IIC高,一般可以到几十Mbps,不同的器件当主机和当作从机的速率一般不同。

7.2 信号线

SPI通常有4根线(四线制),可实现全双工通信。

SCK : 串行时钟(Serial Clock)

MOSI : 主发从收信号(Master Output,Slave Input)

MISO : 主收从发信号(Master Input,Slave Output)

CS/CS : 片选信号(Slave Select)

产生时钟信号的器件称为主机,主机和从机之间传输的数据与主机产生的时钟同步。SPI接口只能有一个主机,但可以有一个或多个从机。来自主机的片选信号用于选择从机,这通常是一个低电平有效信号,拉高时从机与SPI总线断开连接,当使用多个从机时,主机需要为每个从机提供单独的片选信号。

7.3 SPI数据传输

要开始SPI通信,主机必须发送时钟信号,并通过使能CS信号选择从机。SPI是全双工接口,主机和从机可以分别通过MOSI和MISO线路同时发送数据。在SPI通信期间,数据的发送和接收同时进行。SPI接口允许用户灵活选择时钟的上升沿或下降沿来采样和/或移位数据。

7.4 时钟极性和时钟相位

在SPI中,主机可以选择时钟极性和时钟相位。在空闲状态期间,CPOL位设置时钟信号的极性。空闲状态是指传输开始时CS为高电平且在向低电平转变的期间,以及传输结束时CS为低电平且在向高电平转变的期间。CPHA位选择时钟相位。根据CPHA位的状态,使用时钟上升沿或下降沿来采样和/或移位数据。主机必须根据从机的要求选择时钟极性和时钟相位。根据CPOL和CPHA位的选择,有四种SPI模式可用:

| SPI模式 | CPOL | CPHA | 空闲状态下的时钟极性 | 用于采样和/或移位数据的时钟相位 |

| 0 | 0 | 0 | 低电平 | 数据在上升沿采样,在下降沿移出 |

| 1 | 0 | 1 | 低电平 | 数据在下降沿采样,在上升沿移出 |

| 2 | 1 | 1 | 高电平 | 数据在下降沿采样,在上升沿移出 |

| 3 | 1 | 0 | 高电平 | 数据在上升沿采样,在下降沿移出 |

下面分别介绍这四种模式中数据的传输。传输的开始和结束用绿色虚线表示,采样边沿用橙色虚线表示,移位边沿用蓝色虚线表示。请注意,这些图像仅供参考。要成功进行SPI通信,还是需要看产品数据手册并确保满足器件的时序规格。

8. IIC

8.1 IIC概述

IIC是Inter Integrated Circuit的简称,是一种串行同步半双工总线。IIC总线是一个多向控制总线,多个器件可以同时挂载到一条总线上。每个连接在总线上的设备都是通过唯一的地址和其他器件通信的,主机和从机可以可以互换。

8.2 硬件连接

IIC有两条总线:SDA(串行数据线)和SCL(串行时钟线)。两条线都是双向线路,都通过一个电流源或者上拉电阻连接到正的电源电压,当总线空闲时,这两条线路都被拉高为高电平。如图,设备的数据线都连接到SDA,时钟线都连接到SCL。

8.3 通信协议

主机和从机的概念,主机是负责整个系统的任务协调与分配,从机一般是通过接收主机的指令从而完成某些特定任务。主机和从机之间通过总线连接,进行通信。

IIC是半双工的协议,也就是指在发送数据的同时不能接收数据,在接收数据的同时不能发送数据,发送和接收数据必须在时间上分开。

8.3.1 数据的有效性

SDA线上的数据必须在时钟的高电平周期保持稳定。数据线的高或低电平状态只有在SCL线的时钟信号是低电平时才能改变。如图,IIC总线的位传输。

8.3.2 起始和停止位

在IIC总线中,总线上数据的传输必须以一个起始信号作为开始条件,以一个结束信号作为传输的停止条件。起始和结束信号总是由朱设备产生,即意味着从设备不可以主动通信,所有的通信都是从主设备发起的。主机可以发出询问的命令,然后等待从机设备通信。

起始和结束信号的产生条件:总线在空闲的状态时,SCL和SDA默认都是保持着高电平状态。

起始位:当SCL为高电平时,SDA电平状态发生由高到低的跳变,产生一个下降沿。

终止位:当SCL为高电平时,SDA由低到高的跳变,产生一个上升沿。

8.3.3 字节格式

IIC总线数据传输是以字节为单位,必须是8位。每次传输可以发送的字节数量不受限制。每个字节后必须跟一个响应位。首先传输的是数据的最高位(MSB)。如果从机要完成一些其他功能后才能接收或者发送下一个完整的数据字节,可以使时钟线SCL保持低电平迫使主机进入等待状态,当从机准备好接收下一个字节并释放时钟线SCL后,数据传输继续。如果从设备不能接收到主设备发送的数据,从设备将回传一个非应答位(非应答位:延时一段时间默认回传一个非应答信号)。也就是说从机应答主机,低电平0表示应答,高电平1表示非应答。

8.3.4 读过程

{ID_Address+REG_Address}+{ID_Address+R_REG_Data}

1. 产生start信号

2. 传送器件地址(写ID_Address),ACK。

3. 传送字地址(写REG_Address),ACK。

4. 再次产生产生start信号。

5. 再传送一次器件地址,ACK。

6. 读取一个字节的数据,读数据最后结束前无应答ACK信号。

7. 产生stop信号。

从时序图上可以看出,IIC读时序要写两次器件地址,首先传送器件地址到总线上找到器件,然后写入寄存器地址,也就是word address找到需要读取数据的地址,但并不是真正的写入数据所以叫作dummy write(假写),然后再传输一个器件地址后开始读数据。

8.3.5 写过程

ID_Address,REG_Address,W_REG_Data

1. 产生start位

2. 传送器件地址ID_Address,器件地址的最后一位为数据的传输方向位。R/W,低电平0表示主机往从机写数据(W),1表示主机从从机读数据(R)。ACK应答。

3. 传送写入器件寄存器地址,即数据要写入的位置。同样ACK。

4. 传送要写入的数据。ACK应答。

5. 产生stop信号

IIC协议在读写数据时,总要发送器件地址,这里要注意,不是主机给从机发送地址,而是主机给地址总线上发送地址,挂IIC总线上的所有从机都能收到地址。如果发过来的地址和自己的地址匹配上了,从机就会给主机一个应答,这样就建立了一个通信。IIC协议一次只能有一对设备或器件进行通信。

9. IIS

9.1 IIS概述

IIS是Inter-IC-Sounder的简写,飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。在飞利浦公司的IIS标准中,即规定了硬件接口规范,也规定了数字音频数据的格式。特点是效率高,适合传送音频。IIS是个相对来时简单的接口协议,没有地址和片选机制。(需要注意的是数字音频不能直接驱动扬声器,必须要通过DAC转换成模拟音频,才能发出声音。)

9.2 IIS硬件连接

(1)串行时钟(SCLK)

也叫位时钟(BCLK),每个脉冲对应数字音频的一位数据,以左右双通道音频为例,SCLK频率=2*采样频率*采样位数。

(2)帧时钟(LRCK)

也叫字时钟(WS),用来选择左右声道,LRCK频率=采样频率,LRCK=0,左声道,LRCK=1,右声道。

LRCK可以在串行时钟的上升沿或下降沿改变,而且左右声道不一定要对称,比数据位最高位MSB早一个时钟改变,这一个时钟周期可以存储前一帧后清空,为一下帧数据准备。

(3)数据信号(SD)

串行音频数据用二进制补码表示,最高位数据固定在LRCK变化后SCLK第二个时钟,发送端的数据有效位数和接收端的数据有效位数可以不同。

(4)串行时钟、帧时钟由主设备或外部时钟提供,从设备接收位时钟与帧时钟

(9.3)操作模式

根据SD数据相对于LRCK和SCLK的位置不同,IIS的操作模式分为三种:标准IIS模式(飞利浦规定模式)、左对齐模式(较少使用)和右对齐模式(也叫日本格式)。

(3.1)标准IIS模式

标准IIS模式是左对齐模式数据信号再延迟一个时钟位变化来的,左右通道的数据MSB都是在WS变化后第二个SCLK上升沿有效。时序如下所示:

(3.2)左对齐模式

左对齐模式的数据MSB没有相对SCLK延迟一个时钟。左对齐格式的左右声道数据的MSB在WS边沿变化后SCLK的第一个上升沿有效,时序图如下:

(3) 右对齐模式

也叫日本格式,sony格式,具体对齐方式如下图所示:

接收设备必须事先知道待传数据的字长。

注意左右对齐模式的WS时钟高电平为左声道,低电平为右声道,刚好与标准IIS相反。

SCK = 采样率(48K、44.1K、16K等) x 字长(16bit、24bit、32bit) x 2(左右两通道)

MCLK/SCK = 384 、256 等需要参考手册说明支持哪种;

IIS接口,多用在传输双声道数据的场合。

10. CAN

待完善

11. 1-WIRE

11. 1 1-WIRE概述

单总线是美国DALLAS公司推出的外围串行扩展总线技术,与SPI、IIC串行数据通信方式不同,它采用单根信号线,既传输时钟又传输数据,而且数据传输是双向的。

11.2 1-WIRE框图

这是典型的1-WIRE框图,可以看到微处理器和1-WIRE器件之间只有一根线。

当MCU发送逻辑1时,经过反相器,总线呈现逻辑0,逻辑0经过1-WIRE器件的反相器,即会收到逻辑1;

当MCU发送逻辑0时,经过反相器,总线呈现逻辑1,逻辑1经过1-WIRE器件的反相器,即会收到逻辑0;

同理,当1-WIRE器件发送逻辑1时,Tx处有NMOS会导通,总线呈现逻辑0,经过MCU Rx处的反相器,MCU会收到逻辑1;

发送逻辑0时,NMOS截止,总线呈现逻辑1,MCU会收到逻辑0。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)