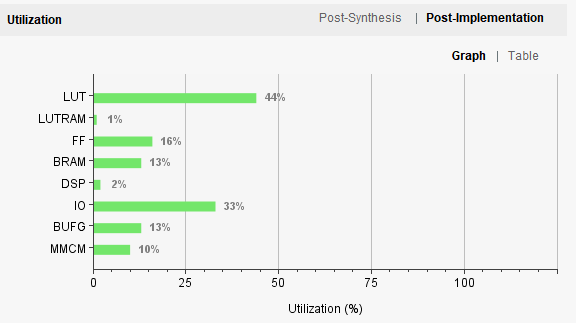

vivado里的LUT、LUTRAM、FF、BRAM、DSP、IO、BUFG、MMCM资源介绍

vivado里的LUT、LUTRAM、FF、BRAM、DSP、IO、BUFG、MMCM资源介绍

提示:以下是本篇文章正文内容,写文章实属不易,希望能帮助到各位,转载请附上链接。

vivado实现电路用到的资源类型

LUT(Look-Up Table):查找表,它接收一组输入信号,并根据预先定义的逻辑函数表(Look-Up Table)输出结果,LUT 可以实现任意逻辑函数,如与、或、非、异或等。

LUTRAM(Look-Up Table Random Access Memory):查找表RAM,LUTRAM 是一种特殊类型的 LUT,它具有额外的可编程存储器功能。这意味着 LUTRAM 可以用于实现具有存储器功能的逻辑功能,例如存储器或 RAM。

FF(Flip-Flop):触发器, 在 FPGA 中用于存储和延时信号。FF 可以将输入信号锁存到其内部,并在时钟上升沿或下降沿触发时更新输出。FF 通常用于存储状态和实现时序逻辑,在时序电路设计中起到关键作用。常见的 FF 类型有 D 触发器、JK 触发器等。

BRAM(Block RAM):块RAM,BRAM 是 FPGA 中的块随机存取存储器单元,用于实现大容量的存储器功能,通常用于存储器、缓冲区等应用。

DSP(Digital Signal Processor):数字信号处理器,DSP 单元是 FPGA 中专门用于高性能数字信号处理的特定硬件单元。它们通常包括乘法器、累加器和其他数字信号处理相关的功能。

IO(Input/Output):输入/输出,IO 单元代表 FPGA 芯片上的输入/输出资源,用于连接外部信号和设备。

BUFG(Global Buffer):全局时钟缓冲器,BUFG 是用于将时钟信号传输到 FPGA 中各个区域的全局时钟缓冲单元。

MMCM(Mixed-Mode Clock Manager):多模式时钟管理器,MMCM 是一种用于时钟生成和管理的特殊硬件资源,可以为 FPGA 中的各种逻辑提供稳定的时钟信号。

IBUF(Input Buffer):输入缓冲器,IBUF 用于将外部输入信号引入 FPGA 芯片。它的作用是将输入信号进行缓冲、放大和对齐,以适应 FPGA 内部的逻辑电平要求。IBUF 可以确保输入信号的稳定性,并使其在 FPGA 内部可靠地使用。

OBUF(Output Buffer):输出缓冲器,OBUF 用于将 FPGA 内部的输出信号传送到外部设备或其他电路。它的作用是将 FPGA 内部逻辑产生的信号进行缓冲和驱动,以适应外部设备的输入要求。OBUF 可以提供足够的电流和电压波形来驱动外部负载。

reg 介绍

-

C:时钟端口。当C端口的上升沿到来时,reg内部的状态会根据D端口的值更新。 -

CE:使能端口。只有在CE为高电平时,reg才会响应C端口上升沿时的输入数据。当CE端口为低电平时,reg会保持原来的值不变。 -

CLR:清零端口。当CLR端口为高电平时,reg置为 0。当CLR为低电平时,reg保持原来的值不变。 -

D:数据端口。D端口的值会在C端口上升沿到来时被存储到reg中。 -

Q:输出端口。Q端口用于输出reg中存储的值。

简单电路分析

该电路实现的简单的与功能,将四个输入两两相与输出。

仔细分析该电路,有以下注意的点:

1、为什么复位信号rst-n后面还接了一个LUT1?

这是因为复位信号低电平有效时,通过LUT1取反变为高电平再输入给CLR,就能清零。

2、为什么中间4个寄存器CE信号一直为高,而输出端口的寄存器CE信号却接的复位信号?

对于输出端口的寄存器(register),使能信号(CE)通常来自于复位信号(CLR)是为了确保在系统复位时,输出信号处于一种可控的状态。

当复位信号触发时,使能信号被设置为低电平,这将导致输出端口的寄存器被禁用。这样做的目的是确保在系统复位期间,输出值不会产生任何无效或不确定的结果。当复位完成后,使能信号被设置为高电平,使得输出端口的寄存器可以正常工作,并且根据输入数据进行更新。

通过使用复位信号来控制输出端口的使能信号,可以确保输出信号在系统启动和复位过程中保持可控和可预测的状态。这对于确保系统在重新启动或复位后正常运行非常重要。

需要注意的是,这只是一种常见的设计实践,具体的设计可能因应用而异。在某些情况下,可能会使用其他信号或条件来控制输出端口的使能信号。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)