Quartus II的基本使用及仿真

如何利用QuartusII建立工程并进行基本的仿真操作

一键AI生成摘要,助你高效阅读

问答

·

1.概述

本文描述的是如何利用QuartusII建立工程并进行基本的仿真操作。

2.建立工程及添加Vreilog文件

2.1 建立工程

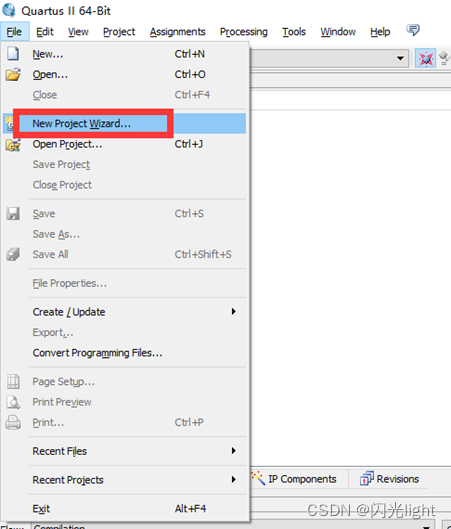

1.打开Quartus II,File>>New proje Wizard…

2. 设置工程路径和工程名。

3.是否要添加verilog文件?否的话直接点击next。

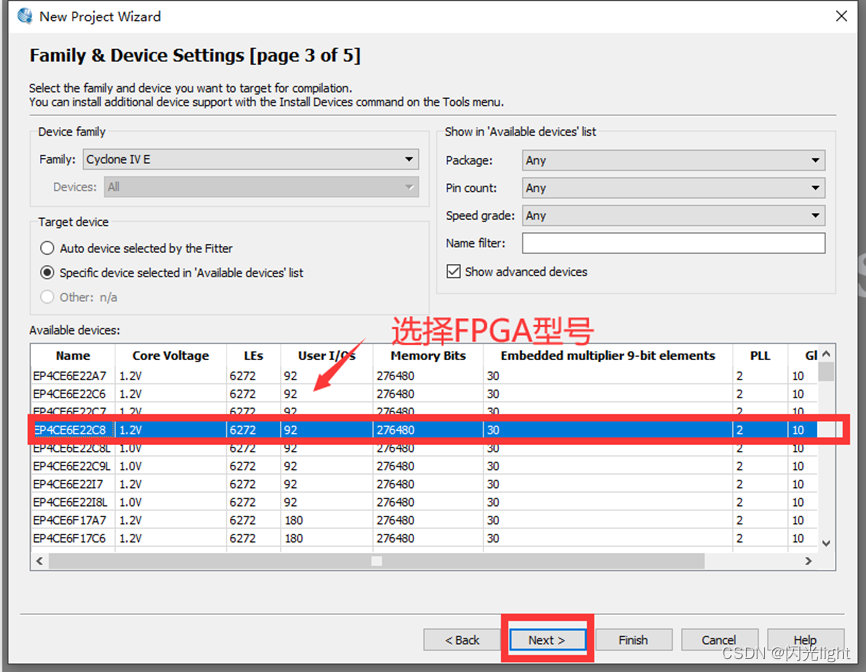

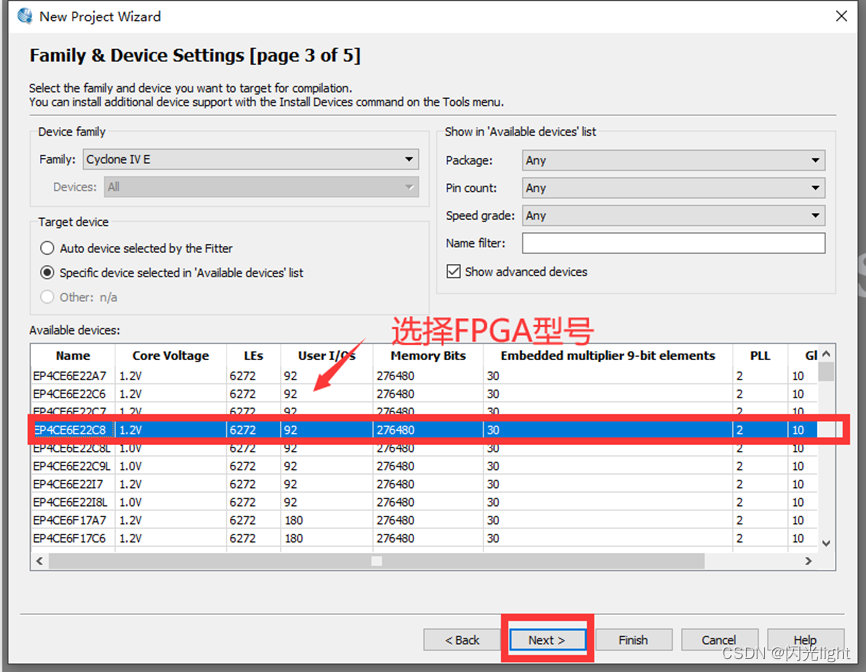

4.选择FPGA型号>>NEXT。

5.选择仿真工具和仿真语言,有的是Modelsim-Altera,有的是Modelsim,这个要视情况选择。

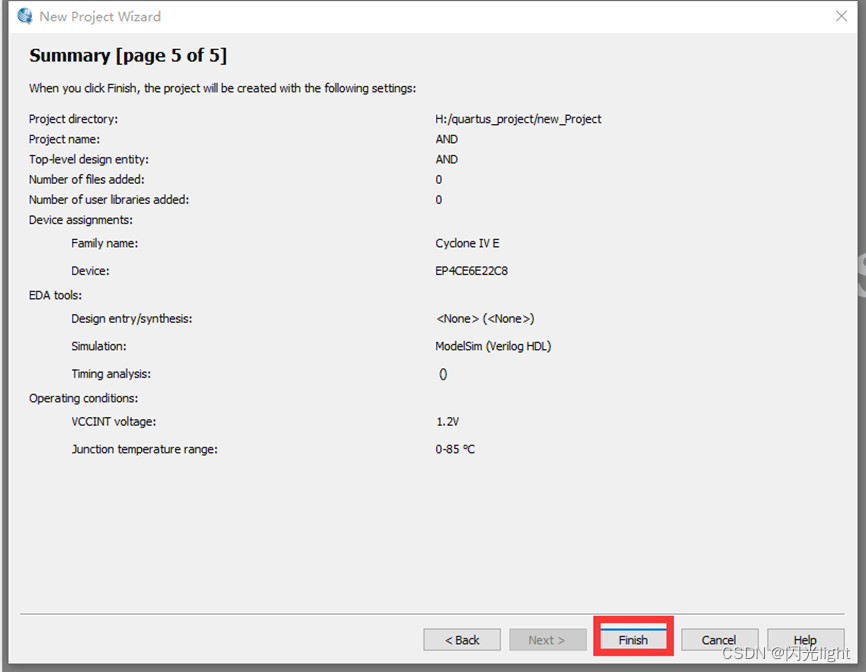

6.Finish。

2.2 添加和编写Verilog。

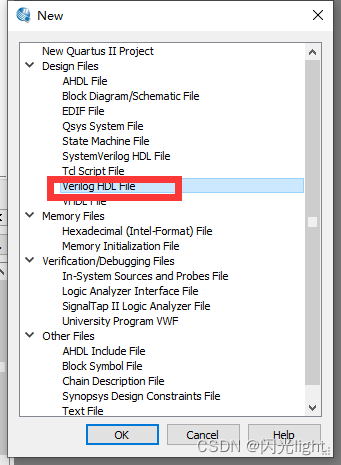

1. File>>New>>Verilog HDL>>OK;

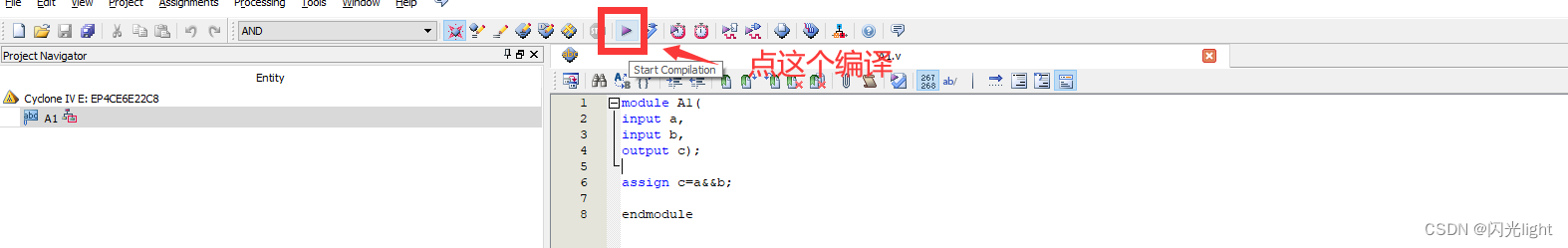

2. 编写代码。

3. 编译。

4. 保存,注意模块名和文件名相同。

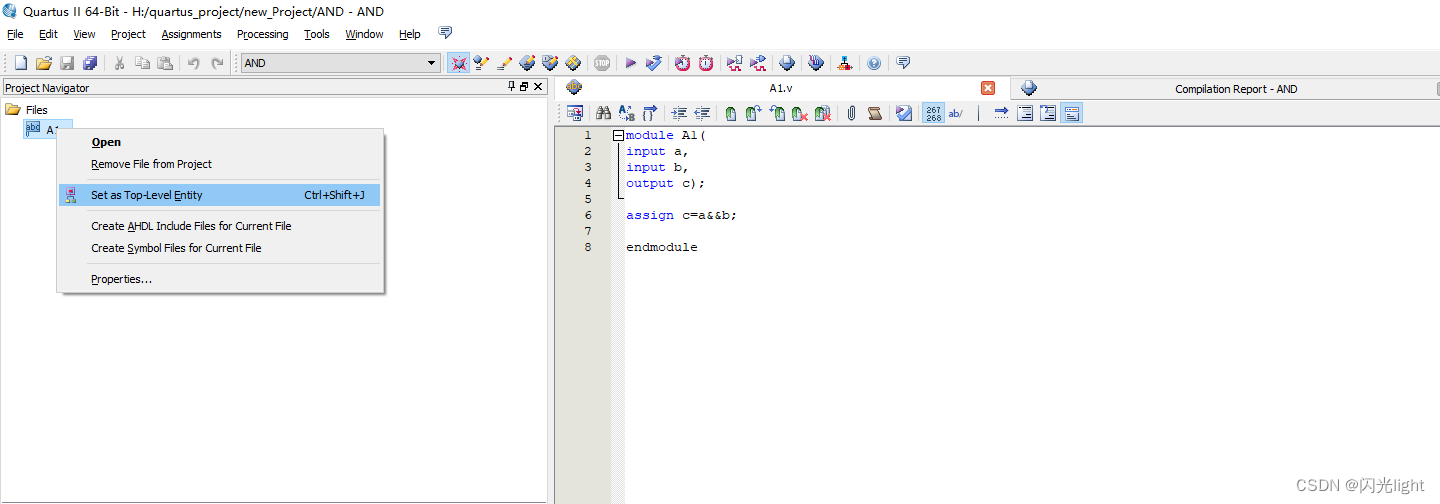

5. 设置顶层模块:右键点击你要设置为顶层模块的verilog文件,Set as Top-Level Entity即可将其设置为顶层模块。

3.仿真

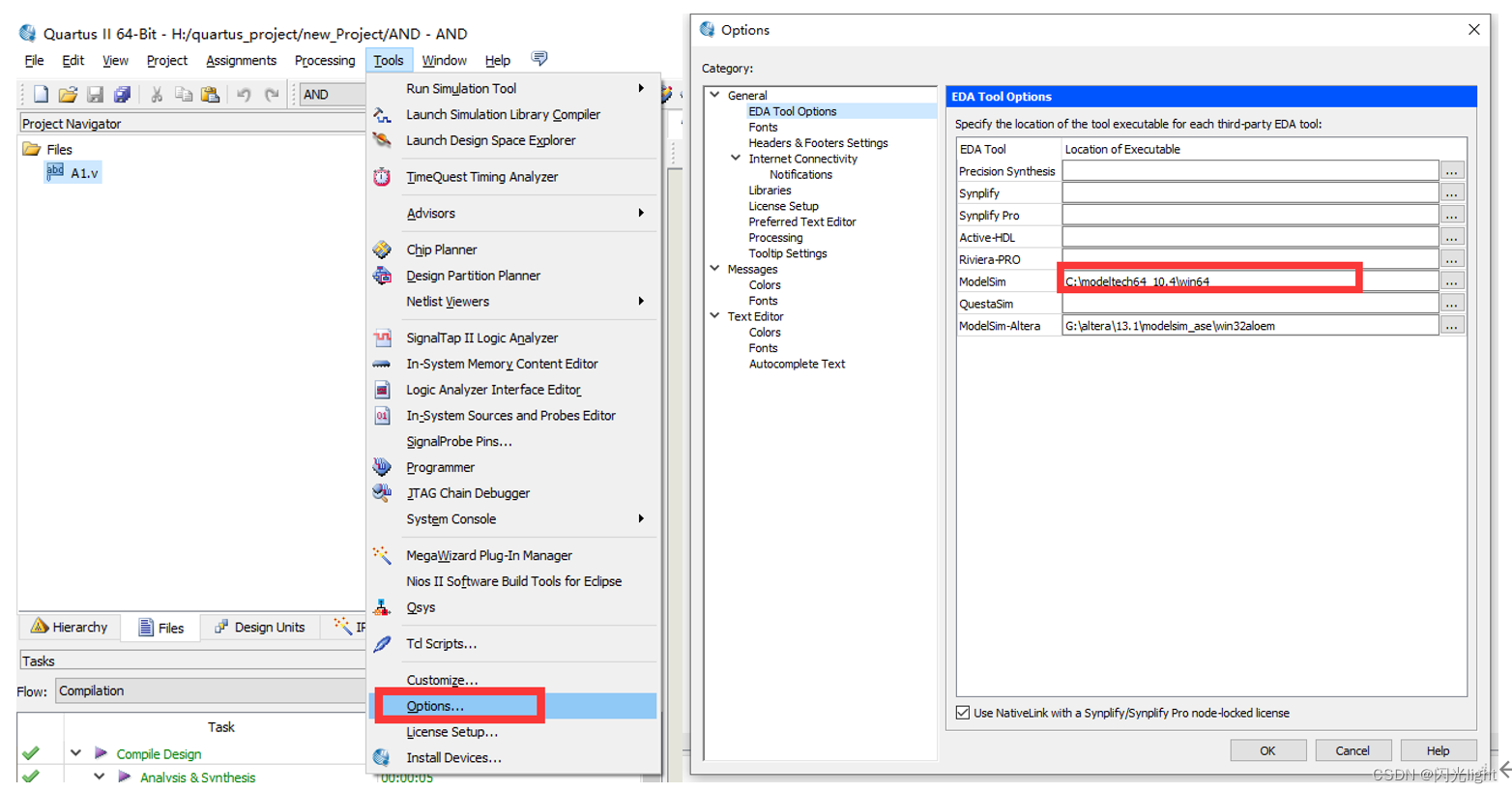

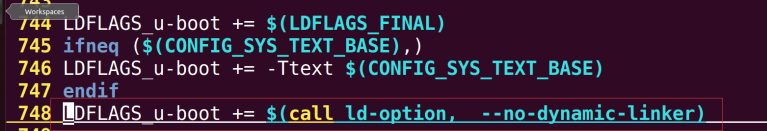

1.第⼀次⽤modelsim+quartus的时候需要在quartus中设置modelsim的路径,quartus->tools->Options…>EDA tool options ,在右边选择modelsim的安装路径,如下图:

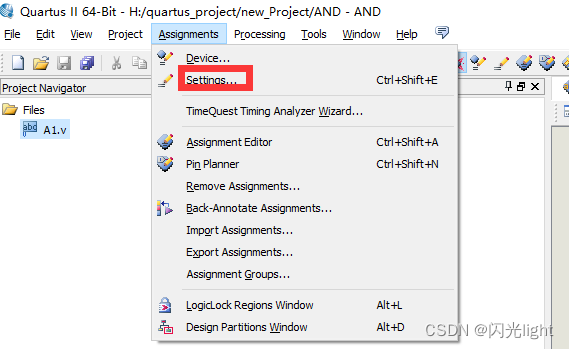

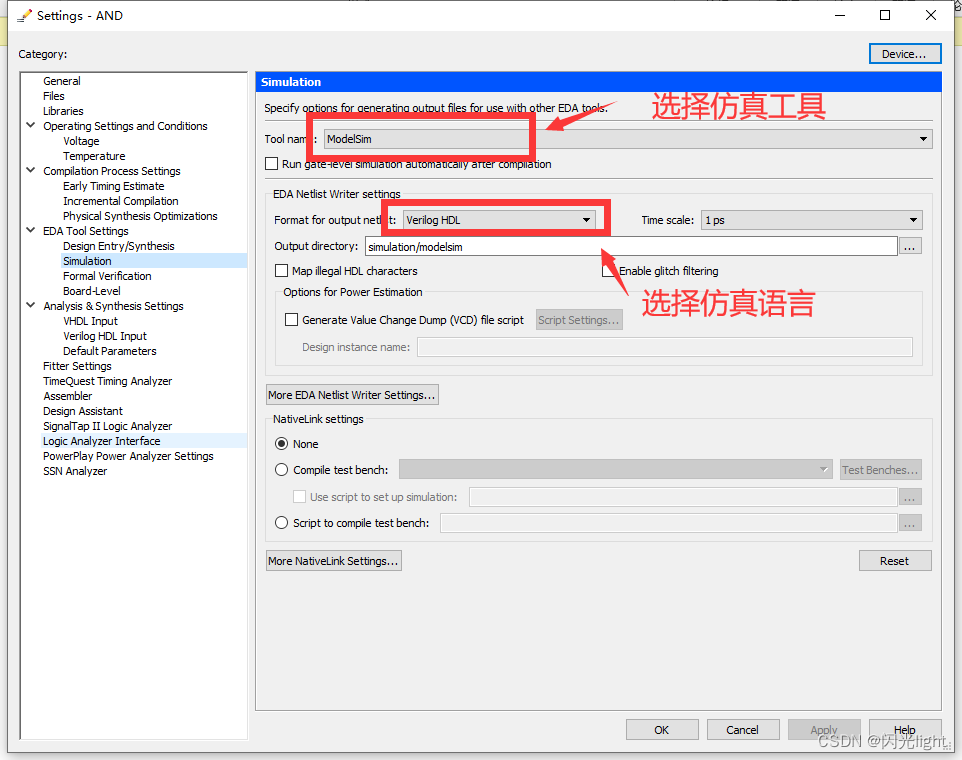

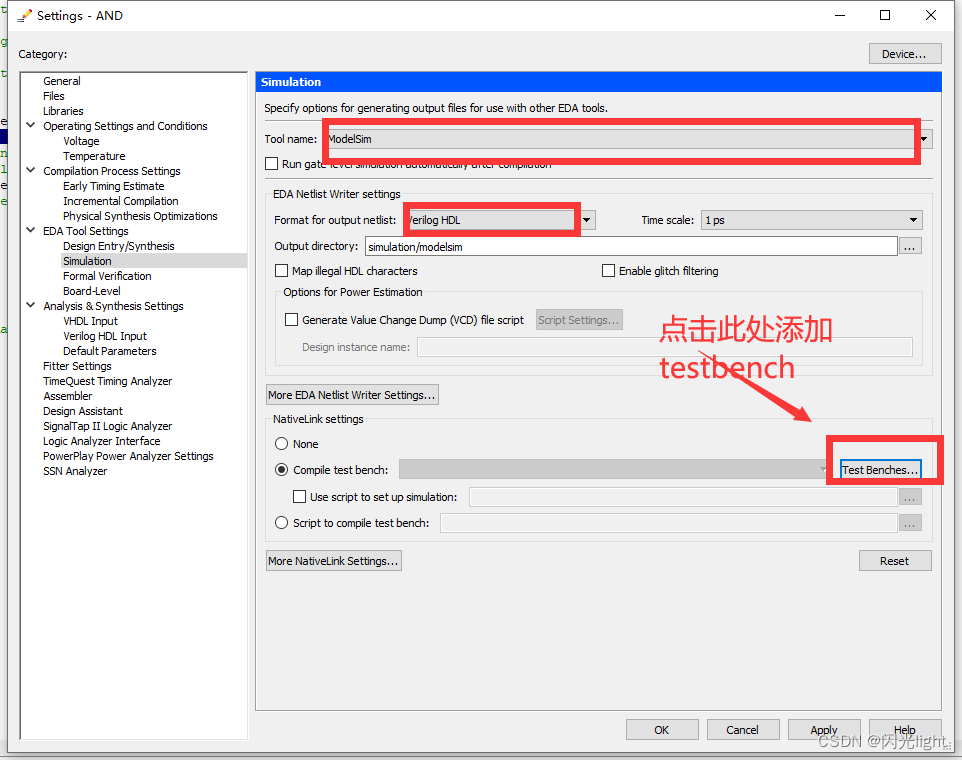

2.然后选择仿真工具和仿真语言,Assignments>>Settings>>Simulation:

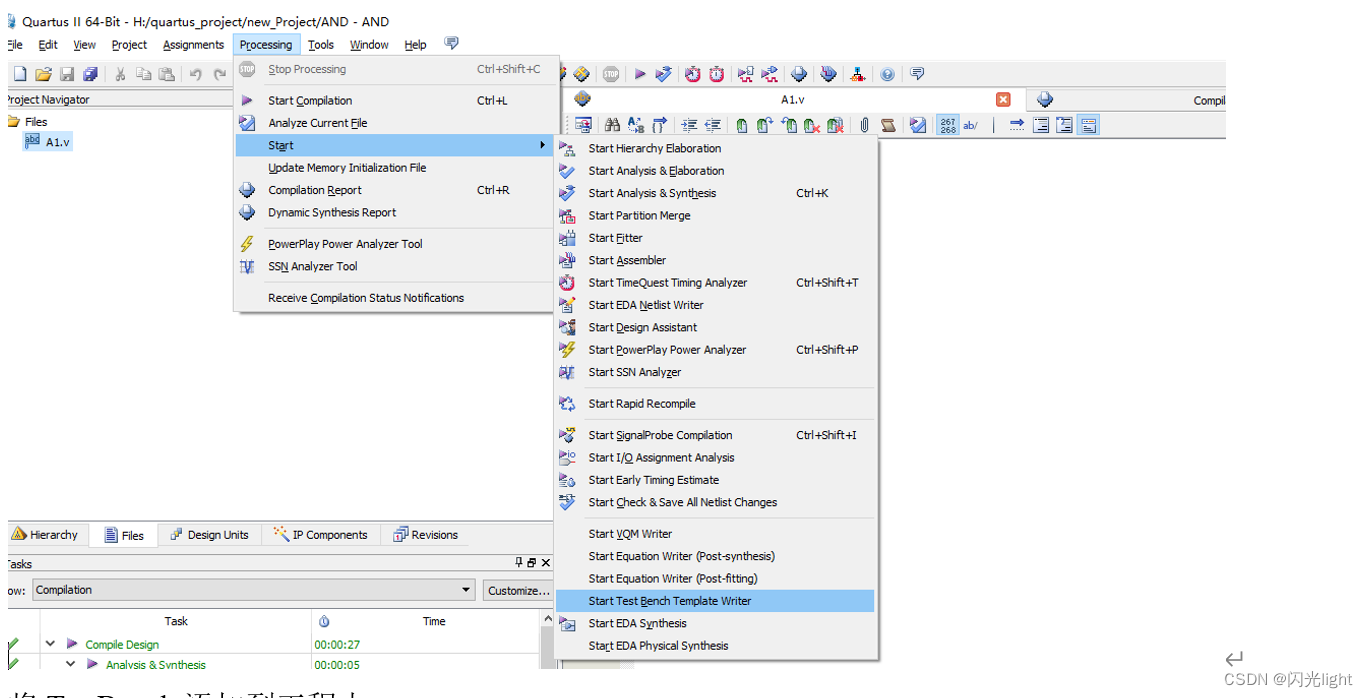

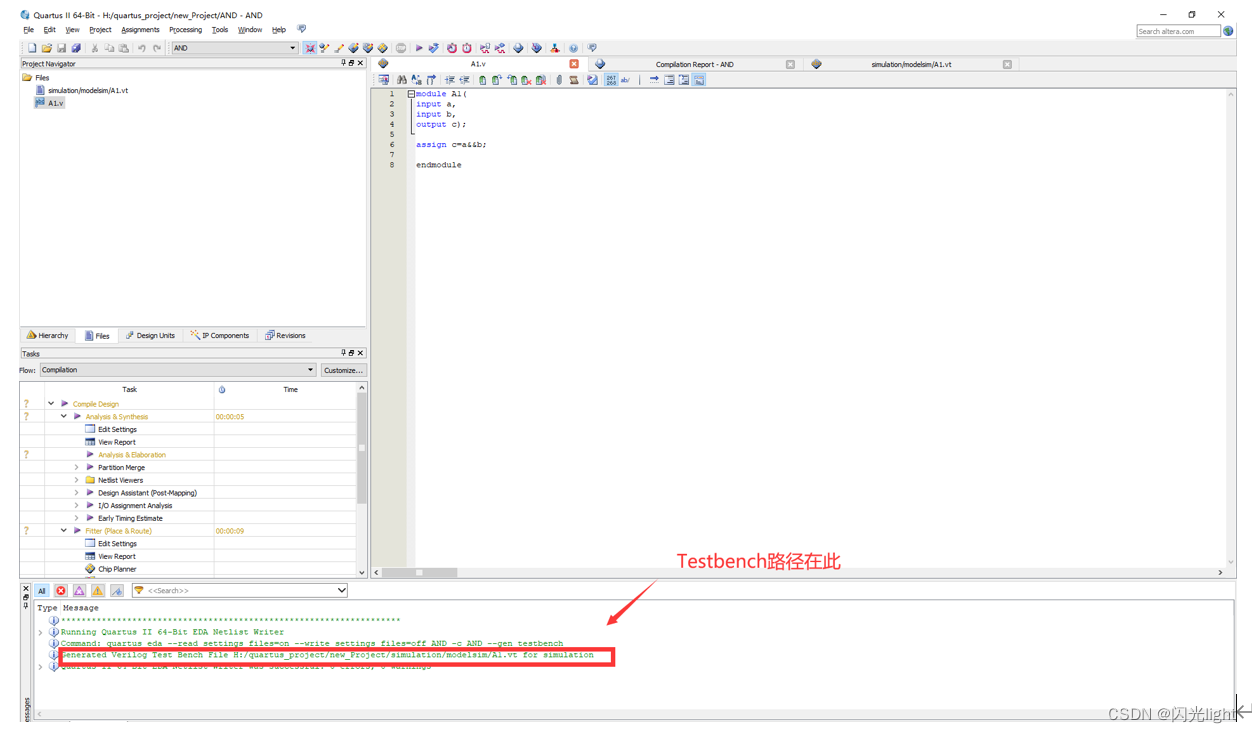

3.生成Testbench模板:点击Start Test Bench Template Writer即可自动生成Testbench。

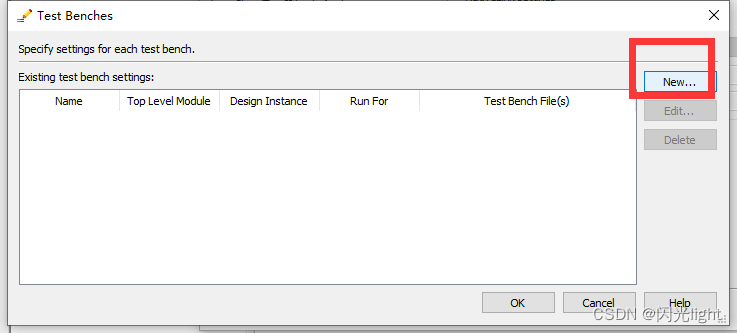

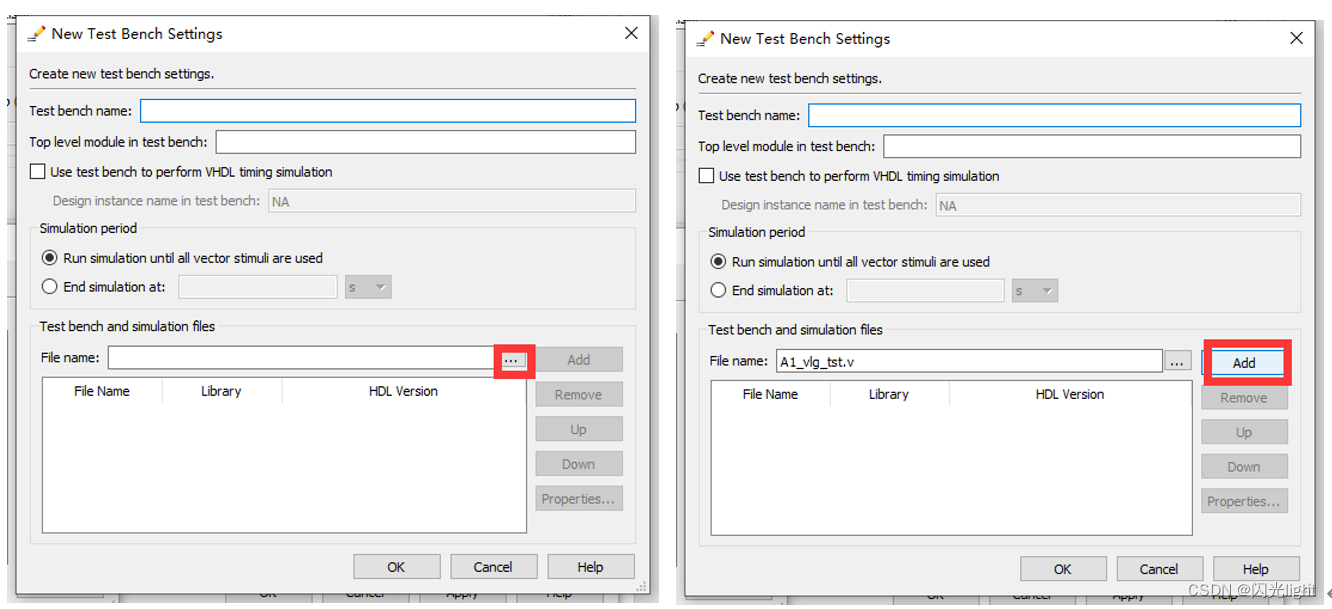

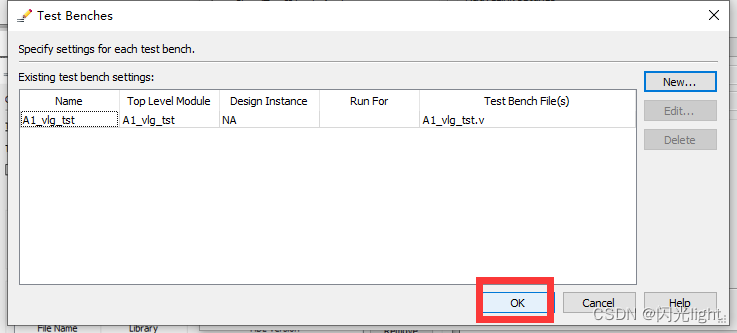

4.将TestBench添加到工程中:

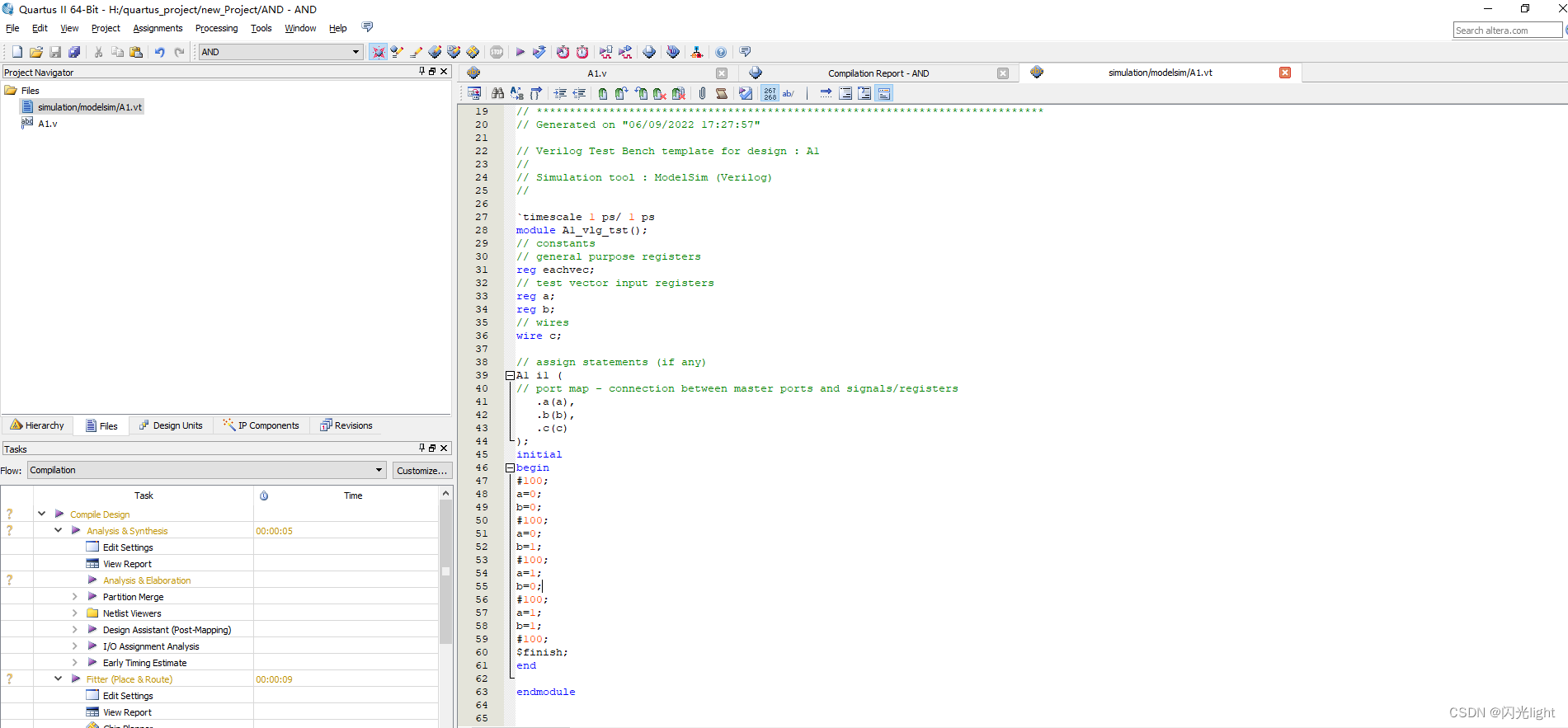

5.打开testbench文件,编写testbench;编写完后保存,记得模块名要和文件名一致。

6.点击Assignment -> Settings,添加编写完的testbench:

7.仿真

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)