芯片测试原理(基础篇)

芯片测试原理

一、测试目的

对待测芯片进行测试,以判断芯片在设计规格书所规定应用环境在,能可正常工作并实现预期的各种功能及性能指标

二、测试分类

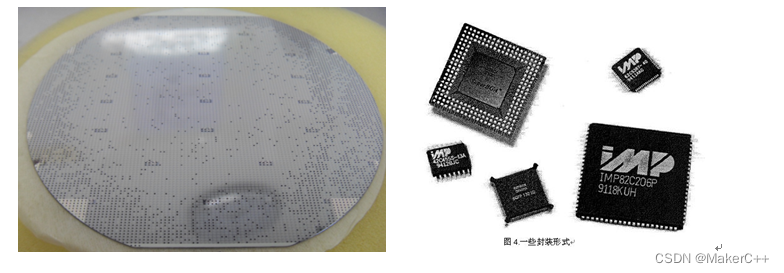

按制造阶段测试可分为圆片测试和成品测试

圆片测试:也叫CP(Circuit probing)测试,是对圆片上的IC进行测测试,此时芯片是裸露的

成品测试:也叫FT(Final test)测试,是对已封装的IC进行测试,此时芯片是封装的

下图左为已测圆片,下图右为成品IC

三、直流参数测试

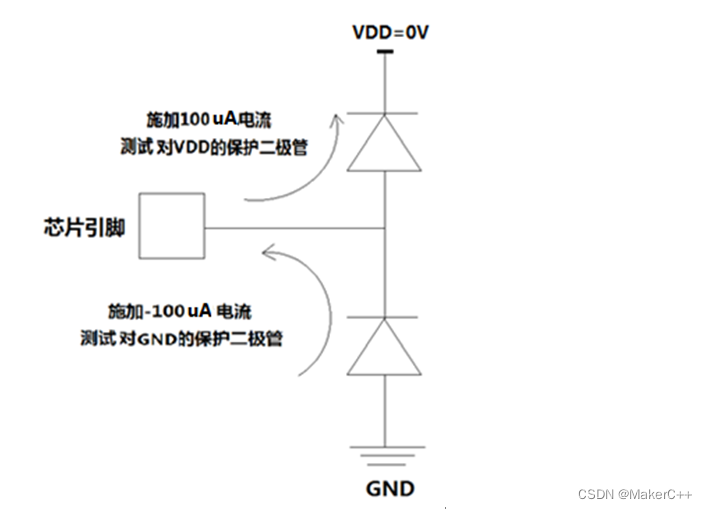

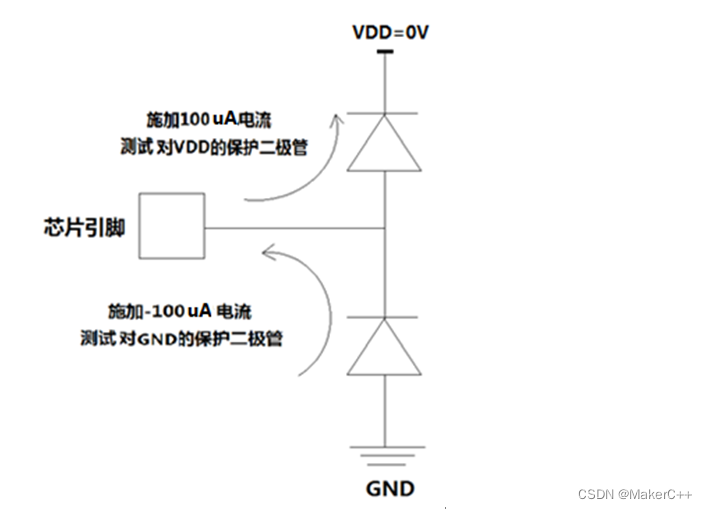

1、OPEN/SHORT测试:也称为Continuity Test或Contact Test

目的:

A.保证待测芯片所有信号引脚与测试机连接正常

B. 并且没有信号引脚与其他信号引脚、电源或地发生短路

测试方法:

A. 所有管脚设为0V

B. 待测管脚上施加正向偏置电流”I”,

C. 测量由”I”引起的电压,

D. 如果该电压小于0.1V,说明管脚短路,

E. 如果电压大于1.0V,说明该管脚开路,

F. 如果电压在0.1V和1.0V之间,说明该管脚正常连接。

测试原理图如下:

另外:测试O/S也可以用跑向量的方式测试,可将各管脚视为输出无波形变化,测试Z状态。

2、静态电流

静态电流:是指芯片在空闲状态时,消耗的最大电流,一般用ISBY表示

目的:挑选出功耗较大的IC

因为ISBY较大的IC一般意味着器件存在结构缺陷,或者已经损坏,有时也会在测试完功能后再测试静态电流,如一些闪灯芯片

测试方法:一般是对IC的VDD脚加电压,其它脚悬空,测试IC消耗的电流

其它情况可能有要求对IC的所有输入脚置高或低电平再测试静态电流,可根据资料要求来测试

3、动态电流测试

动态电流:是指芯片在工作时状时,无负载时消耗的最大电流,一般用IDD表示

目的:挑选出功耗较大的电路

因为IDD较大的IC一般意味着器件存在结构缺陷,或者已经损坏。

测试方法:一般是对IC的VDD脚加电压,给IC的工作条件,使IC进入工作状态

对同一颗IC施加同样的电压,静态电流一定比动态电流小

静态电流和动态电流测试,相当于是测试IC的VDD与GND之间的阻抗,

如VDD=5V,ISBY上限为5uA, 根据欧姆定律得到可接受的最小阻抗为1M欧姆

当为静态时阻抗较大因而测到的电流较小,为动态时阻抗较小,测得的电流较大

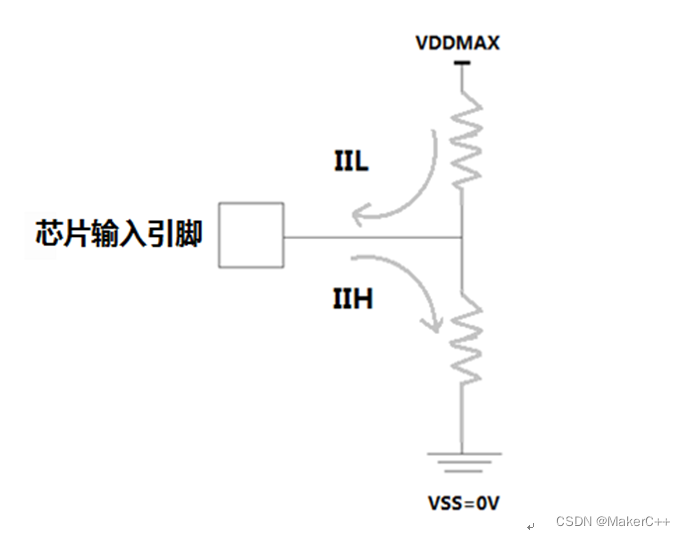

4、漏电测试(IIL,IIH,IOZ)

IIL:是驱动低电平(L)时的输入(I)电流(I)

测试目的:IIL测试测量的是输入管脚到到VDD的阻抗

IIH:是驱动高电平(H)时的输入(I)电流(I)

测试目的:测量的是输入管脚到VSS和VDD的阻抗

IOZ:指的是当一个低电平(或高电平)施加在一个处于高阻态(Z)的输出管脚(O)上,管脚上产生的漏电流(I);

IOZ:测试的目的是确保器件输出管脚被预置为高阻态时,其输出阻抗足够高,或者说管脚能处于“关闭”状态。

此项测试确保输入阻抗满足参数设计要求,并保证输入端不会吸收高于器件规格书定义的IIL/IIH电流。另外,这也是验证和发现COMS工艺制程中是否存在问题的好方法。

理想条件下,可以认为输入及三态输出管脚和地之间是开路的。但实际情况,它们之间为高电阻状态。它们之间的最大的电流就称为漏电流,或分别称为输入漏电流和输出三态漏电流。漏电流一般是由于器件内部和输入管脚之间的绝缘氧化膜在生产过程中太薄引起的,形成一种类似于短路的情形,导致电流通过。

测试原理图如下:

5、转换电平测试(VIL,VIH)

VIL:(输入低电平)表示最坏情况下,输入端电压能被识别为0的最大电压

VIH:(输入高电平)表示最坏情况下,输入端电压能被识别为1的最小电压

目的:测试是确保输入为VIL/VIH时,输入管脚能正确识别逻辑状态

测试方法:VIL,VIH测试需结合测试向量进行测试,如向量能PASS,则VIL,VIH参数正常

如向量FAIL,则VIL,VIH未达到设计规格的要求

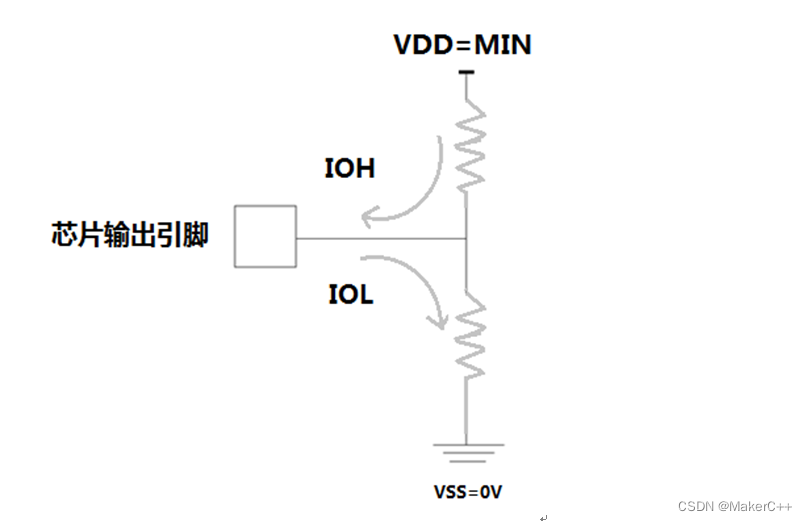

6、输出驱动电流测试(VOL,VOH,IOL,IOH)

VOL:(输出低电压)代表输出在低状态时一个输出产生的最大电压。

VOH:(输出高电压)代表输出在高状态时一个输出产生的最小电压

IOL:(输出低电流)代表输出在低状态时一个输出的灌电流能力。

IOH:(输出高电流)代表输出在高状态时一个输出的源电流能力

目的:当在电流负载下驱动有效输出时,VOL/IOL/VOH/IOH测试验证输出端的阻抗。这个测试确保保持正确的VOL/VOH电压时输出将提供规定的IOL/IOH电流。

测试方法:运行功能测试期间,输出端需要灌入或拉出适当的IOL/IOH电流,输出比较电路则确定输出端是否仍能保持相应的VOL/VOH电平。如果输出端比较脆弱,不能灌入或拉出适当的电流,则比较电路会发现对应电平在边界之外,测试结果为失效

测试原理图如下:

四、 交流参数测试

交流参数测试测量器件晶体管转换状态时的时序关系。交流测试的目的是保证器件在正确的时间发生状态转换。输入端输入指定的输入在特定时间后在输出端检测预期的状态转换。 交流测试有频率测试,传输延迟测试,建立和保持时间测试等,此处只介绍频率测试

1、频率测试

测试芯片指定管脚的输出频率,常见的有振荡端,测试端,COM脚,SEG脚输出频率测试

测试目的:

①、器件在规定的参数条件下,是否可正常起振

②、器件在规定的参数条件下,输出频率是否符合设计或应用要求。

五、功能测试

1、基础术语

测试向量:是器件一系列所设计的逻辑功能的输入输出状态的描述。

真值表:指逻辑电平的一系列0、1序列或其他表征。

测试时钟:在功能测试中,输入时钟的频率,即每单元测试向量所持续的时间

输出采样:在功能测试中,IC的输出信号在周期内的某个时间点被评估的过程。

信号格式:输入信号的波形格式

功能测试是验证IC是否能正确实现所设计的逻辑功能,为此,需生成测试向量或真值表以检测IC中的错误,真值表检测错误的能力可用故障覆盖率衡量,测试向量和测试时序组成功能测试的核心。

2、输入数据

输入数据由以下因素的组合构成:

测试向量数据(给到IC的指令或激励)

输入信号时序(信号传输点)

输入信号格式(信号波形)

输入信号电平(VIH/VIL)

时序设置选择(如果程序中有不止一套时序)

最简单的输入信号是以测试向量数据形式存储的一个逻辑0或逻辑1电平,而代表逻辑0或逻辑1的电平则由测试头中的VIH/VIL参考电平产生。

大部分的输入信号要求设置为包含唯一格式(波形)和时序(时沿设定)的更为复杂的数据形式,主程序中会包含这些信息并通过相应的代码实现控制和调用。

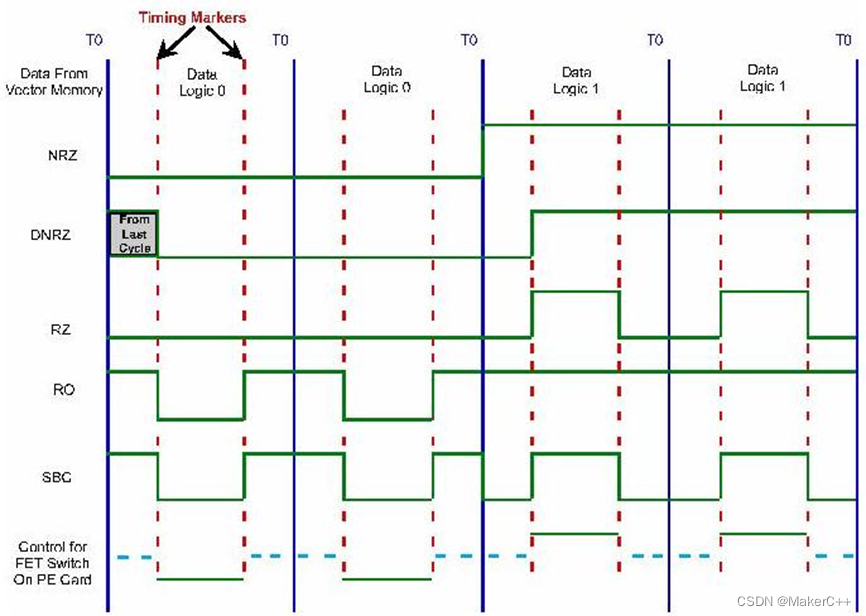

3、输入信号格式

信号的格式很重要,使用得当可以保证规格书定义的所有AC参数均被测试。信号格式与向量数节据、时沿设定及输入电平组合使用可以确定给到DUT的输入信号波形。下图给出了一些信号格式的简单描述

NRZ Non Return to Zero,不返回,代表存储于向量存储器的实际数据,它不含有时沿信息,只在每个周期的起始(T0)发生变化。

DNRZ Delayed Non Return to Zero,延迟不返回,顾名思义,它和NRZ一样代表存储于向量存储器的数据,只是周期中数据的转变点不在T0。如果当前周期和前一周期的数据不同,DNRZ会在预先定义的延时点上发生跳变。

RZ Return to Zero,返回0,当数据为1时提供一个正向脉冲,数据为0时则没有变化。RZ信号含有前(上升)沿和后(下降)沿这两个时间沿。当相应管脚的所有向量都为逻辑1时,用RZ格式则等于提供正向脉冲的时钟。一些上升沿有效的信号,如片选(CS)信号,也会要求使用RZ格式。

RO Return to One,返回1,与RZ相反,当数据为0时提供一个负向脉冲,数据为1时则保持。RO信号也有前(下降)沿和后(上升)沿。当相应管脚的所有向量都为逻辑0时,RO格式提供了负向脉冲的时钟。一些下降沿有效的信号,如始能(OE/)信号,会要求使用RO格式。

SBC Surround By Complement,补码环绕,当前后周期的数据不同时,它可以在一个周期内提供3个跳变沿,信号更为复杂:首先在T0翻转电平,等待预定的延迟后,在定义的脉冲宽度内表现真实的向量数据,最后再次翻转电平并在周期内剩下的时间保持。SBC是运行测试向量时唯一能同时保证信号建立(setup)和保持(hold)时间的信号格式,也被称为XOR格式。

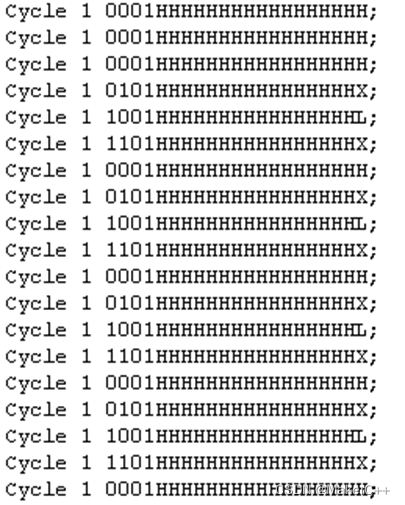

4、输出数据

输出部分的测试由以下组合:

测试向量数据(期望的逻辑状态)

采样时序(周期内何时对输出进行采样)

VOL/VOH(期望的逻辑电平)

IOL/IOH(输出电流负载)

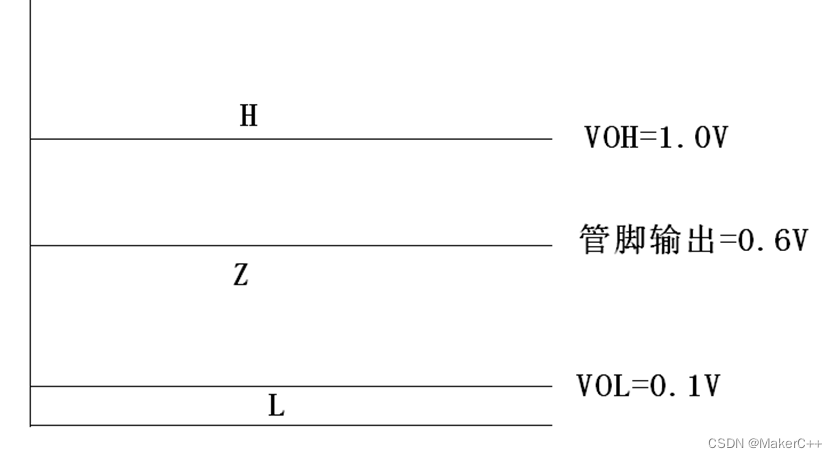

测试向量如下图示:

5、测试输出

功能测试期间,程序会为每个输出管脚在测试周期内指定一个输出采样时间,在这个时间点上,比较单元会对输出进行采样,再将采样到的IC输出信号电平和VOL/VOH参考电平相比较。

测试向量含有每个管脚的期望逻辑状态。如果期望是逻辑0,当采样进行时,IC的输出电平必须小于或 等于VOL;如果期望时逻辑1,则必须大于或等于VOH。部分测试系统还拥有测试高阻态的能力。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)