#VERDI# 关于Verdi工具的实用小技能汇总

目录

13. 利用 VC Apps 中的 Find Instance with Module Def Name。

对于做数字集成电路的工程师来说,Verdi可以说是最常用的代码和波形观察工具了。这里列几个使用中的小技巧,说不上高明,不过自己用着感觉还是蛮有效率的。

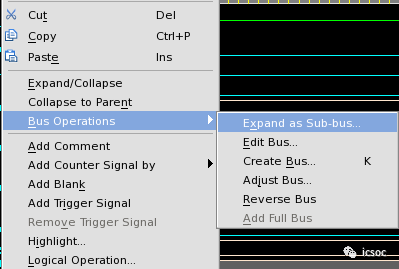

1、总线拆分

分析波形的时候有时候需要把一个多比特的bus拆分成几个位宽较小的bus,以方便观察数值。例如把一个8比特的bus拆成两个2比特的bus,可以右键点击这个bus,在弹出的菜单中点击Bus Operation,在弹出的对话框中的Every后面的输入框,start 输入5, end 输入2, Every 输入2,意思是每2比特拆成一个bus,点击ok,就会看到出现了两个比特的bus信号以及对应的波形。

2、统计次数

统计出某个信号在特定时间段内的跳变的次数。这个结合下一节的逻辑运算,可以把一些复杂的波形分析用直观的形式表现出来。还是右键点击波形窗口左边的某个信号名字,在弹出菜单中选择Signal Event Report。

在弹出的对话框中,可以关注感兴趣的内容,比如Rising#,指的是默认Markers标定的时间段内,该信号的上升沿次数。这样就不用很辛苦的放大波形,用眼睛一个一个去数了。

3、逻辑运算

在一个频繁变化的信号、尤其是多比特的bus信号中观察是否出现了某个值,有时候可以通过搜索来追踪。但是如何一目了然地看到呢?通过右键点击该信号,在弹出的菜单上点击Logical Operation,通过新建一个信号,该信号是待观察信号的某种逻辑表达式。

比如,想知道这个state等于0x7的分布情况,就可以新建一个信号state_is_7等于state==0x7,这样看这个新信号什么时候为1,就可以了解特定状态的分布情况了。

4、manage.rc

manage.rc可以管理多个rc文件,实现每次启动Verdi都能载入预设的设置,同时不受上次启动Verdi后保存的设置影响。还可以保存本次使用过程中更改过的设置,以便更新预设设置。这个略微有些复杂。在启动Verdi时,需要加个参数。

-managercFile some_path/manage.rc这个manage.rc的内容大概是这样的:

@Manage rc file Version 1.0[File]default_file = ~/load_only.rcworking_file = ./novas.rc[Load]default_file[Save]working_file = MODIFIED_KEY

例子中作为只读的default_file文件,可以放一些自己习惯或者喜欢的设置。比如tab等于4还是8,各种界面的字体,以及其它一些每次启动Verdi都希望生效的设置。working_file用来保存本次使用更改的设置,如果有想长期预设的,可以从中copy出来到default_file,这样方便升级迭代。

通过如下常规的参数调用

-rcFile some_path/some.rc也可以读入一个rc文件实现类似预设功能,不过这种方法的缺点是这个rc文件会被当前调用覆盖。后果就是下次启动的Verdi会带有上次使用的痕迹,比如打开波形文件的目录位置。用的次数多了,不胜其烦。干脆用manage.rc来彻底的解决。

5、Trace代码过程中波形窗口保持前置

不知道从哪个版本开始,Verdi默认打开了Active Detection,Trace窗口在trace过程中会被激活前置,造成波形窗口被遮挡,也是不胜其烦。当然这也属于个人喜好问题。

那如何保持波形窗口始终在前呢?首先需要在Trace下拉菜单中取消Active Detection,然后点击波形窗口右上角的Keep as Top。

这样在代码Trace时,波形始终可以看到,方便debug。Active Detection可以在rc文件中预设。Keep as Top还没有找到预设的方法。

6、Parameter 提示的默认进制

在Verdi中,如果把鼠标放到Verilog代码中的parameter上,可以提示其值是多少。因为各种原因,有时候会以二进制的形式提示,如果这个parameter是32比特,那把这个二进制看明白也太费眼睛了。简单的话还是16进制比较易读。这个可以在下图中的Parameter Value Radix中设置。当然也可以把它加入rc文件进行预设。

7. 数字信号的模拟化呈现

Verdi 提供了既简单又直观的操作,去绘制数字信号的模拟变化趋势。尤其是在观察周期性计数的数字信号时,例如调制频率的变化,还有 FIFO 读写地址的变化,这种方式基本是可以做到一目了然的。

操作方式:nWave 窗口菜单 - Waveform - Analog Waveform

对于 Verdi 这个工具来说,它对于数字信号本身的含义目前还没有智能到可以自动识别。所以我们需要指定特定数字信号的表示方式(Notation),是无符号、二补码还是补码等等。

操作方式:nWave 窗口菜单 - Waveform - Set Notation

8. 模拟波形的显示范围

还有一个可能遇到的局限性就是,Verdi 在绘制数字信号的模拟波形时,默认会按照整个波形的动态范围来绘图。如果一个数字信号的初始值和工作时实际的动态范围差别很大,那么观察实际工作时的模拟波形时,波形变化的幅度相比整个动态范围就会太小,无法明了的看到小动态范围的变化趋势。

手动调节显示范围

还好 Verdi 提供了手动调节显示范围的功能。

操作方式:nWave 窗口菜单 - Analog - Zoom Value...

根据需要调节上限和下限,调节过程中波形是实时更新的。

对比效果如下图,第一个信号是默认范围的,动态变化缩成一条直线了,没有观察价值。第二个信号是调整了范围的,可以清楚的看到变化趋势。第三个是原始的数字信号。

自动调节:切换 FSDB 文件

还有一个比较笨的解决方法是,写出 FSDB 文件时,根据特定信号,从数字信号开始动态变化的时候,做一个文件切换。这样就把数字信号初始化部分的波形分离出去。当我们着重分析动态变化的部分时,就不需要加载初始化部分的波形。Verdi 在绘制模拟波形的时候,只会看到小动态范围的数值,绘制出来的变化趋势就足够清楚了。

$fsdbDumpfile("tb_000.fsdb");

$fsdbDumpvars(0, tb);

@(posedge some_trigger_signal);

$fsdbSwitchDumpfile("tb_001.fsdb");

9. 自动调节:加载特定时间范围

当然作为团队项目的螺丝钉,有时候不方便控制 FSDB 文件的产生方式,那么在加载 FSDB 文件的时候,可以选择指定一个时间范围。感谢读者 @Erik Li 提供的这个技巧。

操作方式:nWave窗口菜单 - Open,选择 FSDB 文件到 Target Name 后,点击左下方的 Options... 按钮。

在弹出的对话框中选中 Open File By Time Range,然后点击 OK 按钮。

再点击 OK 按钮,在弹出的对话框中就可以选择感兴趣的时间起止范围了。

10. 如何提高螺丝钉的自我修养

今天就到这里。最后再分享一个最近才发现的 Verdi 调用参数。

verdi -preTitle "some text"

螺丝钉做久了,需要同时打开的 Verdi 窗口数量与日俱增。怎么从密密麻麻的任务栏图标中找到要找的那个,是个麻烦但不紧急的问题。除了贯彻断舍离、及时关闭短期内不需要的窗口之外,用上面的选项为每一个 Verdi 窗口做个简洁唯一的命名,也是一个不那么有效的解决之道。

11. 跳转到指定行号

其实日常的频繁、快速地查看 Verilog 源代码,一般是在独立的文本编辑器中完成的。比如,VCS 编译产生的 log 文件中,对应的 Warning、Error 的后面会跟着相关源文件的路径、行号。如果用的编辑器是版本比较新的 Vim,那么简单的 gF 指令就可以迅速的从 log 文件跳转到对应源文件,而且光标会体贴的定位在出错行。如果是仍未默认支持的旧版 Vim,那么自己可以添加一个函数,可以参考这篇文章。

问题背景:这种方式在门级仿真的场景中会不太灵光。因为门级网表通常都非常巨大,用 Vim 类的编辑器打开一次会非常缓慢,频繁跳转造成的等待就更难以接受了。

浏览门级网表诸如此类的超大文件,用 Verdi 是个不错的选择。在 Verdi 的 Source 窗口中,如何快速跳转到指定的行呢?

用鼠标拖动当然是种办法。但更快捷的是,在 Source 窗口下,按 g 键。会弹出一个小窗口,输入行号,点击确定即可。

12. 源文件之间或不同逻辑层次的切换

有时候在 Verdi 中需要频繁的在两个 Verilog module 之间做切换,做一些对比的工作。如果这两个 module 所处的层次距离比较远,那么快捷的切换就显得特别重要了。这里介绍两个小技巧。

第一个是利用 Verdi 支持多 Source Tab 的功能。在两个不同的 Source Tab 中分别打开不同的 module,通过鼠标切换 Source Tab 来实现源文件或者逻辑层次的切换。

打开新的 Source Tab 的比较方便的方法是,在感兴趣的 Instance 上点击右键,然后在右键菜单上点击 Display Source Code in New Tab.

效果类似下图。

13. 利用 VC Apps 中的 Find Instance with Module Def Name。

首先打开 Tools 菜单中的 VC Apps Toolbox。

在 Design Exploration 目录中找到上述名字的 App,然后双击执行。

在出现的对话框中输入感兴趣的 module 名字,支持通配符。然后点击确定。

在 Verdi 下部的调试窗口中会出现一个新的大概叫做 SmartLog 的页面,其中列出了按照 module 名字搜索出来的所有 Instance。单击某个 Instance,Source 页面就会跳转到对应的地方。

重复执行上述过程,但搜索不同的 module name,会形成独立的 SmartLog 页面。这样通过切换 SmartLog 页面,也可以很方便的在多个设计中切换。

14. 统计之 Grid Option

我们之前介绍过用 Verdi 提供的Signal Event Report来统计一些信号的变化。

最近学习到了一种新方法。详情可以阅读次条转载的这篇来自公众号数字ICer的文章。

这里简单描述一下操作步骤。

-

选中一个要统计的信号

-

点击菜单 View - Grid Option

-

如下图,勾选 Grid on,按需选择统计依据的信号沿,如上升沿

-

勾选 Grid Count with Start Number,默认是0,也可以按需设置

绘出的 grid 效果如下图,可以很方便的来数数了。

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)