集成电路中的ESD防护,一篇入门

随着半导体制造工艺的特征尺寸越来越小,静电放电(ESD,Electeo-Static Discharge)已经成为集成电路中最重要的可靠性问题之一。半导体制造工艺的不断改进使得ESD防护设计越来越困难,部分产品会出现因ESD保护能力不足而导致失效。本文将对ESD的产生、测试、防护进行概述。

目录

1.3.1人体放电模式(HBM,Human Body Model):

1.3.2机器放电模式(MM,Machine Model):

1.3.3元器件充电模式(CDM,Charge Device Model):

1.3.4电场感应模式(Field-Induced Mode):

1集成电路中ESD现象概述

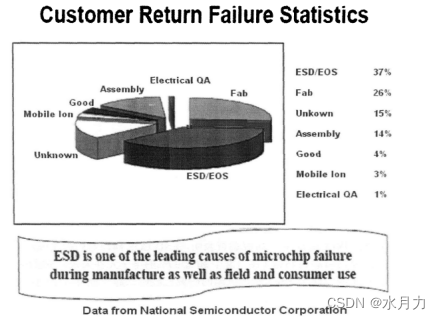

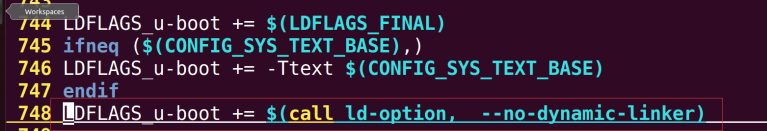

CMOS 工艺集成电路制造技术已经进入纳米时代,随着特征尺寸的降低,ESD (Electro-Static Discharge,静电放电)问题越来越成为集成电路中最主要的可靠性问题。所谓ESD现象,就是在集成电路芯片的制造、运输、使用过程中,芯片的外部环境或者内部结构会积累一定量的电荷,这些积累的电荷会瞬间通过芯片的管脚进入集成电路内部。瞬间通过集成电路内部的峰值电流可以达到数安培,这个瞬态大电流值足以将芯片烧毁(图1),这就是集成电路中ESD现象的基本过程。研究调查表明,ESD问题是引起集成电路产品失效的最主要的可靠性问题(图2),超过37%的电子元件失效是ESD由引起的。对集成电路中 ESD物理机制的研究已经越来越受世界各国的重视,国内外各大集成电路设计公司和代工厂都把 ESD问题提上了战略高度。

图 1 集成电路内部ESD失效的扫描图

图2 ESD问题是集成电路中最主要的可靠性问题之一。

1.1ESD基本概念

ESD定义:ESD(Electro-Static discharge)的意思是“静电释放”。ESD是20世纪中期以来形成的以研究静电的产生、危害及静电防护等的学科。因此,国际上习惯将用于静电防护的器材统称为ESD,中文名称为静电阻抗器。 静电放电,很容易造成电子元件或电子系统遭受过度电应力而永久破坏。

在芯片制造、生产、测试、搬运等过程中,静电会积累在人体、仪器、设备之中,甚至芯片本身也会积累静电,这些静电一旦在某些情况下形放电通路,那么芯片便有可能遭受高压、大电流的静电放电损害。ESD的防护:1加强工作场所对静电积累的控制 2必须加强集成电路本身对静电放电的耐受能力,ESD保护设计成为所有芯片设计时必须考虑的一部分。

1.2ESD的基本认识

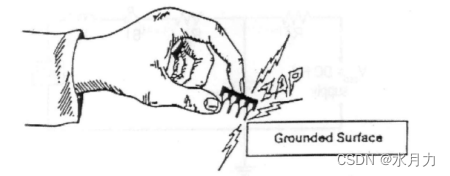

当两个带有相反电荷的物体相接触时就会发生放电的现象,而且这种现象在芯片使用和生产中随处可见。

比如摩擦、离子注入等过程中很容易造成芯片中的静电积累,当积累有电荷的芯片与人体、机械导体、其它芯片接触时,就有可能发生静电放。

这个过程可能持续几纳秒到几百纳秒,放电电压可能高达几百伏甚至上千伏,放电电流可能高达数安培甚至数十安培,芯片内的器件在这样高压、大电流的作用下会发生不可逆的破坏,这是需要设计ESD保护电路的根本原因。

1.3ESD产生来源

1.3.1人体放电模式(HBM,Human Body Model):

是指因人体通过磨擦或其他因素积累了静电,此时当人去碰触IC时,人体上的静电便会经由IC的PIN脚进入IC内,再经由IC放电到地。芯片级一般用HBM来做测试。如图1.3所示

1.3.2机器放电模式(MM,Machine Model):

是指机器(例如机械手臂)本身积累了静电,当此机器碰触IC时,该静电便经由IC的PIN脚放电。此放电的过程时间更短,电流更大。如图1.4所示。

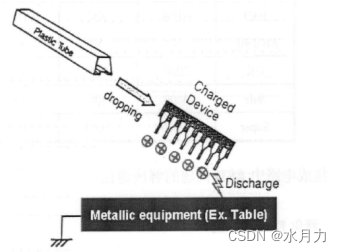

1.3.3元器件充电模式(CDM,Charge Device Model):

是指IC先因磨擦或其他因素而在IC内部积累了静电,但在静电积累的过程中IC并未受到损伤。这种带有静电的IC在处理过程中,当其PIN脚碰触到接地面时,IC内部的静电便会经由PIN脚自IC内部形成放电,此种模式的放电时间可能只在几ns内。(最厉害)

1.3.4电场感应模式(Field-Induced Mode):

这种模式是由于外在电场影响芯片电荷引起的。过程类似于CDM。

图3 HBM模式的ESD模型

图4 CDM模式的ESD模型

2集成电路中ESD问题的解决途径

避免ESD的措施

包围隔离

为了防止静电电荷进入静电敏感电子器件造成损伤,在生产制造中对这些敏感电子器件都用抗静电材料包装,或使用有盖的抗静电容器储放;而在静电敏感区域(如 SMT制程)工作的人员,则还要穿着静电服。

接地

将工作环境中的人员及设备通过不同的地线接地。静电敏感区的操作人员可以带上接地的防静电腕带,该区域中的操作台面应该接地良好。

排除

为了防止静电电荷进入电子器件内部,可使用离子风扇以中和电子器件表面所带静电。

调整湿度

湿度也是影响静电电荷积累的重要因素,适当增加湿度可降低ESD电压(表1.3)。在电子制造厂的ESD敏感工作区域适当地通过加湿器增湿可以降低ESD损伤电子器件的概率,这也是电子制造厂为何多在南方建厂的原因之一。

表1 湿度和ESD电压

避免 ESD的措施一般只能出现于产品交付客户以前,对于终端用户显然不太适合(举例来说,我们不可能在使用手机之前先戴上静电手环)。因此,需要在电子产品的设计时候加上 ESD 防护单元,这个防护单元可以在芯片外加上专用ESD防护器件(Off-Chip Protection),也可以在芯片内部加上 ESD 防护单元( On-Chip Protection)。

2.1片外ESD防护

片外ESD保护器件常见的有陶瓷电容、齐纳二极管、肖特基二极管、MLV(Multi-Layer Varistor,多层变阻器)和TVS (Transient Voltage Suppresser 瞬态电压抑制器)。MLV是一种基于ZnO压敏陶瓷材料,其工作原理是利用压敏电阻的非线性特性,当过电压出现在压敏电阻的两极间,压敏电阻可以将电压钳位到一个相对固定的电压值,从而实现对后级电路的保护(图1.6)。MLV在很多领域得到了广泛的应用,如手机、机顶盒、复印机的片外ESD保护。另外一种片外保护电路是TVS(图1.7)。TVS通常并联于被保护电路,当瞬态电压超过电路的正常工作电压时,二极管发生雪崩,为瞬态电流提供通路,使内部电路免遭超额电压的击穿或超额电流的过热烧毁。

图 5MLV的内部结构示意图

图6 TVS的内部结构示意图

2.2片上ESD防护

片上ESD防护就是在芯片里集成ESD 防护单元,当静电信号到来的时候能够保护内部电路免遭烧毁,相比于片外ESD防护电路,片内ESD防护电路的优点是:直接而且显著增强 ESD 防护能力,节省板级空间,减少系统成本并降低设计与布线的复杂度[2,22,30-32]。虽然从目前情况来看,片上集成ESD 防护电路的难度相当大:工艺的进步使集成电路的栅极氧化层厚度越来越薄,IC自身的ESD防护能力降低,先进工艺使传统的片上ESD 防护措施效果减弱。但是片上ESD 防护单元的设计,对电子产品抗击ESD伤害有着至关重要的作用。

2.3集成电路中ESD问题解决

综上所述,ESD问题的解决主要有三种方法:一、避免 ESD的发生;二、片外专用 ESD保护器件;三、片上 ESD防护单元设计。在实际ESD解决方案中,通常是从三种方法同时入手解决ESD问题。但是由于ESD事件能够被控制却不能杜绝,并且片外ESD防护器件要额外占用很多系统级/板级资源,因此最经济而且有效的ESD问题的解决方法是合理设计片上ESD防护单元,这个单元必须能够有效地保护内部电路抵御ESD 冲击。下文将重点对片上ESD防护技术进行研究。

3 ESD的典型测试方法:

集成电路中的 ESD测试可以分为后端检验型测试和前端研究型测试两类。后端检验型测试体现在产品的后端可靠性测试中,为了保证芯片产品的良率,芯片需要通过一定值(通常为2kV)的 ESD检验才算合格。现有芯片级的ESD检验多采用ZAPMASTER测试仪。系统级的ESD检验多采用电子枪。

前端研究型测试主要应用于芯片研发阶段,本阶段的测试可以预先估测产品的ESD承受能力,从根本上保证芯片产品的良率。为了获得 ESD防护器件的关键性能指标,传输线脉冲技术(Transimmison Line Pusle,简称TLP)是研究型测试中最主要的工具。

3.1一般测试方法

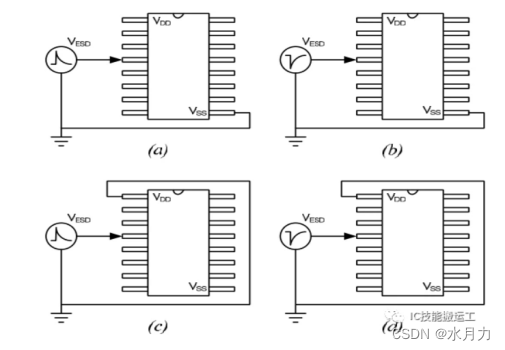

静电的积累可能是正的或负的电荷,因此静电放电测试对同一PIN脚而言是具有正、负两种极性。对于每一个I/O PIN而言,进行ESD测试时,有下列四种组合:

:VSS引脚接地,正的ESD电压出现在I/O PIN并对VSS脚放电,此时VDD与其它PIN脚浮空。

NS mode:VSS引脚接地,负的ESD电压出现在I/O PIN并对VSS脚放电,此时VDD与其它PIN脚浮空。

PD mode:VDD引脚接地,正的ESD电压出现在I/O PIN并对VDD脚放电,此时VSS与其它PIN脚浮空。

ND mode:VDD引脚接地,负的ESD电压出现在I/O PIN并对VDD脚放电,此时VSS与其它PIN脚浮空。

上面是针对I/O PIN与电源和地之间发生ESD的情形,等效原理图如下所示。

图7 几种基本ESD测试方法

另外ESD也有可能发生在任意的I/O引脚之间,若两只PIN脚之间无直接的相关电路,静电放电电流会先经由某部分的电路到VDD或VSS电源线上,再由VDD或 VSS电源线到另一引脚流出IC。基于1、2下图a、b中给出了改进的Pin-to-Pin测试方法,情形与上述基本类似,只是正、负ESD电压放电发生在一个I/O引脚与其他I/O引脚之间,测试这种情况时电源和地浮空。

图8 ESD基本测试方法

ESD也有可能发生在电源和地的引脚上,这种情况测试时也分正、负两种情况,测试时只在电源和地之间加测试信号,其余引脚浮空。

3.2 Zapmaster测试

现有的Zapmaster测试仪器有多种,常用的有Thermo KeyTek 公司生产的ZAPMASTER测试系统。本仪器相对应的测试标准为GJB548A-3015。短路测试波形要求上升时间小于10ns,下降时间大约为150上20ns,每次测试在管脚正负测试三次,测试时间间隔为一秒。2000V的 HBM电压相当于1.33A的尖峰电流。Zapmster测试仪器中判决器件ESD失效有三种模式:包络线失效(ENV),开路失效(OC)和短路失效(SG)。

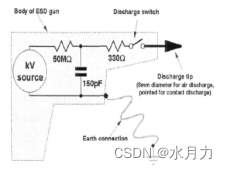

3.3电子枪测试

和Zapmaster一样,电子枪ESD测试是另外一种后端检验型测试。电子枪测试通常在芯片组装成整机电子产品之后进行系统级的终端ESD 测试,目前常用的测试标准是IEC 61000-4-2,测试模式分为接触式放电(Contact Discharge)和空间放电(Air Discharge)。图 1.11是电子枪的示意结构图,电子枪的ESD等效电容为150pF,等效ESD 电阻是330Q2。商用产品的系统级空间放电标准一般是l5kV。

图9 电子枪的实物图

图10 电子枪的等效电路图

4测试判断ESD失效判断

绝对漏电流:当IC进行ESD测试后,在其 I/O PIN上加一定电压,漏电电流超过规定值,即可认为ESD失效。

相对I-V漂移:当IC进行ESD测试后,其 I/O PIN的I-V曲线漂移超过规定值,即可认为ESD失效。

功能判断:当IC进行ESD测试后,其 I/O PIN的功能已经不满足性能规格,即可认为ESD失效。

5 ESD防护设计

5.1ESD防护设计基本要求

ESD防护设计的目的是,当集成电路任意两个输入/输出引脚之间发生ESD事件时,集成电路内部的ESD防护系统能及时开启来泄放掉大量的瞬时电流/电压,使内部电路免遭破坏。此外,在集成电路正常工作时,即未发生ESD事件时,ESD系统引入的寄生参数不会影响电路的正常工作。具体要求为:

1、当ESD 冲击出现时,ESD保护器件能够快速开启,高效泄放冲击大电流,钳位到安全电压。

2、在ESD 冲击下具有一定程度的鲁棒性,确保ESD保护电路自身能够承受外“部冲击。

3、当IC处于正常工作状态时,ESD保护器件处于关闭状态,不影响电路正常功能。

4、ESD保护电路一般在IO pad的周围,需保证较小的IO延迟.

5、占用较小的芯片面积,提供较高的ESD保护能力。

6、保持较高抗门锁能力。

7、尽量在不增加额外步骤或掩膜的情况下制造ESD保护电路。

5.2 ESD防护电路设计

5.2.1ESD保护电路中器件的使用

在集成电路设计中加入ESD保护电路,当ESD来的时候,ESD保护电路发挥保护效果,避免集成电路内的元件被ESD损伤。

当ESD电压出现在芯片PIN脚上时,位于该PIN脚附近的ESD保护电路必须及早地导通来泄放ESD电流。因此,ESD保护电路所使用的元件必须要具有较高的击穿电压或较快的导通速度,同时也需要注意在芯片正常工作时ESD保护电路不能影响芯片功能。

电阻(Diffusion or poly resistor)、二极管(P-N junction)、金属-氧化物-半导体晶体管(NMOS or PMOS)、厚氧化层元件(Field-oxide device)、寄生的双极型晶体管(BJT)、寄生的可控硅元件(SCR device)、这类器件可以组合使用可单独使用。

5.2.2ESD防护电路

基于上述4种可能发生的ESD事件,ESD可能会发生在I/O、PIN与电源和地之间,也会发生在不同的I/O PIN之间,也可能出现在电源和地之间,因此对于ESD保护电路的设计需要考虑所有可能发生ESD的情形。

图11 ESD防护电路

5.3常见的ESD保护电路设计

目前现有的ESD保护电路及其功能模块的设计。

图12 ESD防护电路的功能模块和保护模块

在全芯片的ESD结构设计时,需注意以下原则:

(1)外围VDD、VSS走线尽可能宽,减小走线上的电阻;

(2)设计一种 VDD-VSS之间的电压箝位结构,且在发生ESD时能提供VDD-VSS直接低阻抗电流泄放通道。对于面积较大的电路,在芯片的四周各放置一个这样的结构,若有可能,在芯片外围放置多个VDD、VSS的PAD,也可以增强整体电路的抗ESD能力;

(3)外围保护结构的电源及地的走线尽量与内部走线分开,外围ESD保护结构尽量做到均匀设计,避免版图设计上出现ESD薄弱环节;

(4)ESD保护结构的设计要在电路的ESD性能、芯片面积、保护结构对电路特性的影响如输入信号完整性、电路速度、输出驱动能力等进行平衡考虑设计,还需要考虑工艺的容差,使电路设计达到化;

(5)在实际设计的一些电路中,有时没有直接的VDD-VSS电压箝位保护结构,此时,VDD-VSS之间的电压箝位及ESD电流泄放主要利用全芯片整个电路的阱与衬底的接触空间。所以在外围电路要尽可能多地增加阱与衬底的接触,且N+P+的间距一致。若有空间,则在VDD、VSS的PAD旁边及四周增加VDD-VSS电压箝位保护结构,这样不仅增强了VDD-VSS模式下的抗ESD能力,也增强了I/O-I/O模式下的抗ESD能力。

总结

ESD保护设计随着CMOS工艺水平的提高而越来越困难,ESD保护已经不单是输入脚或输出脚的ESD保护设计问题,而是全芯片的静电防护问题。芯片里每一个I/O电路中都需要建立相应的ESD保护电路,此外还要从整个芯片全盘考虑,采用整片(whole-chip)防护结构是一个好的选择,也能节省I/OPAD上ESD元件的面积。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)