DFT设计 与 芯片测试 ;Scan Chain; DC里的DFT的扫描链设计; 存在异步复位触发器时的扫描链设计;Scan-In Scan-Out

DFT设计 与 芯片测试 ;Scan Chain; DC里的DFT的扫描链设计; 存在异步复位触发器时的扫描链设计;Scan-In Scan-Out

DFT的介绍

DFT(Design for Testability )该设计有助于提高可测试性,从而促进制造过程中的测试和调试,提高了芯片的可测试性和可靠性。

没有一个制造过程是完美的,所以生成出的所有的芯片不是都能正常工作,因此,进行测试(例如DFT)是非常重要的,以确保只有功能正常的芯片被送出去用于后续的封装和应用。对于任何芯片设计,都会存在一定的失效率(Yield)。这就是说,在一块晶圆上制造出的所有芯片中,只有一部分能通过所有的测试并且功能正常。失效率受许多因素的影响,包括制程控制的准确度、材料的质量、设计的复杂度以及测试的严谨度等。尽管芯片制造商会采取各种措施来提高产量,但是一般来说,随着技术节点的缩小(例如从45nm到28nm),失效率会增加,因为制程的复杂度增加以及缩小的尺寸更容易受到各种小的变化和缺陷的影响。

芯片的晶圆测试wafer sort

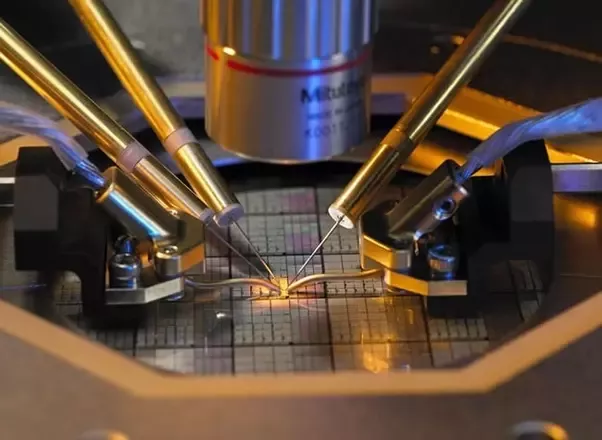

晶圆探测针平台(wafer probe station),它们通常用于进行电性测试,以检查晶圆上的设备是否正常工作。在实施这些测试时,通常会使用来自DFT的测试案例。通过设计自测试,可以生成可以应用于晶圆测试的专门测试向量,这些测试向量可以用于探测潜在的缺陷和故障。然而,这需要设计团队和测试团队之间有密切的协作,以确保测试案例的有效性和准确性。

比如下图所示,在利用扫描链测试到的分析晶圆中有几个器件中测试失效。有一个发现了聚残留物,最后一个器件的闭环接触蚀刻停止层 (CESL) 存在缺陷。

ps, 晶圆越靠近边缘,芯片(一个小方块,即未封装的芯片)就越有可能出现故障。

When good DFT goes bad: debugging broken scan chains

3 mins to know chip test and Package test

DFT的特点

DFT的主要优势包括:

- 提高测试效率: DFT能够简化测试过程,使设计在更高的抽象级别上可以进行测试。这降低了手动测试的工作量,使测试自动化更加可行。

- 提高测试覆盖率: 通过在设计初期就引入DFT,设计师可以确保所有的逻辑都能被适当地测试到。这提高了测试覆盖率,从而减少了制造过程中的缺陷和错误。

- 提高可靠性和质量: 通过提高测试的精度和覆盖率,DFT能够在产品发布之前找出和修复更多的设计缺陷。这可以提高产品的可靠性和质量,从而减少产品退货和售后维修的成本。

- 降低测试成本: 虽然引入DFT可能会增加设计的复杂性和成本,但是它可以降低测试阶段的成本,因为它使得测试能够更有效率地进行。

虽然DFT(Design for Testability)的方法能够提升芯片的测试效率和覆盖率,但是它也有一些潜在的缺点:

- 设计复杂性增加: 在集成电路设计中引入DFT会增加设计的复杂性。设计人员需要在设计初期就计划并实现DFT策略,这需要额外的设计时间和资源。

- 面积和功耗增加: DFT技术如扫描链、内置自测试(BIST)等会引入额外的硬件,例如更多的触发器、测试逻辑电路等。这会导致集成电路的面积增大,同时也可能会增加功耗。

- 性能影响: DFT技术可能对集成电路的性能产生影响。例如,引入扫描链可能会导致时钟路线变长,增加时钟偏斜,这可能影响集成电路的最大工作频率。

- 测试时间和成本: 虽然DFT可以提高测试的效率和覆盖率,但是如果要对每一个晶体管都进行全面的测试,所需的时间和成本可能会非常高。为了克服这个问题,设计人员需要在测试计划中制定出一个合理的折衷方案。

结构测试设计 和 功能测试设计

我们还需要区分验证(Verification)和测试(Testing),前者是检查硬件或软件的设计是否有问题,后者是假设设计是正确的,但可能存在制造故障。本章讲的是后一个概念,但包含测试的结构的设计可能有助于验证和调试设计。一般来说,有两种测试方法。我们可以询问系统是否正常工作(功能测试functional testing)或者我们可以询问系统是否包含错误(结构测试structural testing)。这两种方法乍一看似乎是等同的,但实际上,我们采用的策略可能会对如何开发测试以及应用测试所需的时间产生深远的影响。功能测试意味着一项漫长而困难的任务,因为必须检查系统的所有可能状态。结构测试通常更容易,但依赖于系统的精确实现。

- 功能测试:功能测试针对的是芯片设计规格书中的功能规格,检测芯片是否能够按照设计需求进行工作。这种测试主要关注的是芯片的行为,包括数据处理,通信接口,功耗等等。功能测试的目标是确保芯片的所有功能都正常工作。在硬件的设计阶段需要充分的功能测试和设计验证。

- 结构测试:结构测试是基于硬件实现的详细信息的。在这种测试中,测试人员会根据硬件设计(如逻辑门,电路等)生成特定的测试用例,以查找可能的缺陷和错误。这种测试更多的是针对物理级别的细节,包括对芯片内部结构的评估,比如晶体管,电路互连,逻辑门等。结构测试的目标是确保芯片在物理和电气层面上没有问题。

在芯片生产制造出来后,如果发现硬件功能有问题,基本上是无法修改的(但是如果c代码这种软件代码有问题还是可以改的)。这就是为什么在芯片设计和制造的早期阶段,我们需要进行深入和全面的验证和测试。

ps, "Freeze"在芯片设计和制造的语境下通常指的是“设计冻结”。设计冻结是一个非常重要的阶段,标志着硬件设计已经完成,并且已经准备好进入下一阶段,通常是制造阶段。在设计冻结阶段,所有的设计特性都已经定下来,不再接受更改,除非在之后的验证和测试中发现了重大问题。设计冻结是一个重要的里程碑,因为它标志着设计工作的完成,开始进入生产。

DFT的扫描链设计

DFT,全称Design for Testability,是一种在硬件设计阶段考虑测试的方法,它的目标是在设计时就使得设备或系统能更容易地进行测试。以下是DFT设计的一些基本原则和方法:

- 测试点插入(Test Point Insertion):在硬件设计中,插入额外的测试点,例如观察点和控制点,可以帮助更容易地访问和控制硬件的内部状态。这种方法可以提高硬件的可观察性和可控制性,从而提高测试的效率和有效性。

- 扫描设计(Scan Chain Design ):扫描设计是一种常用的DFT方法,其中所有的触发器(flip-flops)都被连接成一个或多个长的移位寄存器,称为扫描链(scan chain)。通过扫描链,我们可以直接设置和读取硬件的内部状态,从而极大地提高了硬件的可测试性。

- 内置自测试(Built-In Self-Test,BIST):在BIST方法中,硬件被设计为能够执行自我测试。这种方法可以在硬件的运行过程中检测出潜在的故障,并且可以大大减少外部测试设备的需求。

- 测试压缩技术(Test Compression Techniques):测试压缩技术是一种降低测试数据量和测试时间的方法。例如,Xilinx公司的3D IC设计中使用了测试压缩技术,以降低测试成本。

- 故障模型(Fault Models):DFT设计也需要考虑故障模型。一个故障模型是一个假设,它描述了硬件可能出现的故障类型。故障模型的选择可以影响测试的覆盖率和效率。

- 测试策略和计划(Test Strategies and Plans):一个好的DFT设计也需要一个全面的测试策略和计划。这个策略应该详细描述如何,何时,以及在哪里进行测试,包括在制造过程中的测试和在硬件生命周期中的测试。

扫描链(Scan Chain)的设计

在硬件设计中,将触发器 (flip-flops) 替换为可扫描的触发器并以链的形式连接在一起就形成了“扫描链”。在测试模式下,这个扫描链就像是一个移位寄存器,可以通过改变扫描使能信号 (Scan Enable, SE) 的状态,来在正常操作模式和测试模式之间切换。在测试模式下,可以通过扫描输入端口 (Scan Input) 向扫描链中输入数据,然后通过扫描输出端口 (Scan Output) 从扫描链中读出数据。

扫描链,所有的触发器必须连接成一条链,单链或多链。 如果您在一端推送一些数据,而在另一端获得相同的数据,那么它在制造过程中没有错误。

使用扫描链进行测试的目的:进行扫描测试的原因有多种,其中最突出的两个是:

- 测试制造设备中的固定故障(stuck-at faults) ;

- 测试制造设备中的路径的延迟,测试每条路径是否工作在功能频率下;

这种方法的优点在于,它允许我们直接访问和控制硬件的内部状态,极大地提高了硬件的可测试性。通过向扫描链输入一个已知的数据模式,然后读出硬件的输出,我们可以检查这个输出是否与预期的结果相匹配。如果输出与预期的结果不匹配,那么说明在制造过程中可能发生了一些错误。这种方法可以帮助我们在硬件生产的早期阶段就发现和修复问题,从而提高硬件的质量和可靠性。

扫描触发器:扫描链的基本构建块

在触发器的输入处添加多路复用器,多路复用器的一个输入充当功能输入D,而另一个输入充当扫描输入(SI)。D 和 SI 之间的选择由扫描使能 (SE) 信号控制。

扫描链的测试;ATE和ATPG

下图所示时当进行scan chain测试时,发现有些逻辑被卡住了的情况,即有些寄存器有问题,可以通过测试模式测出来失效。如果想定位失效的元件,需要更高级的分析方法和测试方法。

Scan chains – the backbone of DFT

在对扫描链进行测试时,如果发现输出数据与输入数据不一样,确实可能意味着存在问题。此时,ATE (Automatic Test Equipment) 和 ATPG (Automatic Test Pattern Generation) 可以发挥作用,帮助确定问题的具体位置和性质。

- ATE (Automatic Test Equipment): ATE 可以自动执行一系列的测试,收集和分析测试数据。在这种情况下,如果输出数据与输入数据不一样,ATE 可以通过重复执行测试和记录每一次的结果,帮助我们确定问题的一些特性,例如问题是一直存在还是偶尔出现,或者问题是否依赖于特定的输入模式等。

- ATPG (Automatic Test Pattern Generation): ATPG 的主要作用是自动生成能够有效检测硬件故障的测试模式。在这种情况下,ATPG 可以生成一组新的测试模式,用于对硬件进行更详细的测试。例如,它可以生成一系列的测试模式,每个模式只对应于扫描链中的一个特定的触发器,然后通过观察哪些模式导致输出数据与输入数据不一样,帮助我们定位问题的具体位置。

存在异步复位同步化触发器时的扫描链设计

为了实现有效的DFT设计,将flip-flops for reset synchronization 隔离出来,即不被包含到scan chain,这样做的目的是不干扰扫描模式下的复位信号的时序。假设如果被包含进去了,则需要仔细控制Scan-Enable信号的时序,这会使得分析DFT的测试结果变得更加困难。“Input synchronizer is contained in scan path, reset synchronization is not.”

如果用于复位信号同步化(reset synchronization)的触发器包含在扫描链(scan chain)中,则有必要仔细控制扫描使能(Scan-Enable)信号的时序,以确保它们不会干扰扫描模式下的复位信号的时序(扫描模式下用的是pin脚上的,而不是同步后的复位信号)。 这可能会使生成提供良好覆盖率的测试模式和分析测试结果变得更加困难。

其中有两个端口Test和ScanEnable值得注意,当存在两种同步器:一种是给输入信号做同步,另一种是给输入的复位信号做同步;测试模式下所用的复位信号是外界异步的复位信号。Test和ScanEnable通常被称为 “Test Mode Select” 和 “Scan Enable”。例如,可以只在需要进行扫描测试时激活 “Scan Enable”,而在其他测试任务中保持它未激活。同样,也可以只在需要进入特殊的测试模式时激活 “Test Mode Select”,而在其他情况下保持它未激活。这样,可以根据不同的测试需求来选择合适的测试策略和模式。

-

Test:用于选择复位信号是同步后的复位信号还是==同步之前异步的复位信号==。这种设置可以帮助检测和诊断复位相关的问题。

-

ScanEnable:用于选择触发器的模式是在正常功能模式下,还是在测试扫描模式下。

这样分开,可以单独测试哪部分电路失效了。

Design Compiler中插入扫描链

- 扫描单元替换和编译

在sv代码里,把不行包含在扫描链的触发器设置为 dont_touch,这样DC在插入扫描链更换触发器的类型的时候就不会把这两个触发器更改。(ps,这两个触发器是用作reset synchronization)。

// synopsys dc_tcl_script_begin

// set_dont_touch [get_cells RESET_SYNC_FF*]

// synopsys dc_tcl_script_end

DFC1 RESET_SYNC_FF1 (

.D('1), .Q(SYNC_MID_nReset), .C(CORE_Clock), .RN(SYNC_IN_nReset)

);

DFC1 RESET_SYNC_FF2 (

.D(SYNC_MID_nReset), .Q(CORE_nReset), .C(CORE_Clock), .RN(SYNC_IN_nReset)

);

这一步可以在编译compile -scan之后把触发器改为“可扫描的flip flop”。

#compile

compile -scan

- 定义测试协议

-

set_dft_signal -view existing_dft -type ScanClock -port Clock -timing {45 60}:这个命令将Clock端口设置为扫描时钟,时钟周期设置为45至60的范围。 -

set_dft_signal -view existing_dft -type Reset -port nReset -active_state 0:这个命令将nReset端口设置为复位信号,复位信号在低电平(0)时激活。 -

set_dft_signal -view spec -type TestMode -port Test -active_state 1:这个命令将Test端口设置为测试模式选择信号,当Test端口为高电平(1)时,芯片进入测试模式。 -

set_dft_signal -view spec -type ScanEnable -port ScanEnable -active_state 1:这个命令将ScanEnable端口设置为扫描使能信号,当ScanEnable端口为高电平(1)时,扫描触发器进入扫描模式。 -

set_dft_signal -view spec -type ScanDataIn -port SDI:这个命令将SDI端口设置为扫描数据输入端口。 -

set_dft_signal -view spec -type ScanDataOut -port SDO:这个命令将SDO端口设置为扫描数据输出端口。

set_dft_signal -view existing_dft -type ScanClock -port Clock -timing {45 60}

set_dft_signal -view existing_dft -type Reset -port nReset -active_state 0

set_dft_signal -view spec -type TestMode -port Test -active_state 1

set_dft_signal -view spec -type ScanEnable -port ScanEnable -active_state 1

set_dft_signal -view spec -type ScanDataIn -port SDI

set_dft_signal -view spec -type ScanDataOut -port SDO

- 创建DFT协议

create_test_protocol通过修改由创建的协议来定义自定义初始化序列。这个是创建Scan协议,就是让工具理解你定义的scan clock ,scan enable, scan in, scan out ,mode等,为drc检查和insert准备。

create_test_protocol

- 检查是否违反设计规则,它将检查以确保设计已正确设置 DFT。

dft_drc

这里需要注意的是,Autofix可以自动修正一些test DRC的错误,比如:不可控的时钟,不可控的异步置位和复位信号,以及三态和双向信号。set_autofix_configuration可能会使用由测试信号控制的多路复用器自动修复重置和设置信号。

set_dft_configuration -fix_reset enable

set_autofix_configuration -type reset -method mux -control Test -test_data nReset

set_dft_configuration -fix_set enable

set_autofix_configuration -type set -method mux -control Test -test_data nReset

- 扫描路径插入

set_scan_configuration -chain_count 1

preview_dft

insert_dft

然后,在dft_drc里检查如果只有warning S19就是没问题。

SYNOPSYS - DFT Compiler Scan User Guide

RTL Synthesis using Design Compiler

Built-In Self-Test (BIST)

Built-In Self-Test (BIST) 是一种在电路或系统内部实现的测试技术。其主要目的是在不依赖于外部测试设备或手动测试的情况下,能自我检测并报告潜在的故障或性能问题。

电路的可测试性可以表示为:

- 可控性——从主要输入控制内部节点逻辑值的能力。

- 可观察性——在主要输出处观察内部节点逻辑值的能力。

stuck-at model

Stuck-at model 是一种常用的故障模型,它假设一个节点 (例如触发器的输出) 可能会卡在逻辑 0 或逻辑 1 的状态,无论其输入是什么。使用 stuck-at model 进行测试时,可以生成一组测试向量,使得如果存在 stuck-at fault,那么设备的输出就会与预期的输出不一致。

比如下图所示电路中,反相器的输出被卡在了高电平,始终输出高电平,那么这部分电路会被卡在逻辑1上,不论输入输入什么。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)