PCIE时钟解说

很多时候有疑问,CLKREQ#是否要接,首先要知道的是,这个信号是可选的,可要可不要。注意,虽说PCIE时钟有三种架构,但是最常用的还是CC架构,无特殊情况,不要使用其他时钟架构,如果真的要使用其他两种架构,也需要严谨评估先。鉴于PCIE时钟要求多且复杂的,故此文章主要鉴于上一篇文章,给出主要的参数要求,其它详细的要求以及测试方法,后续有机会再编写分享。注意:如果硬件电路这个CLKREQ#没接的话

接上篇文章《clock oscillator,generator,buffer选型杂谈》,今天我们来说下PCIE时钟的要求:

首先先看下PCIE架构组件:下图中主要包括了CPU(ROOT COMPLEX),PCIE SWITCH,BUFFER以及一些PCIE ENDPOINT;而且可知各个器件的时钟来源都是由100MHz经过Buffer后提供。

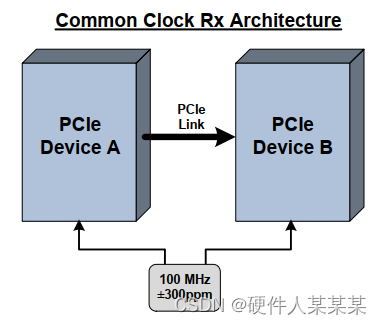

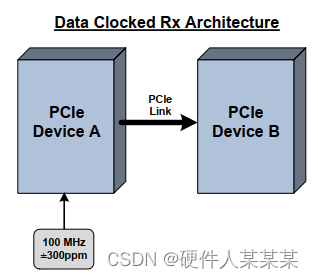

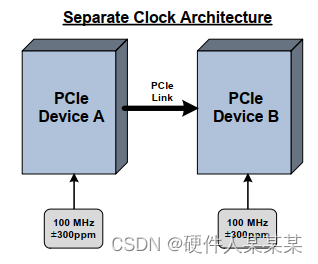

接着上图的架构,我们来简单看下PCIE时钟的三种架构:

Common Clock Architecture:所有设备的参考时钟分布必须匹配到15英寸以内在系统板上。在接收端数据和时钟之间的传输延迟增量必须要小于等于12ns。通常允许PCIE卡上的时钟线长不大于4inch。特别注意这点,涉及到我们实际PCB走线。

Data Clock Architecture:时钟从数据中恢复出来。慎用,有些不支持。

Separate Clock Architecture:

根据有无 SSC 可进一步分为 SRNS ( Separate Refclk with No SSC) 及 SRIS (Separate Refclk with Independent SSC)。

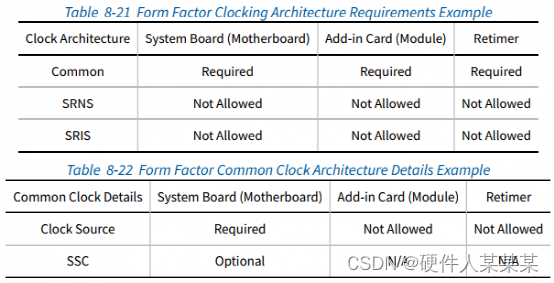

注意,虽说PCIE时钟有三种架构,但是最常用的还是CC架构,无特殊情况,不要使用其他时钟架构,如果真的要使用其他两种架构,也需要严谨评估先。

从下表可知,展频跟非CC架构慎用。

鉴于PCIE时钟要求多且复杂的,故此文章主要鉴于上一篇文章,给出主要的参数要求,其它详细的要求以及测试方法,后续有机会再编写分享。

信号要求:

PCIE_CLK_P/N是差分信号,通常差分阻抗为100Ω,少部分要求85Ω。

电平:HCSL or LP-HCSL。

频率:100±0.03MHz。

频率稳定度:±300ppm,越小越好。

占空比:50%±10%。

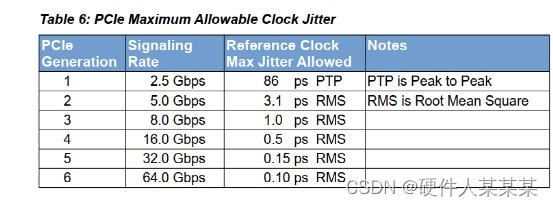

抖动:如下CC模式的要求:

注意:上图给出的是CC时钟架构下的抖动要求;仿真PCIE4.0时候,抖动是按照0.7ps RMS来的;仿真PCIE5.0时候,抖动是按照0.25ps RMS来的;因为标准考虑了实际系统中的额外噪声,故会比较严格。

提到PCIE时钟,相信大部分人会联想到CLKREQ#:

很多时候有疑问,CLKREQ#是否要接,首先要知道的是,这个信号是可选的,可要可不要。那么什么时候需要呢?如果要支持L1-PM子状态(ASPM(Active State Power Management)中的状态)和/支持时钟电源管理,那么这个信号就是必要的(即使你不是使用的CC模式)。

注意:如果硬件电路这个CLKREQ#没接的话,可让BIOS把PCIE中的ASPM的L1状态默认关闭,不然容易出现异常现象。

好了,今天分享就到这里,喜欢的三连,谢谢。

更多推荐

已为社区贡献8条内容

已为社区贡献8条内容

所有评论(0)