晶体(crystal、无源晶振)两端电容取值计算

数字电路中往往会需要一个时钟源,常用的比如晶体振荡器(oscillator、有源晶振)、晶体(crystal、无源晶振)等,一般晶体用的更多些。对于晶体来说,一般电路设计时会在晶体两端各接一个电容倒地,如下图所示:上面电路中晶体两端的电容是用来匹配晶体的负载电容(CL:Load Capacitance)的,如果负载电容无法满足的话一般会使晶体频率产生偏差,严重的话晶体无法起振。电路设计中要尽量..

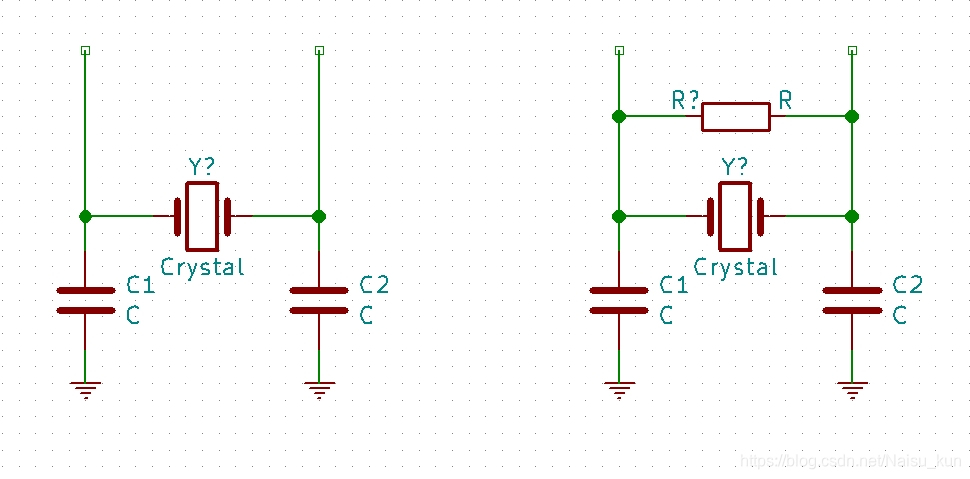

数字电路中往往会需要一个时钟源,常用的比如晶体振荡器(oscillator、有源晶振)、晶体(crystal、无源晶振)等,一般晶体用的更多些。对于晶体来说,一般电路设计时会在晶体两端各接一个电容到地,如下图所示:

上面电路中晶体两端的电容是用来匹配晶体的负载电容(CL:Load Capacitance)的,如果负载电容无法满足的话一般会使晶体频率产生偏差,严重的话晶体无法起振。电路设计中要尽量满足晶体的负载电容需求,从而使晶体工作在最佳状态。负载电容计算公式如下:

CL = C1*C2 / (C1+C2) + CS

CS为电路板的寄生电容,一般取 3~5pF,取C1 = C2,那么公式可以简化成如下:

CL = C1 / 2 + CS

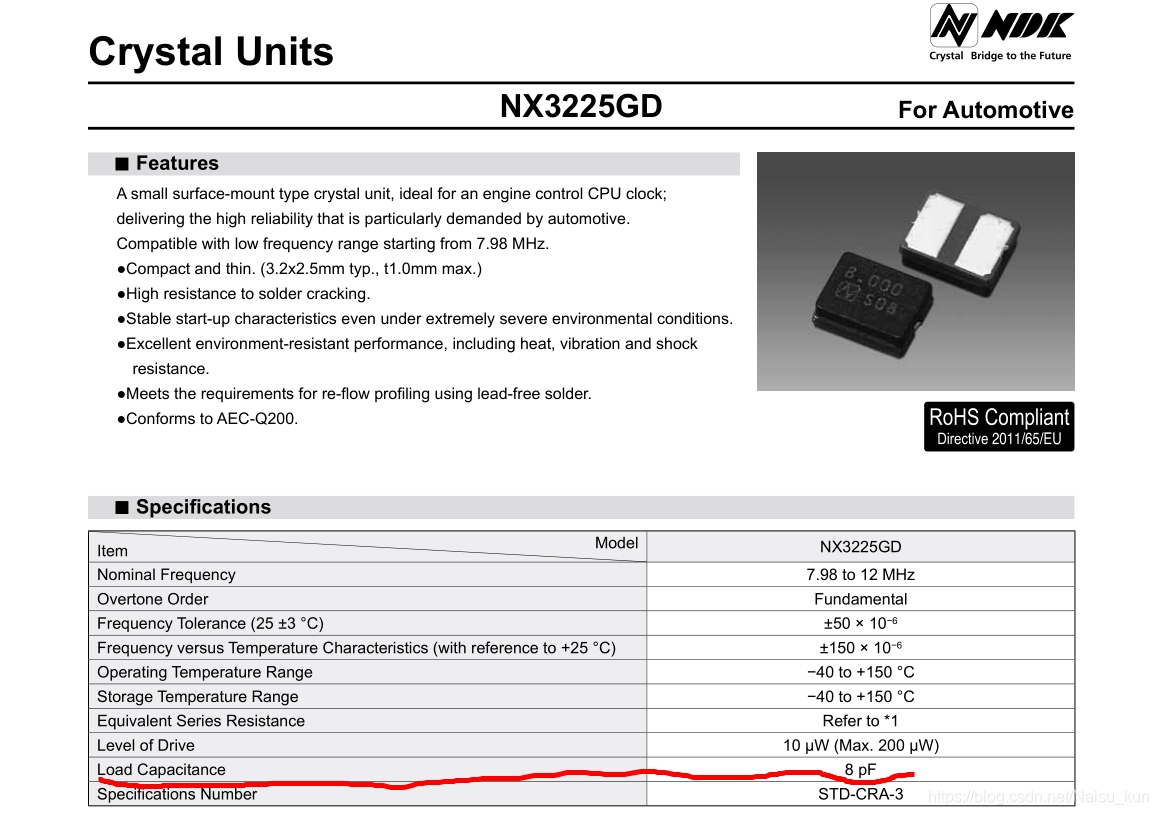

根据上面公式就可以快速计算晶体两端电容取值了,这里找一个晶体进行计算示范:

上面的是某晶体的手册,从手册上可以看到该晶体的负载电容是8pF,如果取CS = 3pF的话可以计算得到C1 = C2 = 10pF,如果取CS = 5pF的话可以计算得到C1 = C2 = 6pF,综合来说一般取个6~10pF都没问题,要是对频率要求比较严格的话需要通过示波器测试波形(一般的示波器探头自身带有几pF的寄生电容可能无法正确测量,有条件的话可以选用有源探头进行测量)。

更多推荐

已为社区贡献24条内容

已为社区贡献24条内容

所有评论(0)