斩波运放仿真教程(PSS+PAC)

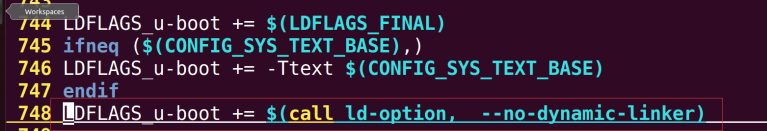

本文将以一个斩波运算放大器为例讲解pss+pac仿真过程由于斩波运放中涉及到斩波时钟,而在进行传统的AC仿真时,斩波的时钟频率不会发生跳转,或者说传统的AC仿真时,是不能带有时域上的时钟信号的,所以不能够仿真带有斩波频率的运放的性能参数;故如果要得到斩波运放的AC参数或者noise参数,需要进行PSS+PAC仿真、PSS+Pnoise仿真等;PSS仿真即周期稳定性仿真,用于仿真带有周期性信号的电路

斩波运放仿真教程(PSS+PAC)

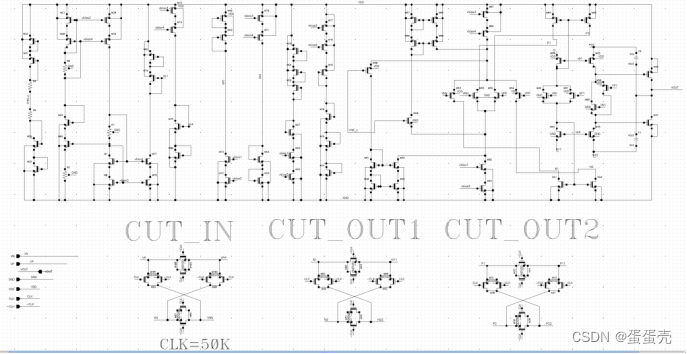

本文将以以下运放作为实例讲解斩波运放仿真(pss+pac):

由于斩波运放中涉及到斩波时钟,而在进行传统的AC仿真时,斩波的时钟频率不会发生跳转,或者说传统的AC仿真时,是不能带有时域上的时钟信号的,所以不能够仿真带有斩波频率的运放的性能参数;故如果要得到斩波运放的AC参数或者noise参数,需要进行PSS+PAC仿真、PSS+Pnoise仿真等;PSS仿真即周期稳定性仿真,用于仿真带有周期性信号的电路(个人理解),例如带有斩波器的运放(周期信号为斩波器时钟)、振荡器(振荡器稳定后的输出信号)等;如下图所示:

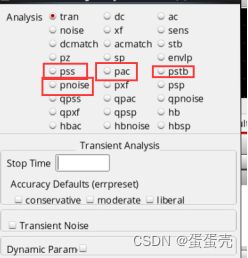

在进行PAC守或者PNOISE仿真之前,要进行一次PSS仿真,因为后面的pnoise等仿真是需要在PSS仿真的结果之上进行;故只有当你的电路在跑PSS仿真得到收敛的结果后才能进行后续仿真;

将上述电路打包成一个sample后进行仿真,首先进行PSS+PAC仿真,拓扑如下:

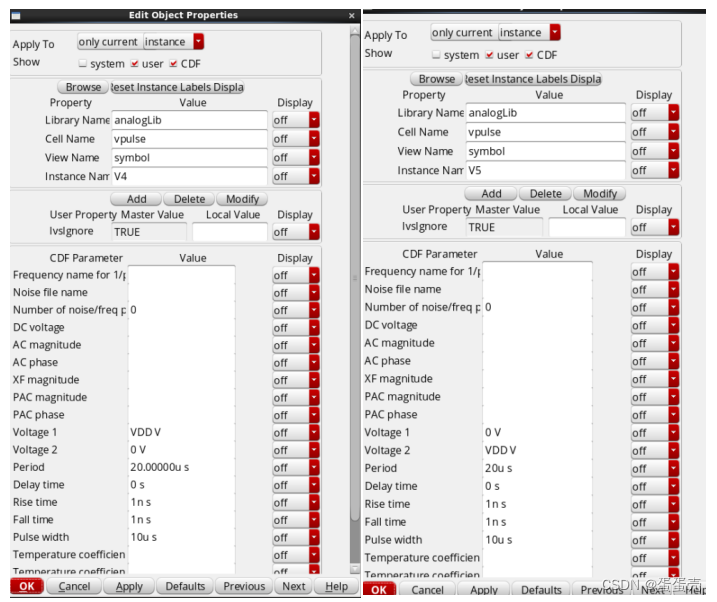

电压源V1用于提供共模电压(VDD/2),V2用于提供交流电压(1V),此时的交流电压源V2参数设置如下:

这里的斩波时钟为50K,故分别给clk和~clk给 50K的时钟信号,由vpluse产生:

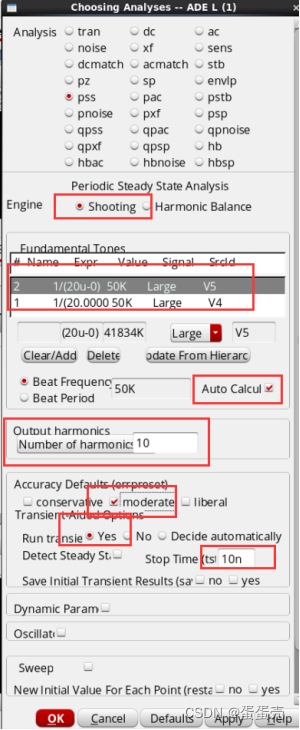

PSS设置

打开ADE,选择“pss”进行周期稳定性仿真,在“Beat Period”栏中输入与斩波时钟周期相同的周期值,由于时钟频率为50kHz,因此对应周期为“20u”(也可以勾选右边的Aut caclute,然后在上面选择电路的时钟源,自动计算 beat period)。在“Number of harmonics”栏中输入仿真的谐波数,如果取得过大会导致仿真速度降低,这里输入“10 ”;“Accuracy Defaults”项选择仿真最高精度“conservative”;在“tstab”中输入仿真稳定时间,这里可选得短一些,如“10n”(一般为时钟周期的10背左右),如下图所示:

PAC设置

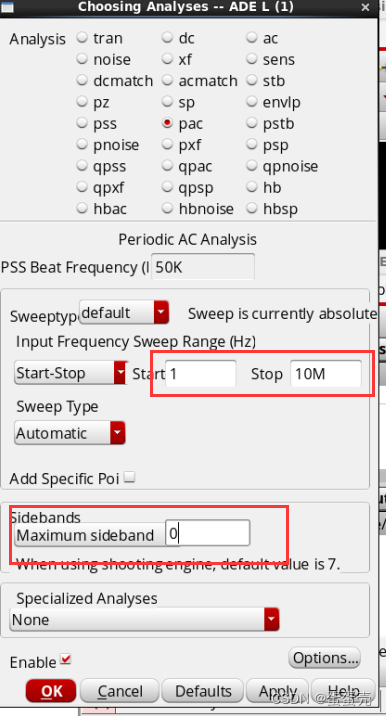

再添加“PAC”仿真,此时“PSS Beat Period(Hz)”中自动指向“pss”输入的时钟周期。在“Start”和“Stop”栏中分别输入pac扫描开始和结束的频率(这里设置1—10M),“Sweep Type"项选择默认的“Automatic",在“Maximum sideband”中输入要仿真的边带数,由于我们只关心基带的信号特性,所以边带值不必设置得很大,这里设置为“0”(大家可以更改这里的数值,看看输出的AC曲线有什么区别),如图下所示,单击“OK”按钮,完成设置。

仿真

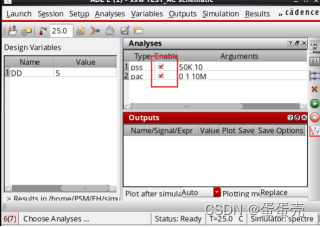

然后开始仿真,记得PSS和PAC同时勾选上:

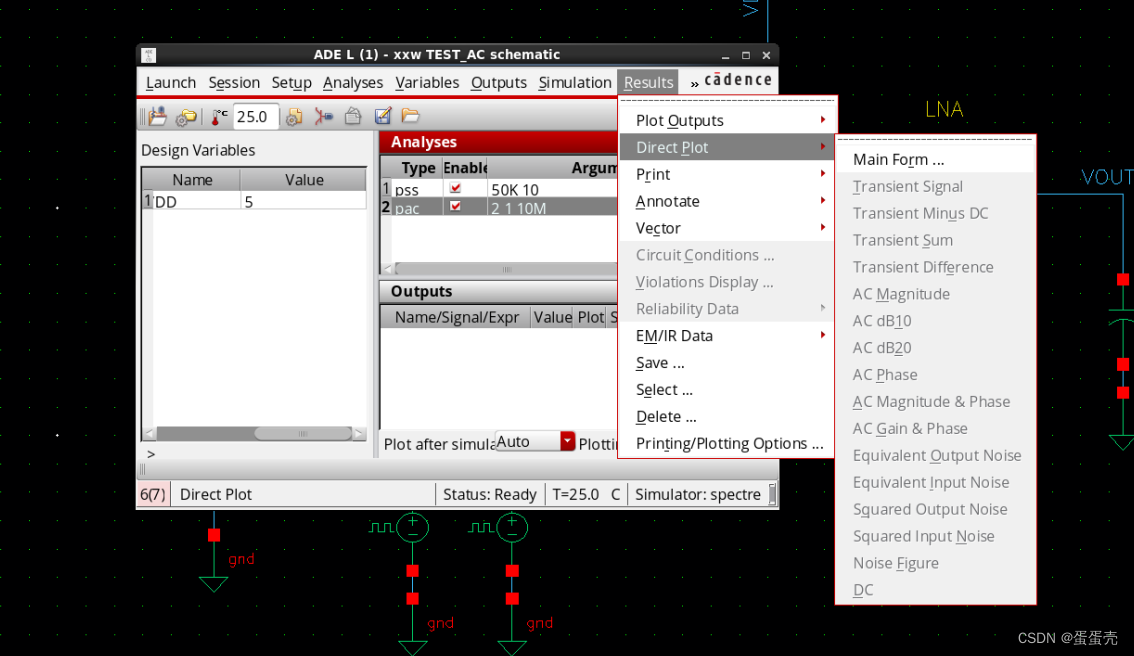

仿真完成后查看曲线:

选择PAC,然后点击输出端

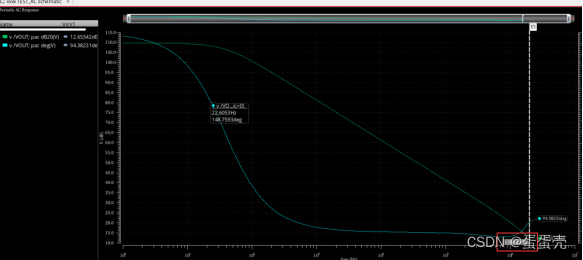

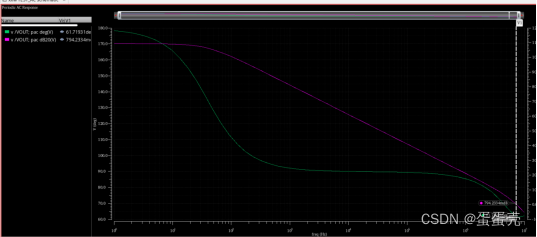

曲线如下,我们可以看到,我们设置的最大频率为10M,然而实际输出并未达到,这是因为PAC仿真是在PSS上进行的,PSS的频率扫描没有达到我们设置的10M;

我们可以在回到PSS的仿真设置,把PSS的最大扫面频率设置为10M,把PSS的参数设置页面拉到最后,点击option:

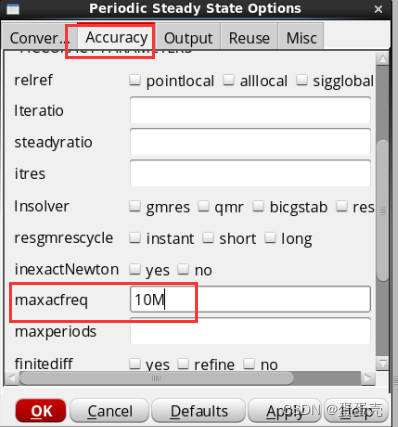

选择“Accuracy”,找到“maxacfreq”,在里面输入你所需要的频率,不宜过大,过大的话会降低仿真速度,设置完成后在重新仿真即可;

重新仿真后得到以下幅频曲线:

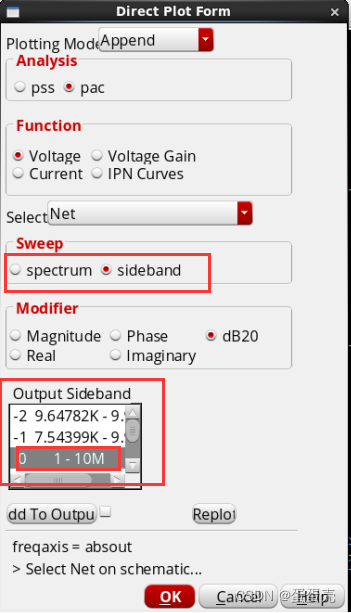

【注】如果在PAC设置的时候,“Maximum sideband”设置的不为0,在plot的时候可以在"SWEEP"里面选择"sideband",然后在“output sideband”里面选择基频,然后再plot。

后续将更新PSS+Pnoise,Pstb,斩波运放失调电压的仿真,以及无片外电容的简单LDO设计过程及仿真,由于临近考试周,将会在空时更新,如有错误欢迎批评指正。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)