zynq7系列DDR3的PCB走线阻抗与端接电阻问题

zynq7系列DDR3的PCB走线阻抗与端接电阻问题

zynq7020仅PS带有DDR端口,兼容DDR2到DDR3协议,PCB设计主要参考ug933手册。

本文主要讨论其走线阻抗与端接电阻问题。

1. 官方推荐电压-1.5V/1.35V

DDR3和DDR3L都同时支持1.5V和1.35V的I/O电压。

·············

············

2. 官方推荐走线阻抗–DDR3单端40,差分80

3. 官方推荐端接电阻–单端40,差分时钟80

4.正点原子开源的原理图–单端40.2,差分80.6

5.问题

如果完全按照官方参考来,应该没什么问题,但是实际走线阻抗多用50R,时钟差分也多用100R,一是更通用,二是阻抗更大在叠层设计时走线可以控制得更细、更合理,如一般板厂6层PCB的叠层结构下top计算50欧线宽大概5-6mil,如果40欧则外层来到8-9mil,内层线宽将更大,会让本就不富裕的空间雪上加霜。

那么走线50欧,端接电阻是多少,是按照直觉同步搞成50,还是按照官方推荐的40不变?

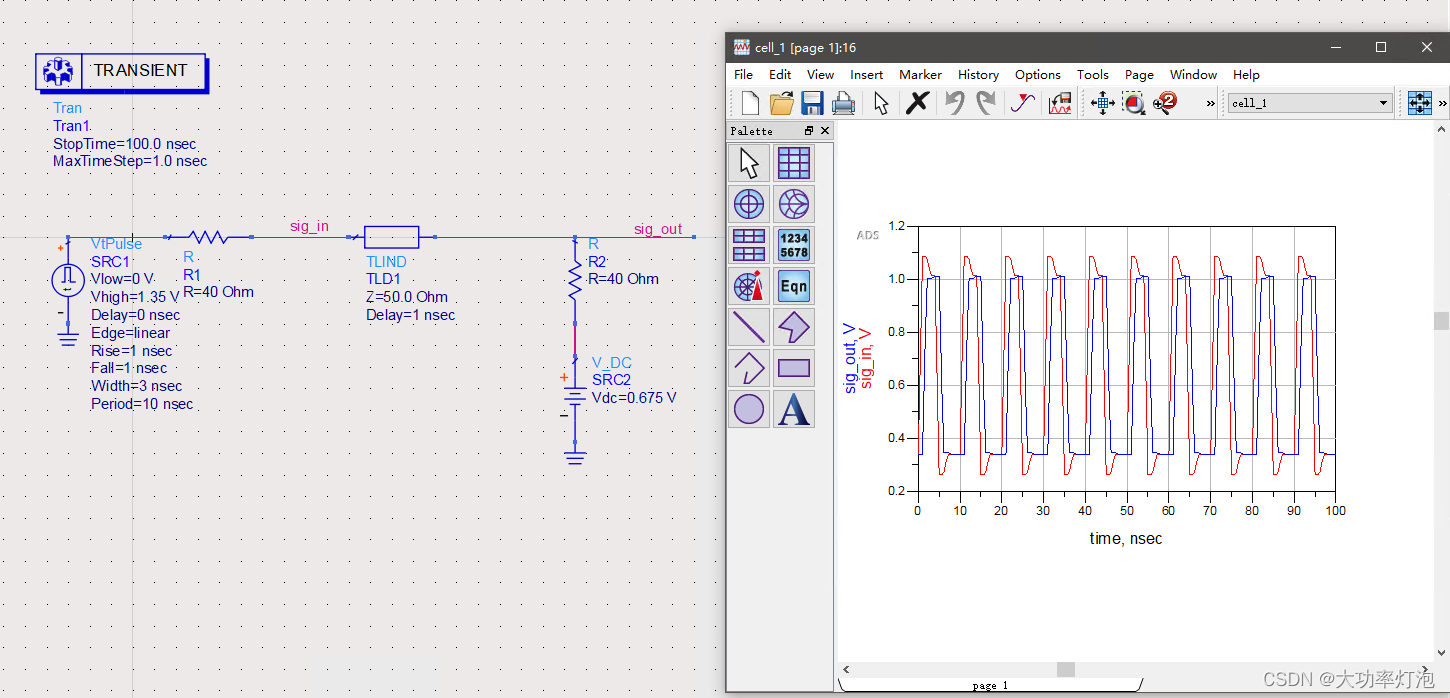

下面在ADS中简单仿真一下,

- 走线50,端接40

- 走线50,端接50

- 走线40,端接50

- 走线40,端接40

2和4波形是所想要的,说明端接电阻应该和走线阻抗匹配;

-

输出阻抗改成200,走线和端接均50

中心在0.68V附近,幅度大幅缩减,由于无法得知实际芯片的阻抗,故由此得知从官方推荐40改到50后的主要影响在于信号围绕中线的幅度有所变化。 -

去掉端接电阻

终端信号满幅度,但是源端回勾明显,说明终端电阻是必要的,但是对于DQ数据线DDR3是支持ODT的,也就不需要去加,但是时钟和地址是没有的需要额外加。

后续补充:地址线和命令线数据传输是单向的,即使反射回来的信号导致源端波形不理想,但是终端信号质量是可以接受的,所以不加终端匹配电阻似乎也说的过去,而数据线是双向的但是一般芯片自带可调节端接电阻。

6.上述是基于理想情况的,实际考虑到寄生电容等因素就不得而知了,也有说走线50,端接40是个经验值,否则就得做个整板的SI仿真。

7.DDR3相关电平标准

DDR相关标准由JEDEC组织定义

DDR3的IO电平采用SSTL

这是主控端的描述

DDR3芯片对电平的描述

!!!VIL 和VIH在参考电平VTT(1/2VDD)上下0.3V内

8 DDR走线时BGA区域规则引起的阻抗不匹配带来的影响

如上,BGA区域内走线比预计算出的走线要细很多,此处从5.7mil降到3.5mil,5.7mil宽走线长500mil,3.5mil线宽100mil左右;经过计算,5.7mil是匹配的50欧姆,3.5mil则是非预期的62欧;如下

通过搭建简单的模型,来简化分析一下这种不连续带来的影响,ADS模型采用如下所示:

仿真输出结果如下:

不算好,但是还行,没有回勾,也都越过了VIL和VIH;

作为对比,取消3.5mil的线宽,全部换成5.7mil的匹配线宽,结果好像是差不多的;

9 allegro 中拓扑的设置

T拓扑设置:这两个都不错。

https://www.bilibili.com/video/av668030087

https://www.zhihu.com/zvideo/1319993178591326208

这个是设置T点的最佳教程,关键是SigExplorer中建立两条同名但不同路径的规则

https://www.bilibili.com/video/av548715209/

Fly-by,参考十四的教程

https://study.163.com/course/courseLearn.htm?courseId=1005839006#/learn/video?lessonId=1053480248&courseId=1005839006

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)